# AN ANALYTICAL MODEL DESCRIBING THE PERFORMANCE OF APPLICATION-SPECIFIC NETWORKS-ON-CHIP ON FIELD-PROGRAMMABLE GATE ARRAYS

by

Jason Shek-Yen Lee

B.A.Sc, Simon Fraser University, 2007

Thesis submitted in partial fulfillment of the requirements for the degree of Master of Applied Science in the School

of

Engineering Science

© Jason Shek-Yen Lee 2010 SIMON FRASER UNIVERSITY Spring 2010

All rights reserved. However, in accordance with the Copyright Act of Canada this work may be reproduced, without authorization, under the conditions for Fair Dealing. Therefore, limited reproduction of this work for the purposes of private study, research, criticism, review and news reporting is likely to be in accordance with the law, particularly if cited appropriately.

## APPROVAL

| Name:                | Jason Shek-Yen Lee                                                                                                           |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|

| Degree:              | Master of Applied Science                                                                                                    |

| Title of Thesis:     | An Analytical Model Describing the Performance of Application<br>Specific Networks-on-Chip on Field-Programmable Gate Arrays |

| Examining Committee: |                                                                                                                              |

| Chair:               |                                                                                                                              |

|                      | Dr. John Bird                                                                                                                |

|                      | Professor, School of Engineering Science                                                                                     |

|                      | Dr. Lesley Shannon                                                                                                           |

|                      | Senior Supervisor                                                                                                            |

|                      | Assistant Professor, School of Engineering Science                                                                           |

|                      | Dr. Rick Hobson                                                                                                              |

|                      | Supervisor                                                                                                                   |

|                      | Professor, School of Engineering Science                                                                                     |

|                      | Dr. Rodney Vaughan                                                                                                           |

|                      | Internal Examiner                                                                                                            |

|                      | Professor, School of Engineering Science                                                                                     |

Date Approved/Defended: January 14, 2010

## Declaration of Partial Copyright Licence

The author, whose copyright is declared on the title page of this work, has granted to Simon Fraser University the right to lend this thesis, project or extended essay to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its users.

The author has further granted permission to Simon Fraser University to keep or make a digital copy for use in its circulating collection (currently available to the public at the "Institutional Repository" link of the SFU Library website <www.lib.sfu.ca> at: <a href="http://ir.lib.sfu.ca/handle/1892/112>">http://ir.lib.sfu.ca/handle/1892/112></a>) and, without changing the content, to translate the thesis/project or extended essays, if technically possible, to any medium or format for the purpose of preservation of the digital work.

The author has further agreed that permission for multiple copying of this work for scholarly purposes may be granted by either the author or the Dean of Graduate Studies.

It is understood that copying or publication of this work for financial gain shall not be allowed without the author's written permission.

Permission for public performance, or limited permission for private scholarly use, of any multimedia materials forming part of this work, may have been granted by the author. This information may be found on the separately catalogued multimedia material and in the signed Partial Copyright Licence.

While licensing SFU to permit the above uses, the author retains copyright in the thesis, project or extended essays, including the right to change the work for subsequent purposes, including editing and publishing the work in whole or in part, and licensing other parties, as the author may desire.

The original Partial Copyright Licence attesting to these terms, and signed by this author, may be found in the original bound copy of this work, retained in the Simon Fraser University Archive.

Simon Fraser University Library Burnaby, BC, Canada Abstract

Modern Field-Programmable Gate Arrays (FPGAs) are now used to implement complex

Systems-on-Chip (SoCs) and more recently Networks-on-Chip (NoCs). NoCs consist of

computing nodes that are connected via switches or routers to a network of point-to-point

links, which define its topology. Appropriate topology choices for Application-Specific Inte-

grated Circuits (ASICs) have been investigated, but due to an FPGA's fixed interconnect

fabric, these conclusions are not necessarily applicable. Our research investigates how a

commercial FPGA's fixed interconnect and CAD flow constrain the performance of NoCs

based on a set of design parameters. We develop an analytical model that predicts the

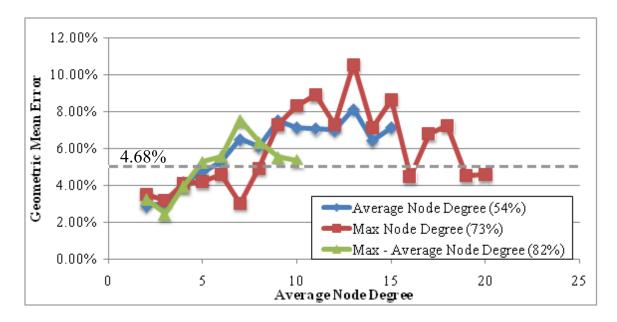

performance for both homogeneous and heterogeneous NoCs with a geometric mean error

of 4.68% for Xilinx Virtex 2 Pro, Virtex 4, Virtex 5, and Virtex 6 FPGAs, and with a

geometric mean error of 5.12% for Altera Stratix III and Stratix IV FPGAs.

Keywords: Networks-on-Chip; NoCs; FPGAs; Analytical Model; Systems-on-Chip; SoCs;

Performance; Topologies; Routability; Application-Specific; Homogeneous; Heterogeneous

iii

## Acknowledgments

While I was told to try to keep this section short, I cannot go without acknowledging the many people that have helped me in the past few years. First, I would like to thank my family for supporting me and dealing with my extended absences from home. I am especially thankful for my mom who never took an eye off of me and is always watching over me night and day. It is the best feeling in the world to always have a loving home to come back to whenever your research hits a wall...

To my endearing girlfriend Sami, thank you for listening to my complaints, dealing with my stress, and always having an opinion on what needs to be done. You were always there to put a smile on my face and I don't think I could have done it without your support. I love you!

To the friends I have made through university, I know that you will be my life long friends. We will hopefully continue to have parties at Cho's, bet on when Eric will graduate, and wonder if Jeff is asleep or awake. Thanks to Jamie who had many Indian lunches with me. I am determined to beat you in squash one day. To Danny H., who is always there for a helping hand and an intermittent round of golf. I am forever grateful that I have friends like you guys.

To my two awesome dogs, Bailey the Haveanese and Boomer the Chow cross Lab. You are my best companions and your unquestionable love cannot be thanked enough. Although you won't be able to read this, I promise I'll reward you with a fist full of dog treats.

I would also like to thank all my lab-mates for their support and humorous conversations. Jian, you helped me deal with so many problems when you already had a stack of them on your own, and I am in your debt. Ed, you helped me with all the little things, and although you might not realize it, I am very grateful for all the work you did. Dave, thanks for all the help you provided and the numerous projects that we have done. I will always be able to look to you when I want to get lost in a foreign country.

Last but not least, I would like to thank my supervisor, Dr. Lesley Shannon. I realize that this section might be too colloquial to your taste, but your attention to detail has allowed me to foster many skills that I lost in my early years of university. I have learned a great deal in my graduate studies, and a lot of it is because of you.

I would also like to acknowledge the financial support, as well as the equipment and software donations, that I have received from the following organizations that have made the research possible: the Canadian Microelectronics Corporation, the Natural Sciences and Engineering Research Council, Simon Fraser University, Xilinx, and Altera.

# Contents

| $\mathbf{A}_{]}$ | ppro  | val                    | ii  |

|------------------|-------|------------------------|-----|

| $\mathbf{A}$     | bstra | $\operatorname{ct}$    | iii |

| $\mathbf{A}$     | cknov | wledgments             | iv  |

| C                | onter | nts                    | vi  |

| Li               | st of | Figures                | iii |

| Li               | st of | Tables                 | x   |

| $\mathbf{G}$     | lossa | $\mathbf{r}\mathbf{y}$ | xii |

| 1                | Intr  | roduction              | 1   |

|                  | 1.1   | Motivation             | 2   |

|                  | 1.2   | Objective              | 3   |

|                  | 1.3   | Contributions          | 3   |

|                  | 1.4   | Thesis Organization    | 4   |

| $\mathbf{G}$     | lossa | ry                     | 1   |

| 2                | Bac   | kground                | 5   |

|                  | 2.1   | Terminology            | 5   |

|   | 2.2 | Related Work                              | 7                |

|---|-----|-------------------------------------------|------------------|

|   |     | 2.2.1 Network Architecture                | 7                |

|   |     | 2.2.2 Architectural Changes               | 9                |

|   |     | 2.2.3 CAD Tool Flows                      | 1                |

|   |     | 2.2.4 Previous Analytical Model Work      | 2                |

|   |     | 2.2.5 Analytical Models for NoCs          | .3               |

| 3 | Exp | periment Methodology 1                    | .5               |

|   | 3.1 | Network Nodes                             | 6                |

|   |     | 3.1.1 Computing Node                      | 6                |

|   |     | 3.1.2 Network Interface                   | 20               |

|   | 3.2 | Custom Tool Flow                          | 22               |

|   | 3.3 | Testing Methodology                       | 24               |

| 4 | Der | iving an Analytical Framework for NoCs 2  | 28               |

|   | 4.1 | Previous Research                         | 30               |

|   | 4.2 | Chip Independence                         | 31               |

|   | 4.3 | Resource Usage                            | 33               |

|   | 4.4 | Number of Nodes and Node Sizes            | 36               |

|   | 4.5 | Local Routing Demand                      | 11               |

|   |     | 4.5.1 The Star Topology                   | 12               |

|   |     | 4.5.2 Link Width                          | 16               |

|   |     | 4.5.3 Bandwidth                           | 18               |

|   | 4.6 | Global Routing Demand                     | 50               |

|   |     |                                           |                  |

|   | 4.7 | Regularity                                | 55               |

| 5 |     |                                           | 55<br>5 <b>7</b> |

| 5 |     | alytical Model 5                          |                  |

| 5 | Ana | Alytical Model 5  Xilinx Analytical Model | 7                |

|    | 5.2   | Altera Analytical Model                                      | 3 |

|----|-------|--------------------------------------------------------------|---|

|    |       | 5.2.1 Local Routing Demand                                   | 3 |

|    |       | 5.2.2 Global Routing Demand                                  | 4 |

|    | 5.3   | Summary                                                      | 6 |

| 6  | Veri  | ification 6                                                  | 9 |

|    | 6.1   | Xilinx Verification                                          | 9 |

|    | 6.2   | Altera Verification                                          | 4 |

|    | 6.3   | PlanAhead - Manual Placement of NoC Topologies               | 7 |

| 7  | Con   | clusion 8-                                                   | 4 |

|    | 7.1   | Future Work                                                  | 5 |

| Bi | bliog | raphy 8                                                      | 7 |

| A  | Top   | ology Generator 92                                           | 2 |

|    | A.1   | Main Function (main.c)                                       | 2 |

|    | A.2   | Global Variables (globals.c)                                 | 1 |

| В  | Syst  | tem Generator 113                                            | 3 |

|    | B.1   | Main (main.c)                                                | 9 |

|    | B.2   | Global Variables (globals.c)                                 | 2 |

|    | B.3   | Generate Multiplier PCORE (generate_mult.c)                  | 4 |

|    | B.4   | Generate Switch PCORE (generate_switch.c)                    | 4 |

|    | B.5   | Generate Xilinx *.xmp file (generate_xmp.c)                  | 9 |

|    | B.6   | Generate Xilinx *.mhs file (generate_mhs.c)                  | 1 |

|    | B.7   | Generate Xilinx *.mss file (generate_mss.c)                  | 0 |

|    | B.8   | Generate Xilinx *.opt file (generate_opt.c)                  | 4 |

|    | B.9   | Generate Xilinx *.ucf file (generate_ucf.c)                  | 7 |

|    | B.10  | Generate FSL for Altera FPGAs (generate_fsl.c)               | 9 |

|    | B 11  | Generate System Wrapper for Altera FPGAs (generate system.c) | 2 |

# List of Figures

| 2.1  | Network topologies                                                           | 6  |

|------|------------------------------------------------------------------------------|----|

| 3.1  | Network node                                                                 | 15 |

| 3.2  | MicroBlaze computing node                                                    | 16 |

| 3.3  | Multiplier computing node                                                    | 16 |

| 3.4  | Multiplier architecture                                                      | 17 |

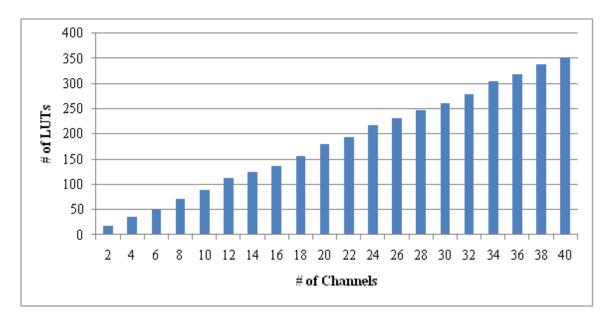

| 3.5  | Network interface resource utilization                                       | 20 |

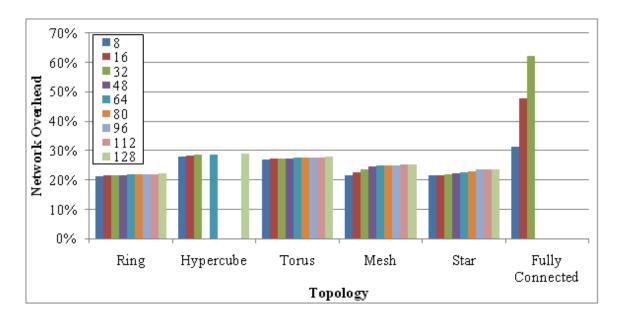

| 3.6  | Network overhead on Xilinx Virtex 5 LX330                                    | 21 |

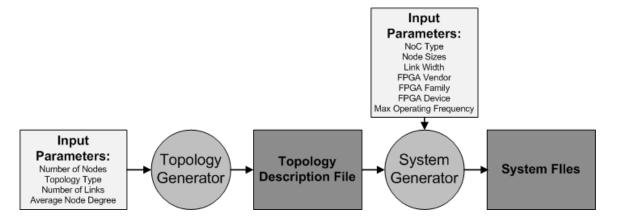

| 3.7  | Custom tool flow                                                             | 23 |

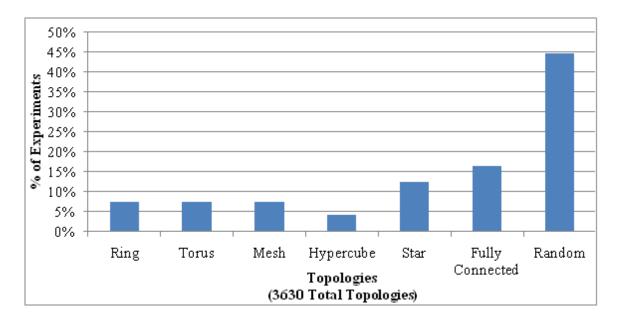

| 3.8  | Distribution of experiments for each topology                                | 25 |

| 4.1  | Ring topology on Xilinx FPGAs                                                | 32 |

| 4.2  | Ring topology on Altera FPGAs                                                | 32 |

| 4.3  | Logic utilization of NoC topologies on Xilinx Virtex 5 LX330                 | 34 |

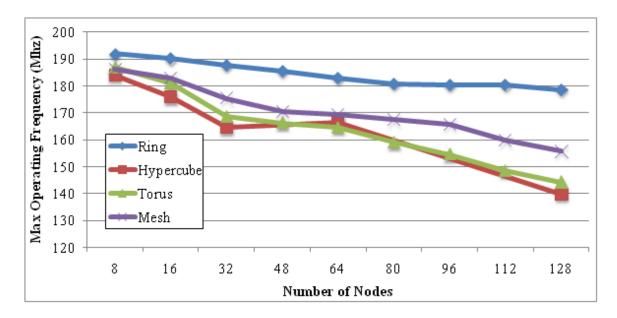

| 4.4  | Xilinx Virtex 5 LX330 performance for all topologies                         | 35 |

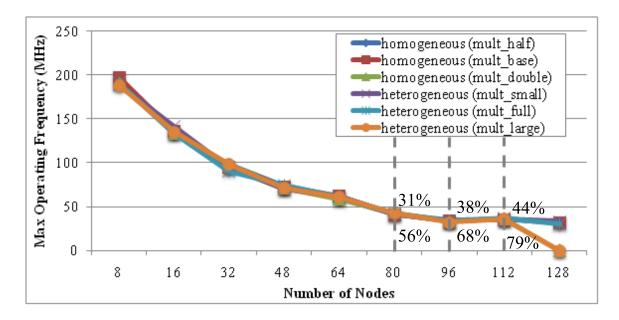

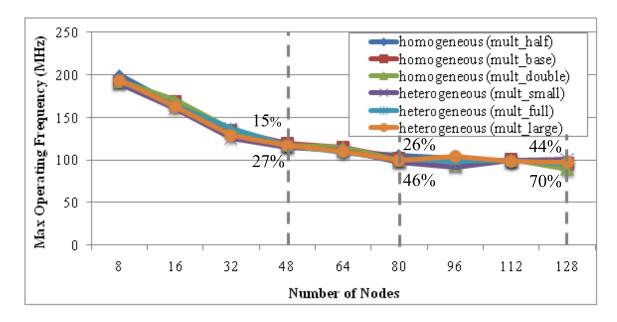

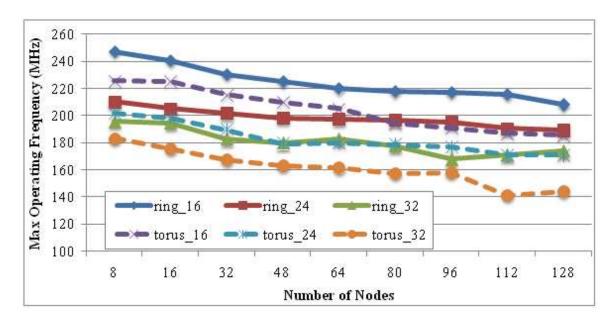

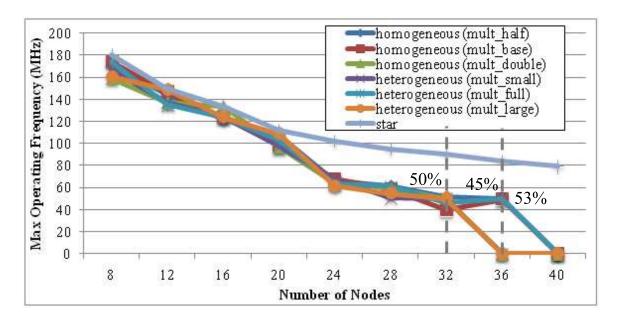

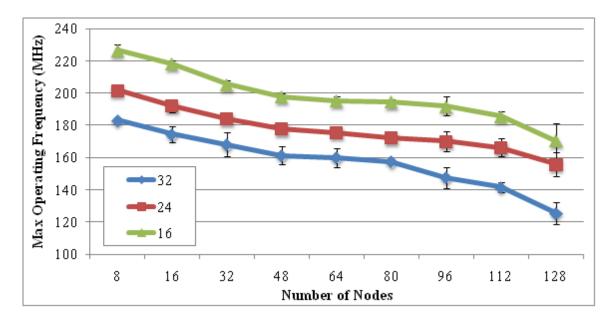

| 4.5  | Xilinx Virtex 5 LX330 performance for homogeneous topologies                 | 37 |

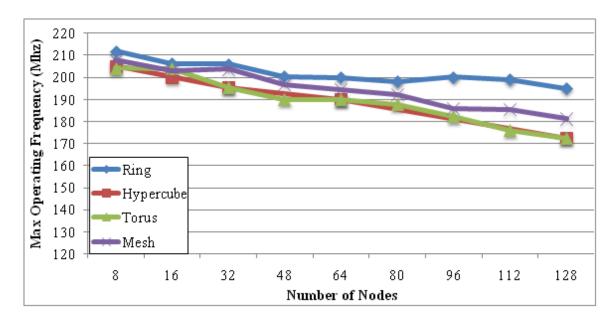

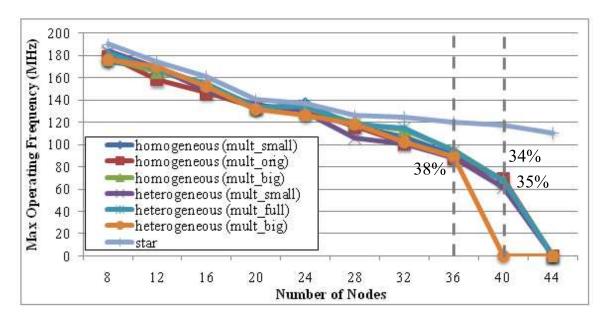

| 4.6  | Altera Stratix III 340 performance for homogeneous topologies                | 38 |

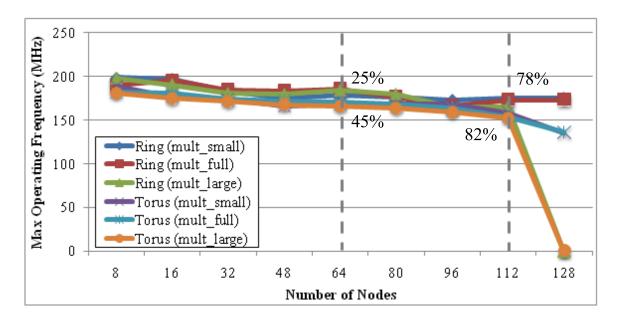

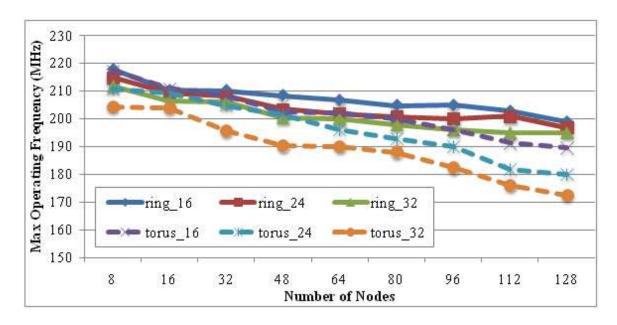

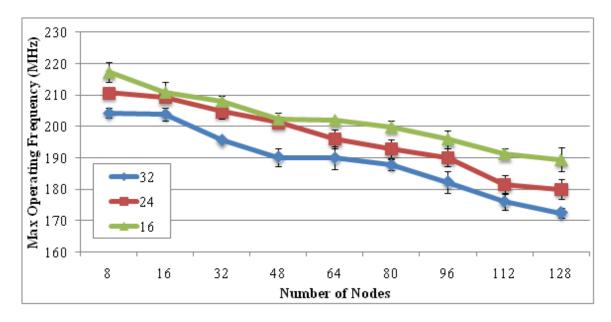

| 4.7  | Xilinx Virtex 5 LX330 performance for heterogeneous topologies $\dots \dots$ | 39 |

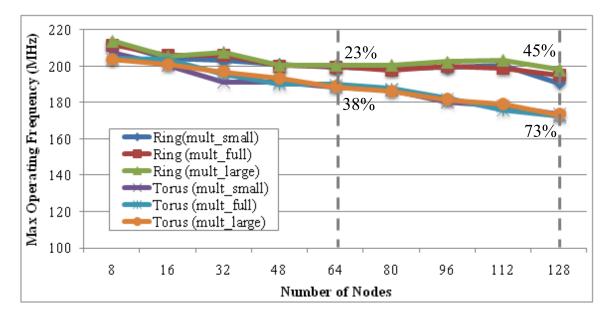

| 4.8  | Altera Stratix III 340 performance for heterogeneous topologies              | 39 |

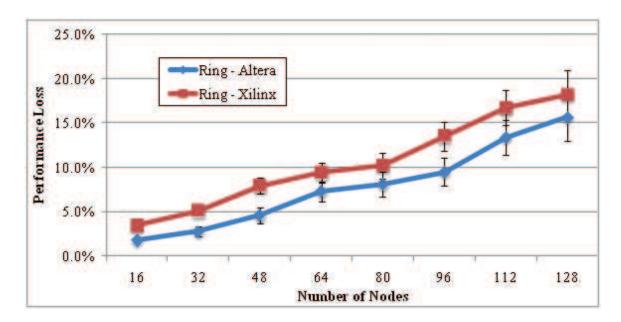

| 4.9  | Performance loss due to change in number of nodes for a ring topology        | 41 |

| 4.10 | Star topology performance on Xilinx Virtex 5 LX330                           | 42 |

| 4.11 | Star topology performance on Altera Stratix III 340                          | 43 |

| 4.12 | Network interface of 32-node star topology on Xilinx Virtex 5 LX330                                     | 44 |

|------|---------------------------------------------------------------------------------------------------------|----|

| 4.13 | Network interface of 64-node star topology on Xilinx Virtex 5 LX330                                     | 45 |

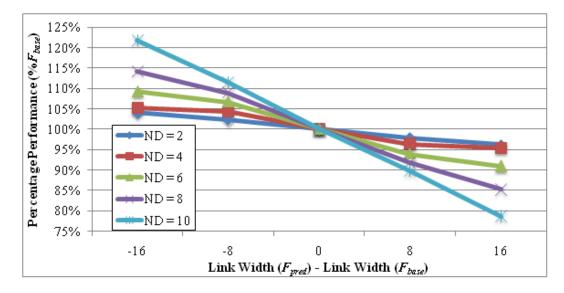

| 4.14 | Varying link widths on Xilinx Virtex 5 LX330                                                            | 47 |

| 4.15 | Varying link widths on Altera Stratix III 340                                                           | 47 |

| 4.16 | Bandwidth analysis for ring and torus topologies                                                        | 50 |

| 4.17 | Fully connected topologies on Xilinx Virtex 5 LX330 $\dots$                                             | 51 |

| 4.18 | Fully connected topologies on Altera Stratix III 340 $$                                                 | 51 |

| 4.19 | Heterogeneous random topologies on Xilinx Virtex 5 LX330 $\dots$                                        | 53 |

| 4.20 | Heterogeneous random topologies on Altera Stratix III 340 $\ \ldots \ \ldots \ \ldots$                  | 54 |

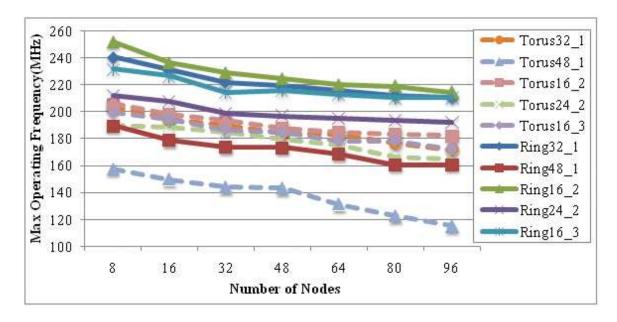

| 4.21 | Performance of torus topology and random topologies on Xilinx Virtex 5                                  |    |

|      | LX330 $(AND = 4)$                                                                                       | 55 |

| 4.22 | Performance of torus topology and random topologies on Altera Stratix III                               |    |

|      | $340 \; (AND = 4) \; \dots \; $ | 56 |

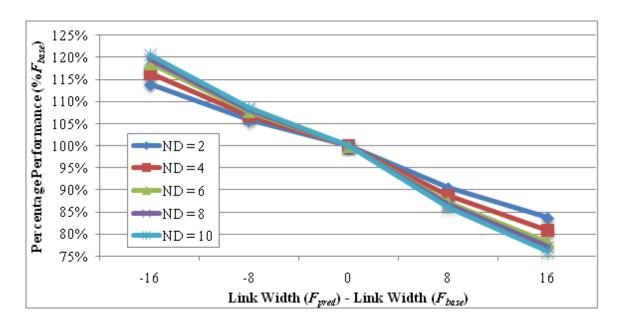

| 5.1  | Performance variation due to a change in link width for Xilinx FPGAs                                    | 59 |

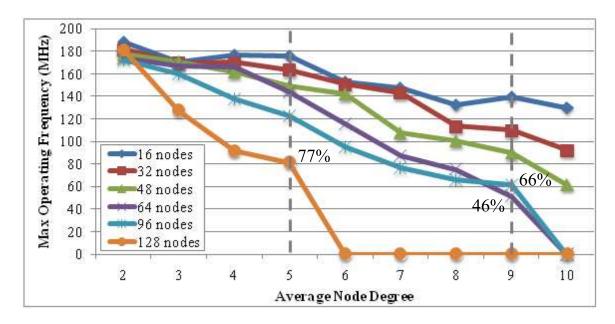

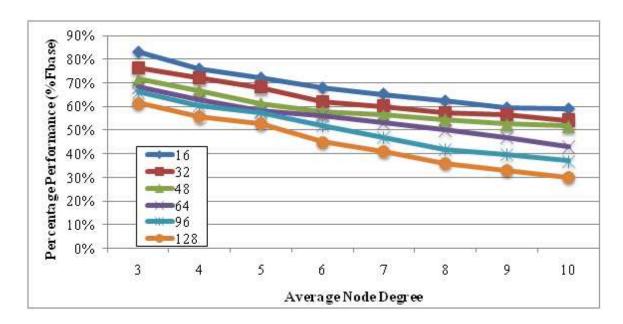

| 5.2  | Performance loss due to average node degree for Xilinx FPGAs $\ \ldots \ \ldots$                        | 61 |

| 5.3  | Performance variation due to a change in link width for Altera FPGAs                                    | 64 |

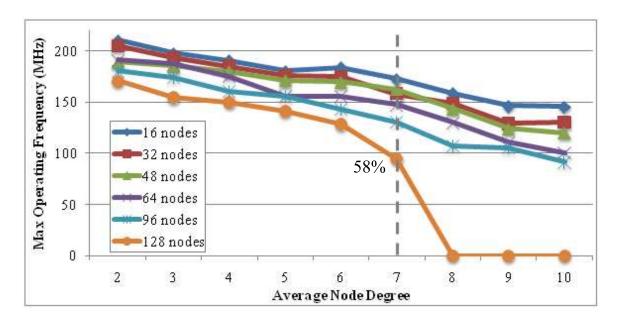

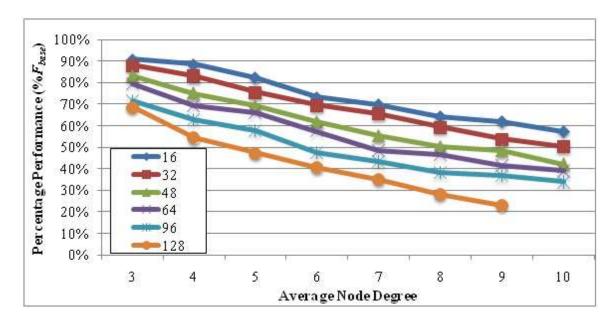

| 5.4  | Performance loss due to average node degree for Altera FPGAs                                            | 65 |

| 6.1  | Geometric mean error as a function of node degree for Xilinx FPGAs                                      | 70 |

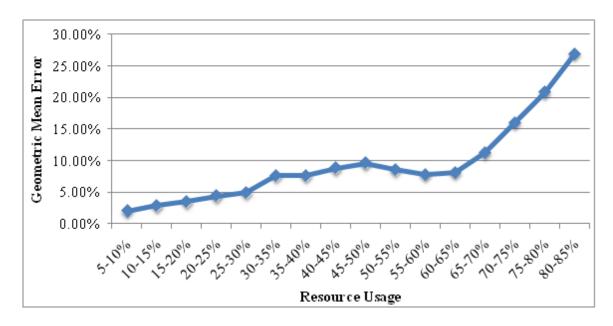

| 6.2  | Geometric mean error as a function of resource usage for Xilinx FPGAs $$                                | 74 |

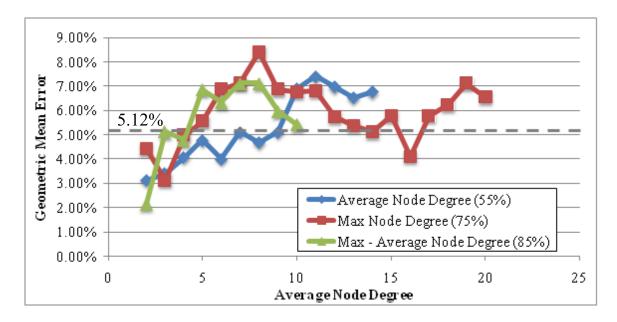

| 6.3  | Geometric mean error as a function of node degree for Altera FPGAs $$                                   | 75 |

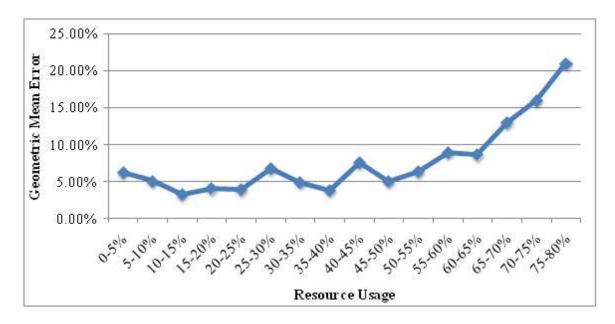

| 6.4  | Geometric mean error as a function of resource usage for Altera FPGAs $$                                | 77 |

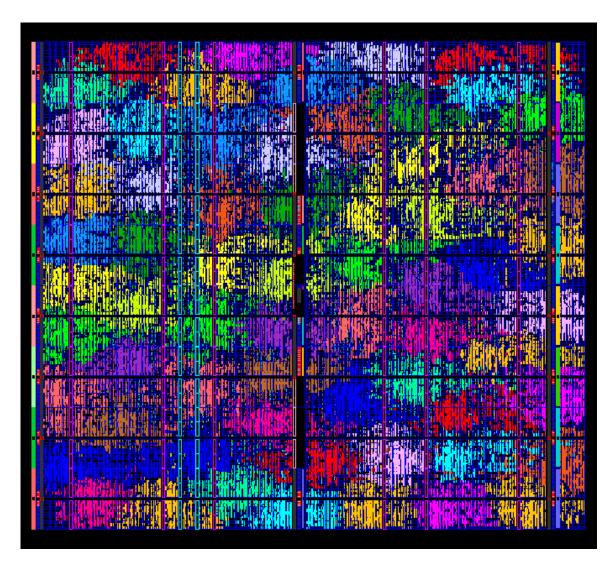

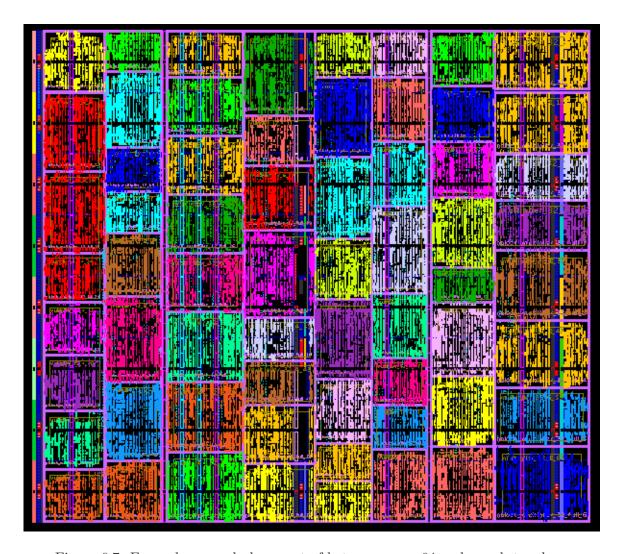

| 6.5  | Example automatic placement of homogeneous 64-node mesh topology                                        | 79 |

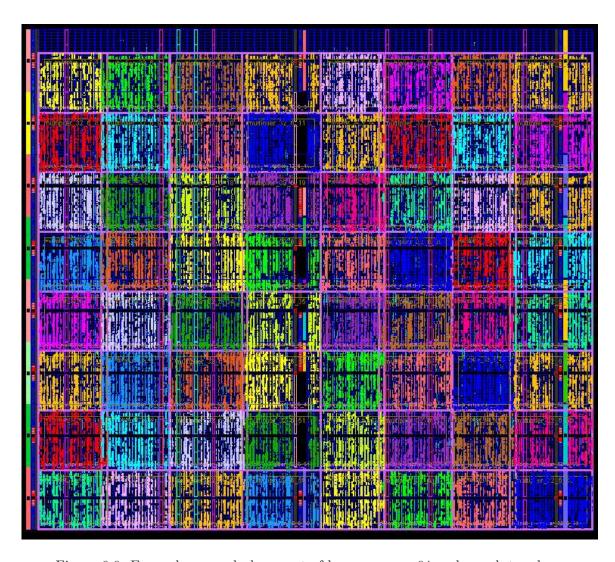

| 6.6  | Example manual placement of homogeneous 64-node mesh topology                                           | 80 |

| 6.7  | Example manual placement of heterogeneous 64-node mesh topology                                         | 82 |

# List of Tables

| 2.1 | Network topology characteristics                                       | (  |

|-----|------------------------------------------------------------------------|----|

| 3.1 | Homogeneous multiplier node types                                      | 18 |

| 3.2 | Heterogeneous multiplier node types                                    | 19 |

| 3.3 | FPGA family and devices                                                | 26 |

| 4.1 | Performance variation for FPGA devices and families                    | 33 |

| 4.2 | Percentage resource usage of largest NoC system for Xilinx FPGAs       | 35 |

| 4.3 | Percentage resource usage of largest NoC system for Altera FPGAs       | 36 |

| 4.4 | Percent resource usage for 128-node topologies                         | 38 |

| 5.1 | Base frequencies for training experiments                              | 67 |

| 6.1 | Predicted operating frequencies for Xilinx Virtex 4 and Virtex 5 FPGAs | 71 |

| 6.2 | Predicted operating frequencies for Xilinx Virtex 6 FPGA               | 72 |

| 6.3 | Predicted operating frequencies for Altera FPGAs                       | 76 |

| 6.4 | Homogeneous MultBase topologies with manual placement                  | 81 |

| 6.5 | Heterogeneous MultBase topologies with manual placement                | 81 |

## Glossary

- AND Average Node Degree

- ASIC Application-Specific Integrated Circuits

- CAD Computer-Aided Design

- CLB Configurable Logic Block

- CU Communication Unit

- EDK Embedded Development Kit

- $F_{base}$  Base Frequency

- $F_{pred}$  Predicted Frequency

- FF Flip Flop

- FIFO First-In-First-Out

- FPGA Field-Programmable Gate Array

- FSL Fast Simplex Link

- GRD Global Routing Demand

- INT intercept

- IP Intellectual Property

- ISE Integrated Software Environment

- ISP Internet Service Provider

- $k_{GRD}$  Global Routing Demand Factor

- $k_{LRD}$  Local Routing Demand Factor

- LRD Local Routing Demand

- LUT Look-Up Table

LW - Link Width

N - Number of Nodes

ND - Node Degree

${\operatorname{NoC}}$  -  ${\operatorname{Networks-on-Chip}}$

P2P - Point-to-Point

RPM - Relatively Placed Module

RU - Resource Usage

SL - Slope

$\operatorname{SoC}$  -  $\operatorname{Systems-on-Chip}$

TDM - Time Division Multiplexing

WOT - Weighted Order Toggling

## Chapter 1

## Introduction

Computer networks allow various computing elements to communicate and share resources, wherein the network provides the connectivity between the different elements. Networks provide many levels of abstraction, ranging from local area networks (LANs) with a few processing elements to the world wide web's (WWW) millions of processing elements. The same communication infrastructure can be applied to any system with multiple elements. On a much smaller scale, networks are becoming increasingly attractive for use on Systems-On-Chip (SoC) design, where multiple computing elements are implemented on the same die.

As chip densities improve, Field-Programmable Gate Arrays (FPGAs) are being increasingly used to implement complex SoCs [47]. Due to the lesser logic densities of previous generations, the complexity of SoC implementations on FPGAs has been limited to a small number of computing elements. Therefore, a shared bus such as AMBA [40], CoreConnect [45], and WISHBONE [49] could be used as the communication infrastructure between multiple master and slave nodes. While appropriate for smaller systems [1], shared busses do not scale well for more complex systems. As system complexity increases, the number of possible masters and slaves on a given bus leads to increased bus contention, slowing down data transfer and limiting bandwidth. Thus, more complex communication structures, such

as networks, are becoming increasingly attractive for Network-On-Chip (NoC) implementations. NoCs attempt to provide a solution to the growing complexity of SoCs by providing a highly customizable and scalable interconnect [6][35].

## 1.1 Motivation

When choosing an appropriate network topology for an application, multiple design factors need to be considered. Since each application is unique, there exists a problem of picking a desirable network from a large design space. For example, the NoC topology plays a role in the throughput, bandwidth, and latency of the entire systems. For systems designed on Application-Specific Integrated Circuits (ASICs), appropriate topology choices have been investigated [2][48]. Popular choices for ASICs are the mesh and torus topologies [35][14]. These topologies map well to an ASIC's two-dimensional implementation platform, providing control over the network's electrical characteristics. More complex topologies, such as the star and hypercube topologies, are generally not used on ASICs as they lead to increased chip area and an increasingly difficult routing task as the number of nodes grows.

While these conclusions may be true for ASICs, they do not necessarily hold for FPGAs. For ASICs, the structure and interconnect is completely defined by the designers and only the wires pertaining to the NoC are used and routed. In contrast, modern FPGAs are over-provisioned with routing; that is, FPGA architects provide significantly more routing than is needed for the "common case" to ensure a high fitting rate by the Computer Aided Design (CAD) tools for customer designs. Preliminary work by Shannon et al. showed that due to this over-provisioning, more complex topologies such as the star and hypercube are possible [51]. In fact, it suggested that in some cases these types of networks may be preferable to a mesh, since they have better network latency and bandwidth characteristics, yet can still be implemented easily on a modern FPGA. This result implies that designers have the increased freedom to select more complex topologies when implementing NoCs on FPGAs as opposed to ASICs. However, to leverage these findings, a more concrete understanding of the performance of various network topologies implemented on the fixed

prefabricated routing of an FPGA is required.

## 1.2 Objective

While there has been research investigating the use of FPGAs for NoCs [9], little has been done to characterize the routability and performance of NoC architectures on FPGAs. Given a specific platform and network characteristics, the objective of this work is to quantify and develop an analytical model describing the routability and performance characteristics for both homogeneous and heterogeneous NoCs on a variety of FPGA devices. Various network topologies, using both homogeneous and heterogeneous nodes are investigated to quantify how specific NoC design parameters affect routability and performance in terms of maximum operating frequency.

## 1.3 Contributions

Our research provides a thorough analysis of the performance of FPGA-based NoCs. The contributions of this work is as follows:

- 1. An investigation into the effects of different NoC parameters (Resource Usage, Number of Nodes, Average Node Degree, Link Width, Heterogeneity) on system performance.

- 2. Development of an analytical model describing the maximum operating frequency of an NoC that encapsulates the effects of the CAD tools and network topology for both Xilinx and Altera FPGAs.

- 3. A preliminary investigation into using relatively placed modules (RPMs) to demonstrate if improvements in performance can be attained using this form of guided placement as opposed to purely "automatic" placement.

These contributions are important for two reasons. Firstly, it quantifies the effects of specific network parameters on performance, and thereby the suitability of network topologies for implementation on an FPGA. This is an important first step to understanding the

flexibility and limitations of mapping application-specific network topologies to an FPGA's prefabricated routing interconnect using its commercial tool flow. Secondly, it provides guidance to a designer during early design space exploration, when a suitable network topology is being chosen.

## 1.4 Thesis Organization

This thesis is divided into 7 chapters. Chapter 2 discusses associated terminology and previous work related to our investigation of the implementation of NoCs on FPGAs. Chapter 3 describes the experimental methodology used in the investigation. Chapter 4 introduces the analytical framework and presents the general NoC performance trends. Chapter 5 describes the final derived analytical model for Altera and Xilinx FPGAs. Chapter 6 verifies our analytical model using a new set of benchmark circuits. Finally, Chapter 7 summarizes the conclusions of this work and possible areas for future work.

## Chapter 2

# Background

In order to fully characterize how varied NoC parameters affect system performance, diverse topologies are used to encapsulate the different network parameters. This chapter introduces the various network topologies used in our experiments and their properties, along with a thorough discussion of previous work done to investigate NoCs implemented on FPGAs.

## 2.1 Terminology

A network topology describes the connectivity between network nodes in an NoC. As shown in Figure 2.1, the topologies that are analyzed in our research include the (a)ring, (b)mesh, (c)star, (d)fully-connected, (e)torus, and (f)hypercube topologies, which are commonly used in many applications. In our experiments, the number of columns for the mesh topology is fixed at four. The size of the mesh topology is varied by increasing or decreasing the number of rows. Using these topologies, the experiments are further expanded by including both homogeneous or heterogeneous NoCs. A homogeneous NoC consists of identical network nodes, whereas a heterogeneous NoC consists of a set of different network nodes. A number of parameters are used to characterize a topology as shown in Table 2.1. For a given topology, the diameter of the topology is the maximum distance between any two nodes using existing links. The link complexity is the total number of links a topology requires. The node degree

Figure 2.1: Network topologies

Table 2.1: Network topology characteristics

| Topology        | Diameter       | Link Complexity | Node Degree | Regular |

|-----------------|----------------|-----------------|-------------|---------|

| Ring            | n/2            | n               | 2           | yes     |

| Mesh            | $2(n^{1/2}-1)$ | $2(n-n^{1/2})$  | 2,3,4       | no      |

| Star            | 2              | n-1             | 1, n-1      | no      |

| Fully-Connected | 1              | (n(n-1))/2      | n-1         | yes     |

| Torus           | n/2            | n               | 4           | yes     |

| Hypercube       | $\log_2 n$     | $(n\log_2 n)/2$ | $log_2n$    | yes     |

is the number of links from a node to its connected neighbours. Furthermore, a regular topology is defined as a topology where all nodes share the same node degree. Finally, the average node degree (not shown in Table 2.1) is the average number of links for all nodes. Also not shown is the link width, which is the number of bits in each link between network nodes.

In addition to these common topologies, the experiments also include random topologies, which are used to model application-specific topologies. Random topologies are used to model application-specific NoCs where connections between nodes are defined by application needs rather than using a topology in Figure 2.1 that could lead to unused connections. How random topologies are generated is discussed in Section 3.1.1.

## 2.2 Related Work

Research involving NoCs on FPGAs predominantly focuses on the design and implementation of NoCs. Network architectures investigate different switching elements to provide the best throughput and bandwidth. Changes to the FPGA architecture have also been suggested to better support NoCs as they become more popular. Furthermore, customized CAD tool flows have been developed to simplify the design process of NoCs. Our research focuses on characterizing NoC performance on existing FPGAs using our own customized tool flow. Using our results we develop an analytical model that describes the system performance as a function of various network parameters. This section describes previous research done for NoCs on FPGAs, along with some examples of analytical models for FPGAs.

#### 2.2.1 Network Architecture

When designing FPGA-based NoCs, there are a number of design characteristics that are considered to optimize NoC performance. Numerous studies investigate different switch and router architectures that are targeted for use on FPGAs. Kapre investigates a high-performance, packet-switched, on-chip network [30]. Packet switching groups all transmitted data into suitable blocks to be routed over a shared network. In contrast Kapre's work, a

parallel study by Mehta investigates highly-scalable, time-multiplexed, FPGA networks [44]. A time-multiplexed network relies on transmitting blocks of data from multiple nodes over the same network, sharing the resources over blocks of time. Both studies analyze the performance of their respective switch architecture for different network topologies and provide a measure of performance for both types of network interface on the Xilinx XCV4000. Kapre et al. then performs a direct comparison of the two switch architectures [31]. The study found that packet-switched networks typically outperform time-multiplexed systems for NoCs with under 100 nodes. Furthermore butterfly fat-trees are the best performing topology for both architectures.

Sethuraman et al. proposes a lightweight parallel router, which can support five simultaneous routing requests, with minimal overhead, implemented on a Xilinx XC2VP30 [54]. The router utilizes optimizations in XY routing and decoding logic that maximize the performance to area ratio. With minimal packet overhead, the router is implemented using 3x3 mesh networks and characterized for power and performance parameters. Bartic et al. investigates a topology adaptable communication network design [5]. A versatile network platform is introduced with the IP interfaces, ISP, and an operating system (OS) managing all network resources. This architecture allows the possibility of dynamically changing the packet routing for each IP, in every router, allowing a better balance in network traffic. However, the proposed architecture experiences a quadratic increase in resource utilization as the number of input signals increases. Zeferino et al. presents a router soft core for NoCs called RASoC [59]. The router architecture is used in the building of NoCs for embedded systems. The model relies on a parameterized VHDL module, which allows reuse of RASoC in the synthesis of NoCs with different sizes. However, significant overhead in resource utilization is reported. The overhead is attributed to the complicated switch design and routing algorithm implementation.

Bertozzi et al. designs a complete NoC infrastructure called Xpipes [7]. The system consists of a library of switches, network interfaces, and links, that are designed to be tuned to specific heterogeneous architectures. Links can be pipelined to a flexible number of stages

to separate a link's latency from its throughput. Furthermore, a tool called XpipesCompiler is developed that automatically instantiates a customized NoC using its library of network components based on a given set of design parameters. Hilton et al. presents a flexible circuit-switched NoC for FPGA-based systems called PNoC [24]. In contrast to packet-switching, which uses a shared network resource, circuit-switching relies on establishing a connection between nodes before transmission can occur. While PNoC demonstrates a 23x speedup when compared with a shared bus implementation, a direct comparison between PNoC and a packet-switched network is not performed as a suitable packet-switched architecture was not developed yet.

These switch architectures, along with different bus architectures and proposed FPGA architectural changes, are compared by Mak et al. [43]. The investigation acknowledges that it is difficult to compare the different NoCs, as their respective implementations are often time applied to specific applications. The paper identifies that due to the unique requirements of different applications, there exists a problem of searching for optimal communication architectures from a huge design space since choices are often performed ad-hoc. Our work takes a step in this direction providing a method of predicting the performance of NoCs to enable easier design space exploration.

From all these investigations, NoCs on FPGAs are advocated as a promising solution to on-chip communication especially in Multi-Processor Systems-on-Chip (MPSoC) design. These investigations focus on the philosophy of "routing packets, not wires" [14][53], thus the network interface itself is the focus of much of the research. Selecting appropriate switch architectures, when used in conjunction with our work, can improve the means of selecting an optimized NoC model.

#### 2.2.2 Architectural Changes

Since the routing and resources for FPGAs are fixed, possible architectural changes to FPGAs have also been investigated to improve the performance of NoCs. In terms of architectural changes, research has predominantly focused on changing the wiring types

in FPGAs, and adding network switches or routers as embedded blocks. All studies aim to minimize area overhead, while maximizing data throughput and bandwidth for systems utilizing an NoC as its communication infrastructure.

Francis et al. shows that fine-grain, time-division-multiplexed wiring outperforms conventional wiring for networks on FPGAs [16][15]. Time-division multiplexed (TDM) wiring consists of FPGA wiring links that are shared amongst different IP blocks. This allows for increased capacity on individual wiring links while decreasing the silicon area. TDM wiring is scheduled serially within a discrete time slot, with the interconnect pipelined at a higher rate than the design to increase data throughput. The investigation shows that using TDM wiring can reduce the amount of FPGA configurable wiring by up to 83% and reduce the complexity of switch boxes, thus leading to an overall reduction in silicon area.

Goossens et al. illustrates a dedicated NoC interconnect fabric hardwired in an FP-GAs [19]. By proposing a hardwired NoC, some area of the FPGA is lost to a fixed function. However, Goossens proposes that the loss of flexibility is outweighed by the reduced implementation costs and greater flexibility in dynamic partial reconfiguration. The investigation uses hardwired NoCs as functional interconnect between IP blocks and configuration interconnect that are used to transport data. The proposed hardwired NoC has a 10% overhead for IP sizes with approximately 1400 Look-Up Tables (LUTs).

Gindin et al. presents an NoC architecture based on a proposed routing scheme called Weighted Ordered Toggle (WOT) [18]. WOT utilizes simple, small-area, on-chip routers with low memory demands. The architecture consists of an island-style FPGA with configurable network interfaces at each "island," on the assumption that most applications implemented on this architecture will use a network style interface. Each network interface uses the WOT routing algorithm, which is a packet-switched network that toggles the flow of packets in the horizontal and vertical directions. Ahmadinia et al. describes a dynamic network-on-chip (DyNoC) consisting of a coarse-grain programmable fabric interlinked with circuit-switched busses called Reconfigurable Multiplexed Bus (RMBoC) and connected to each configurable region via on-chip switches [3]. A new routing algorithm is proposed such

that the network-on-chip architecture can be realized with run-time configuration. Due to the complexity of the system, the on-chip switches consume a large area of the design. For a Xilinx Virtex-II 1000 device, 21% and 46% of logic resources are devoted to the on-chip switches of word-length 32-bit and 64-bit respectively. Similarly, Jovanovic et al. presents an island style architecture (CuNoC) with communication units (CU) placed at each configurable region [29]. Each CU consisted of a simple packet forwarding switch based on the priority-to-the-right rule. CuNoC is shown to have good performance and much less overhead when compared to DyNoC.

For all investigations, architectural changes show improved performance for applications that require NoCs. However, due to increased overhead, these changes may not necessarily be beneficial in other types of systems. Whereas these investigations propose possible changes to FPGA architecture to support NoCs, our objective is to understand how the existing interconnect fabric constrains NoC performance on commercial FPGAs. Thus the focus is on existing modern architectures and not on architectural changes.

#### 2.2.3 CAD Tool Flows

In order to fully exploit FPGA resources, complex CAD algorithms are used to place and route NoCs on FPGAs. Research has been done to create automated design flows that target NoCs on FPGAs. Bertozzi et al. presents a complete synthesis flow, called NetChip, for customized NoC architectures [8]. The flow partitions the development work into topology mapping, selection, and generation. The entire flow implements a reusable and scalable network component's library called timespipe that is design-time tunable and customizable to achieve arbitrary topologies. Several case studies are presented showing the use of NetChip in generating NoCs.

Kumar et al. develops an automated design flow to instantiate Multi-Processor Systems on Chip (MPSoC), with an NoC communication scheme [34]. The NoC specifications are done on a high level of abstraction, relieving the designer of low level design. The flow is used to generate a set of sample designs verified on a Xilinx Virtex II 6000. In addition

to the automatic generation, a run-time flow is presented that allows easy debugging and reconfiguration of the system via a host. Sethuraman et al. presents an algorithm which optimally maps custom routers called optiMap [55]. Each router consists of a multi-local port router capable of handling multiple logic cores in parallel. For a given NoC, optiMap finds the optimal number of routers, configuration of each router, optimal mesh topology and the final mapping of the NoC. In comparison to a single-local port version of the same router, the investigation observed an average of 36% area savings based on the Virtex 2 Pro 30.

A framework based on the Xilinx Embedded Development Kit (EDK) is also presented by Lukovix et al. [41]. The described framework represents a fully integrated design flow for fast generation of NoC-based MPSoCs on Xilinx FPGAs. In our research, we employ a similar tool flow to automatically generate a wide variety of NoC systems required for this investigation. However, our tool flow is capable of generating NoCs based on both Xilinx EDK and Altera Quartus CAD flows. A similar tool flow is also developed by Saldana et al [51]. The tool flow took an existing system generated for Xilinx EDK and changed the system files to describe the desired NoC system. The newly generated tool flow is developed in C and works independently of any existing systems. All file generation is hard coded into the tool flow to avoid any extraneous inputs. The details on the tool flow design are given in Section 3.2.

## 2.2.4 Previous Analytical Model Work

In the past, research has primarily evaluated FPGA architectures and applications using empirical analysis to find the best parameters to optimize performance. More recently, there has been a growing trend to express FPGA performance using analytical models to enable better design exploration when designing for FPGAs. Ahman et al. presents an analytical model that predicts interconnect requirements in FPGAs based on the number of look-up-tables (LUTs) in the FPGA [50]. This analytical model for two-dimensional FPGAs is calibrated using fully routed benchmark circuits and extended to three-dimensional

FPGAs. The investigation found that for FPGAs with more than 20,000 4-input LUTs, three-dimensional FPGAs can potentially reduce channel width, interconnect delay and power dissipation by up to 50%.

Lam et al. describes an analytical model that relates logic parameters to the area efficiency of an FPGA based on Rent's Rule [36]. The model relates the LUT and cluster size, and the number of inputs per cluster to the amount of logic that can be packed into each cluster. Due to the simplicity of the analytical model, the analysis can provide a tool for FPGA designers to better understand and guide the development of future FPGA architectures. An analytical model that relates FPGA architectural parameters with the average prerouting wirelength is presented by Smith et al. [57]. This model encompasses both homogeneous and heterogeneous FPGA architectures. For homogeneous FPGAs, the wirelength is related to the LUT and cluster size, and the number of inputs per cluster. For heterogeneous FPGAs, in addition to the parameters investigated for homogeneous FPGAs, the position of embedded blocks as well as the number of pins to each block is also considered. Much like the evaluations done in these works, our research focuses on developing an analytical model that enables designers to perform design space exploration for FPGA-based NoCs.

#### 2.2.5 Analytical Models for NoCs

In this work, an analytical model describing the performance of an NoC is presented. Although a general analytical model describing the performance of a wide range of NoCs have not been investigated, several studies have investigated the performance of NoCs for specific applications. Lee et al. [37] describes an analytical model to predict the area, performance, and energy consumption of an MPEG-2 encoder application implemented on a Virtex2 3000 FPGA. The study analyzes the difference between using a network, point-to-point, or a shared bus for communication between nodes. It found that: 1) the performance of the NoC design is very close to the point-to-point (P2P) implementation, 2) the NoC implementation scales better in area than the P2P and bus-based implementations, and

3) the NoC implementation has lower energy consumption than the P2P and bus-based implementations.

Freitas et al. performs a study comparing the performance of a MPSoC system using bus-based communication to a mesh network [17]. The work utilizes MicroBlaze soft processors on a Xilinx Virtex 2 Pro 20 with 4-node and 16-node systems. The work concludes that MPSoCs benefits in performance when using NoCs versus bus-based systems. Similarly, Saldana et al. investigates the routability of multiprocessor network topologies on FPGAs [51]. Ring, star, mesh, hypercube, and fully connected topologies from 8 to 32 nodes are utilized to characterize the performance and area requirements on a Xilinx Virtex 4LX200. It is determined that all topologies except for fully connected performed well up to 32-nodes

The work in this thesis expands on the work done by Shannon et al. [51]. Preliminary results from this work is also presented in previous publications. Lee et al. presents the effects of node size, heterogeneity, and network size on NoC performance [38]. It is shown that the number of nodes has a greater affect on performance than node size and heterogeneity. Lee et al. further investigates NoC performance by developing an analytical model to predict the performance of NoCs due to local and global routing demand on Xilinx FP-GAs [39]. The work presented in this thesis expands on these results [38] [39], utilizing both Xilinx and Altera FPGAs. Bandwidth, resource utilization, and the use of relatively placed modules are also explored in this thesis.

## Chapter 3

# Experiment Methodology

The objective of this research is to investigate how an NoC topology and its associated characteristics effects performance. Specifically, the focus is on the routing resources and how the NoC maps to an FPGA's fixed interconnect based on different NoC parameters. To do this, we utilize a vast exploration space, which includes homogeneous and heterogeneous topologies for a wide range of FPGA devices. The following chapter describes the NoC design used in our experiments, and the custom tool flow developed to automatically generate these NoCs.

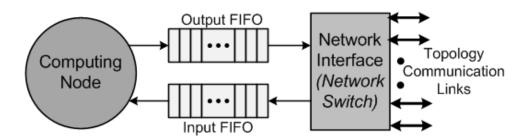

Figure 3.1: Network node

Figure 3.2: MicroBlaze computing node

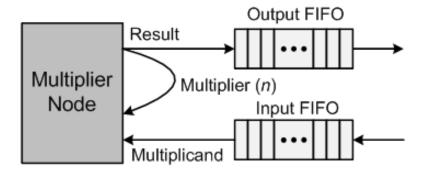

Figure 3.3: Multiplier computing node

### 3.1 Network Nodes

Section 2.1 illustrates the different network topologies, including common and application-specific topologies that are used in our experiments. Each network node, as shown in Figure 3.1, consists of a computing node, two FIFOs, and a network interface linked to the network interconnect using topology communication links. Each computing node communicates with the network interface through two, synchronous, 16-word-deep FIFOs. For Xilinx FPGAs, these FIFOs are implemented using Fast Simplex Links (FSLs) mapped to LUT-RAMs. For Altera FPGAs, these FIFOs are implemented using equivalent M-LABs, which are only supported by the Stratix III and Stratix IV families.

## 3.1.1 Computing Node

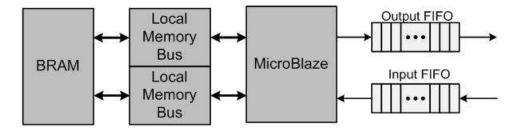

Two types of computing nodes are used; a MicroBlaze soft processor and a custom computing node. The MicroBlaze, as shown in Figure 3.2 is used to compare our newly updated tool

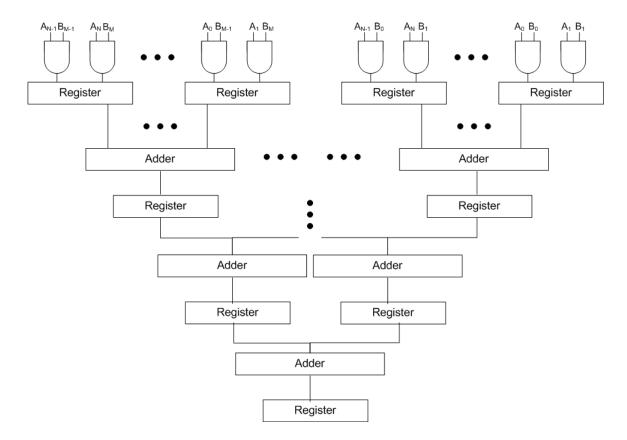

Figure 3.4: Multiplier architecture

Table 3.1: Homogeneous multiplier node types

UBlaze | MultHalf | MultBase | Mult

|       |        |          |      |          |      | 0 1        |      |

|-------|--------|----------|------|----------|------|------------|------|

| Link  | uBlaze | MultHalf |      | MultBase |      | MultDouble |      |

| Width | LUTs   | Mult     | LUTs | Mult     | LUTs | Mult       | LUTs |

| 48    |        | 2        | 347  | 4        | 658  | 6          | 1312 |

| 40    |        | 2        | 396  | 4        | 703  | 6          | 1487 |

| 32    | 629    | 4        | 371  | 6        | 694  | 8          | 1429 |

| 24    |        | 6        | 328  | 8        | 652  | 12         | 1393 |

| 16    |        | 8        | 311  | 12       | 614  | 16         | 1374 |

|       |        |          |      |          |      |            |      |

flow with the previous work [51]. Since our investigation focuses on the topology and network links (topology communication links), and not the computing nodes, the computing node has to meet a set of requirements that ensures that it does not contaminate the data obtained to characterize the links. Specifically, the computing node needs to: 1) not be the critical path in the design, 2) use only CLBs and no embedded blocks to ensure portability between Altera and Xilinx devices, and 3) ideally have all combinatorial operations registered in the same CLB to improve timing. The multiplier node in Figure 3.3 meets all these requirements. The multiplier consists of 2-bit partial-products pipelined at each stage as shown in Figure 3.4. Although actual network implementations would contain more complex computing nodes, such as a MicroBlaze soft processor, it is not helpful for this study. If a MicroBlaze is used as the compute node, then in small NoC systems, the critical path would be in the node itself, and not in the topology communication links. Furthermore, the link width cannot be changed for a MicroBlaze node and it is not portable to non-Xilinx FPGAs. In contrast, the multiplier node's size as well as link width can be adjusted, allowing us to experiment with different link widths, and topologies with different network node sizes. Therefore we only use the MicroBlaze in our new analysis to compare current state of the art CAD tools with previous work [51].

As shown in Figure 3.3, the *multiplicand* of the multiplier node is equal to the link-width, and the *multiplier* is equal to the lower n bits of the result. We consider both homogeneous and heterogeneous NoC types; in a homogeneous network, all nodes are of the same size, while in a heterogeneous network, different node sizes exist. As the *multiplicand* always remains fixed to the link-width, the *multiplier* (n) is varied to scale the resource usage. For a given

Table 3.2: Heterogeneous multiplier node types

| Link  | MultSmall      | MultFull        | MultLarge      |

|-------|----------------|-----------------|----------------|

| Width | Range of Mults | Range of Mults  | Range of Mults |

| 48    | 2,4            | 2,4,6,8         | 4,6,8          |

| 40    | 2,4            | 2,4,6,8         | 4,6,8          |

| 32    | 2,4,6          | 2,4,6,8,10      | 6,8,10         |

| 24    | 4,6,8          | 4,6,8,10,12,14  | 10,12,14       |

| 16    | 6,8,10         | 6,8,10,12,14,16 | 12,14,16       |

heterogeneous or homogeneous system, the link width remains fixed for all network nodes. Table 3.1 lists the multiplier sizes used in our homogeneous experiments. *Mult* is defined as the width (*n-bits*) of the multiplier, and *Link Width* is equal to the multiplicand width. We used five different link widths, with three different multiplier widths for each link-width. The baseline multiplier *MultBase* is chosen to have approximately the same LUT usage as a MicroBlaze on a Virtex 5. *MultHalf* is approximately half the size, and *MultDouble* approximately twice the size. As the link width changes, the multiplier width also needs to be adjusted to maintain approximately constant resource usage for the computing node. The percent variation in LUT usage for each node type is 7.12% with a standard deviation of 3.2%.

To generate heterogeneous NoCs, we kept the link width (multiplicand) fixed for the design and varied the network node size by scaling the multiplier bit-width. We use three types of heterogeneous NoCs (MultSmall, MultFull, MultLarge) generated using a range of multiplier node sizes defined by a minimum and maximum multiplier bit-width. The size of each multiplier node in a heterogeneous topology is chosen at random and uniformly distributed across the range of multiplier widths defined by the heterogeneous NoC type and fixed link width. Table 3.2 lists the range of sizes used in our heterogeneous experiments for varied link widths.

Figure 3.5: Network interface resource utilization

#### 3.1.2 Network Interface

Since we are interested in the performance achieved by the CAD flow's ability to leverage the over-provisioned routing resources to implement the links that define the NoC topology, and not the NoC's performance in terms of bandwidth and throughput, we use a lightweight network switch. In order to isolate the performance of the network interface and subsequently the network node from the interconnect, the output from the network interface to the link is registered. The network switch is a lightweight packet switch that broadcasts an address control packet to all its linked neighbours. A receiving switch only reads the control packet and subsequent packets if the address matches its own and otherwise ignores it. These switches are only capable of sending to and receiving from their directly connected neighbours and are not capable of multi-hop communication. While extremely simple, this switch is sufficient for the purpose of our studies, which focuses on the performance of various topologies on an FPGA's fixed interconnect and not on the switch architecture or packet latency and throughput.

The size of each switch is defined by its number of ports. The NoC topology in turn

Figure 3.6: Network overhead on Xilinx Virtex 5 LX330

defines the number of ports required by each network node's switch. For example, a torus is a regular topology with all network nodes having a node degree of four. This means that each network interface has four ports or four channels. Each channel comprises two unidirectional links to form a bidirectional channel. In contrast, a mesh topology has network switches with node degrees of two, three and four. Therefore the system will require three different network switches with two, three, and four ports. All network nodes on the perimeter of the mesh require a network switch with three ports except the corner network nodes, which require a network switch with two ports. Finally, the interior network nodes require a network switch with four ports. Recall that in Figure 2.1 each topology is illustrated, and the network switches required by each network node can be determined by the number of links connected to a given node. As the number of links to the network switch grows, the resource utilization also increases linearly. Figure 3.5 shows the resource utilization (Number of LUTs) of different network interface sizes. This ensures that the total resource utilization of the network node (i.e. including the computing node, FIFOs, and network interface) increases linearly.

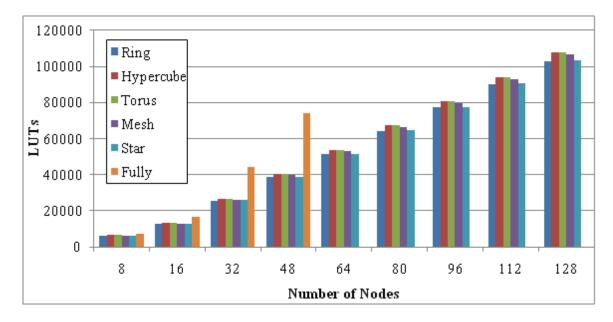

The network switch overhead is defined as the resource usage utilized by all network

switches in the NoC topology as a percentage of total resources. In order to determine the network switch overhead of each topology, we measure the percentage of total resources occupied by the network connectivity. Figure 3.6 shows the network overhead for homogeneous ring, hypercube, torus, mesh, star, and fully connected topologies with MultBase nodes and 32-bit link widths.

As seen in Figure 3.6, for all topologies other than the fully connected, mesh, and star topologies, the network connectivity occupies a constant percentage of total resources as the number of nodes increase. This trend is expected since the resource usage of each individual network switch remains constant for the ring, hypercube, and torus topology. Thus when the NoC increases in the number of nodes, the total resource usage of all network switches should increase at the same rate as the total resources occupied by the entire NoC topology.

For small mesh topologies, the number of network switches with two or three ports is greater than the network switches with four ports. However, as a mesh gets bigger there are more four port network switches than two or three port network switches. This is shown by the increase in network overhead from 8 to 48 nodes due to an increase in four port nodes in relation to two and three port nodes. The network overhead eventually levels off for larger mesh topologies as the majority of switches utilize four ports. Furthermore, the slight increase in network overhead for the star topology is due to the increase in ports for the central node's network switch; and the large increase in network overhead for the fully connected topology is due to the increase in ports for all network nodes in the system.

#### 3.2 Custom Tool Flow

In our experiments, we use approximately 3600 benchmark circuits that are generated using an automated benchmark circuit generator. The generator supports six of the common network topologies, previously shown in Figure 2.1, and application-specific topologies modeled using random topologies, with several different node sizes. The use of such a generator allows us to run many more experiments than would be possible using "real" benchmark circuits; this, in turn, allows us to isolate the impact of each NoC parameter on the overall

Figure 3.7: Custom tool flow

performance of the system.

Figure 3.7 shows the tool flow used to generate the benchmark circuits. The code for the *topology generator* is presented in Appendix A, and the code for the *system generator* is shown in Appendix B. The topology generator outputs a topology description file that defines the connectivity between each network node based on a given set of input parameters. These inputs define the NoC topology characteristics and are listed below:

- Number of Nodes the number of nodes in a given system

- Topology Type Torus, Hypercube, Ring, Mesh, Star, Fully Connected, Application-Specific (modelled using random topologies)

- Average Node Degree (optional, if topology is random) the average number of links to all nodes

Common topologies have a predefined connectivity pattern, however application-specific topologies are not predefined. Therefore for application-specific topologies, given a fixed number of nodes, links are randomly generated between nodes until the average node degree is met and all nodes have at least one link. The topology description file illustrates the number of nodes, and the switch and node properties. The number of switches is determined by the topology type. If the topology is regular, than there is only one switch type. If the

topology is not regular, than the number of switch types depend on the connectivity of all nodes. For example, as previously described, a mesh topology requires three switch types. Given the topology description file, the system generator produces the necessary files used by either the Altera and Xilinx CAD tool suites depending on the input parameters shown below:

- NoC Type Homogeneous/Heterogeneous

- Node Sizes Multiplier width or range

- Link Width Width of point-to-point links between nodes (FIFOs)

- FPGA Vendor Xilinx/Altera

- FPGA Family Virtex 2 Pro, Virtex 4, Virtex 5, Virtex 6, Stratix III, Stratix IV

- FPGA Device Specific device for a given FPGA family

- Maximum Operating Frequency Target operating frequency used by the CAD tools

The output files include verilog files describing the NoC and run-time parameters needed by the tool suite. Using the system and topology generator, a wide range of NoCs can be generated. The topology generator can produce topologies of any size, and the system generator can create all necessary files required by the CAD tool suites to implement a wide variety of NoC designs. This provides the necessary framework to generate the infrastructure required by the investigation.

## 3.3 Testing Methodology

Our experiments aim to quantify and characterize the routability and performance of NoCs on a variety of FPGA architectures. Using our benchmark circuits, we generate approximately 3600 circuits to encapsulate the effects of different network parameters. These

Figure 3.8: Distribution of experiments for each topology

circuits included ring, torus, mesh, hypercube, star, fully connected, and random topologies of varied link width and number of nodes. The distribution of experiments based on topology type in shown in Figure 3.8.

Since random topologies include systems with varying average node degree, these topologies constitute a greater percentage of total experiments. For the ring, torus, and mesh topologies, circuits are generated from 8 to 128 nodes at 8 node intervals. For the hypercube topology, there can only be  $2^n$  nodes, thus there are fewer hypercube experiments. The fully connected and star topology is investigated in greater detail to pinpoint where systems fail to route. Thus circuits for these two topologies are generated from 8 to 128 nodes at 4 node intervals.

While having a wide range of NoCs is essential to characterizing NoC performance, we also synthesize these experiments onto multiple Xilinx and Altera FPGA device families. This allows us to demonstrate if the results are device or family specific. The devices that we use in our experiments are listed in Table 3.3. Column 1 lists the processing technologies of each device, and Columns 2 and 3 show the family and devices for Xilinx FPGAs and

Table 3.3: FPGA family and devices

| Processing | Xilinx            |              | Altera           |             |

|------------|-------------------|--------------|------------------|-------------|

| Technology | Family            | Devices      | Family           | Devices     |

| 130nm      | Virtex 2 Pro [25] | XC2VP100-6   |                  |             |

|            |                   | XCV4LX200-11 |                  |             |

| 90nm       | Virtex 4 [27]     | XCV4LX160-11 | Stratix II [11]  |             |

|            |                   | XCV4LX100-11 | (Not Used)       |             |

|            |                   | XCV5LX330-2  |                  | EP3SL340-4  |

| 60nm       | Virtex 5 [26]     | XCV5LX220-2  | Stratix III [12] | EP3SL200-4  |

|            |                   | XCV5LX155-2  |                  | EP3SL150-4  |

|            |                   | XCV6LX760-2  |                  | EP4SE530-I4 |

| 40nm       | Virtex 6 [28]     | XCV6LX365T-2 | Stratix IV [13]  | EP4SE360-I4 |

|            |                   | XCV6LX240T-2 |                  | EP4SE230-I4 |

Columns 4 and 5 show the family and devices for Altera FPGAs. While Xilinx and Altera FPGAs share the same processing technologies, their architectures are different, thus we expect some differences in performance. Since previous work also uses all Virtex 2 Pro FPGAs listed in Table 3.3, and the Virtex 4LV100 FPGA [51], we use the same FPGAs when performing our comparison with previous work.

All our benchmark circuits are synthesized for all the FPGA devices listed in Table 3.3. We found that while our model is the same for Xilinx and Altera FPGAs, the coefficients of our framework are unique between Xilinx and Altera FPGAs. Therefore, for our analytical model describing Xilinx FPGAs, our model coefficients are tuned by first running training experiments using Xilinx EDK 10.1.02 with the Virtex 2 Pro, Virtex 4, and Virtex 5 FPGAs as listed in Table 3.3. In order to evaluate the accuracy of our model, we use the Virtex 4, Virtex 5, and Virtex 6 FPGAs listed in Table 3.3, with EDK 11.2. For our Altera model, the training experiments use Altera Stratix III FPGAs, and the verification experiments use Stratix III and Stratix IV FPGAs listed in Table 3.3. Both sets of experiments are synthesized using Quartus 9.1. Only two Stratix devices are used since these devices are the only ones that are capable of mapping the network node's FIFOs to M-LABs.

In order to obtain accurate results, each design is synthesized multiple times. Initially for our Xilinx model, we ran experiments using the Xilinx Xplorer utility, which synthesizes

designs using known place and route parameters to provide the best results. However, we found that the utility resulted in extremely long run times (on the order of 5-7 days) for each experiment, since the utility always runs to completion even when the maximum operating frequency converges before that point. Therefore, we only use the utility to form a baseline of comparison for the remaining experiments.

Rather than using the Xplorer utility, we are able to approximate Xplorer's process by synthesizing designs multiple times using different seeds, with the maximum operating frequency averaged over each run. The number of iterations is determined by repeating iterations until at least five iterations are run and the change in the average result over all runs is less than 5%. When the results do not converge (which occurs in less than 8% of our experiments), we set an upper bound on the experiments to ten iterations. This method has an average variation of 2.1% to the Xilinx Xplorer utility. A design is deemed unroutable if the design can not route for at least eight out of the ten iterations. This method results in shorter run times, since using our method limits the number of experiments once performance converges.

## Chapter 4

# Deriving an Analytical Framework for NoCs

The objective of this work is to create an analytical model that describes the maximum operating frequency of an NoC. Experimental results are used to derive the coefficients for these equations for a selected device. Our analysis focuses on how specific NoC parameters affect routability and performance of an NoC utilizing both homogeneous and heterogeneous topologies. The key parameters that are investigated include heterogeneity, resource usage, the number of nodes, average node degree, and link width of the topology.

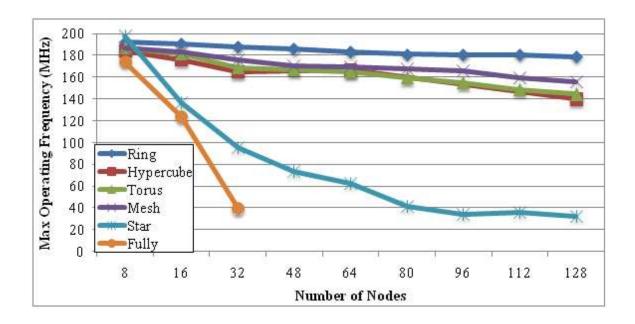

Our overall approach is as follows. We arbitrarily chose an 8-node ring topology with a 32-bit link-width as a baseline architecture, and denote the maximum frequency of this baseline architecture implemented on a given FPGA as  $F_{base}$ . Therefore, the predicted frequency  $F_{pred}$  is quantified as a percentage performance of the baseline performance. For different NoC architectures, we then scale  $F_{base}$  using two factors. The framework is shown below:

$$F_{pred} = k_{GRD} \times k_{LRD} \times F_{base}, \tag{4.1}$$

where the terms  $k_{LRD}$  and  $k_{GRD}$  are functions of the NoC topology, the link width, and

the number of nodes in the NoC. The first scaling factor in the above equation,  $k_{LRD}$ , models the impact of local routing demand. Local routing demand is defined by the routing requirements of a single network node. Network nodes that have a high number of links will tend to have more congestion around their network interfaces. The CAD tools resolve this congestion by either using non-direct routes, or by spreading out the logic related to those nodes with high degree. The impact is a decrease in the maximum frequency of the network; the magnitude of this decrease is encapsulated in  $k_{LRD}$ .

The second scaling factor in the above equation,  $k_{GRD}$ , models the impact of global routing demand. Global routing demand is characterized by the routing requirements of the entire NoC. Topologies that have a large number of links will require more wires. As the number of links increases, the difficulty in routing these connections increases, again leading to a reduction in the maximum frequency of the network. The magnitude of this decrease is encapsulated in  $k_{GRD}$ .

Our investigation aims to derive closed-form expressions for  $k_{LRD}$  and  $k_{GRD}$  using a combination of analytical derivations and empirical curve-fitting from experiments. Before experimentally deriving the specific constants to calibrate our model to Xilinx and Altera device families, we present the characteristics of our generated benchmark circuits. Using these characteristics, we illustrate that there are consistent performance trends, indicating that we can create an analytical model capable of predicting performance. First, an investigation is performed to compare our current generation scripts with previous work [51] to demonstrate how improvements in CAD tools might have improved routability in our new benchmarks. Since Altera and Xilinx FPGAs share the same routing fabric for their FP-GAs, we expect that the analytical model is the same for all FPGAs. Only the coefficients are tuned for Altera FPGAs and Xilinx FPGAs, thus the Altera analytical model can be applied to all Stratix FPGAs, and the Xilinx analytical model can be applied to all Virtex FPGAs. Therefore, in order to verify this, we analyze the variation in performance for the same benchmark circuits amongst different Xilinx and altera FPGAs.

After analyzing the characteristics of our benchmark circuits in comparison with previous

work and among different FPGAs, we present the general performance trends exhibited by specific NoC topologies that strain local and global routing demand on FPGAs. Resource usage is investigated first to demonstrate if NoC performance is dictated by resource usage alone or by the characteristics of the NoC. After, an analysis is performed to determine the effects of the network node alone by: 1) changing the number of nodes, 2) changing the node size, and 3) investigating heterogeneous and homogeneous network nodes. These results are then included in the investigation of local and global routing demand and its effects on NoC performance. The analysis in this chapter is highlighted using the Xilinx Virtex 5 LX330 and the Altera Stratix III 340 for simplicity. All results are consistent for different devices within the same vendor, which will be shown in Section 4.2. These two FPGAs are chosen since they have approximately the same resource availability; however, each vendor has a different FPGA architecture. The Altera Stratix III 340 has the equivalent of 338,000 4-input LEs and the Virtex 5 has 207,360 6-input LUTs, thus we will expect some performance differences between the two FPGAs. The results found in this section are applicable to all Xilinx and Altera FPGAs investigated.

#### 4.1 Previous Research

Previous work developed a custom framework that only instantiated MPSoCs on Xilinx FPGAs[51]. This framework is restrictive in scope, thus in this work, a new framework is developed that can generate a wide range of NoCs including MPSoCs on both Xilinx and Altera FPGAs. Since our experiments utilize newer releases of the Xilinx CAD tools, we compare our generated benchmarks with previous benchmarks to determine how improvements in CAD tools might affect performance and routability.

Previous research showed that homogeneous multiprocessor NoCs exhibited unique trends on FPGAs compared to ASICs. The previous experiments used the MicroBlaze as the computing node and were synthesized to the Xilinx Virtex 2 Pro and Virtex 4 families of FPGAs using Xilinx EDK 7.1. We repeat these experiments with our tool flow using Xilinx EDK 10.1.02 for the ring, star, hypercube, and mesh topologies with 8, 16, and 32 nodes on a

Virtex 4 LX200. For the fully connected topologies, we performed experiments from 8-32 nodes at 4 node intervals. We used the MicroBlaze as the computing node and all IP core versions are the same as previous experiments.

Our new experiments use an average of 8% fewer resources than the previous experiments with a standard deviation of 1.1%. This can be attributed to CAD tool improvements in the newer releases of Xilinx's tool suites. Performance, in terms of max frequency, shows little change with an average improvement of 4.1% and standard deviation of 2.1%. These results exclude the fully connected topologies between 22 and 32 nodes that EDK 10.1.02 can now route, but were previously unroutable by EDK 7.1. Taking into consideration the changes due to an updated tool flow, our new framework is capable of generating MPSoCs that are consistent with previous results. We used the updated system generation scripts are used to produce all the NoCs aimed at characterizing different network parameters and their effects on performance. Before doing this, we first take a look at how the choice in FPGA device can effect performance.

## 4.2 Chip Independence

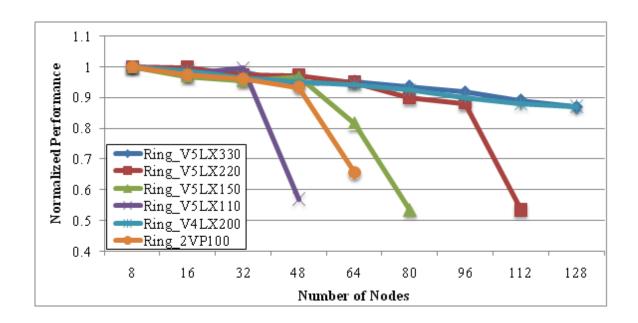

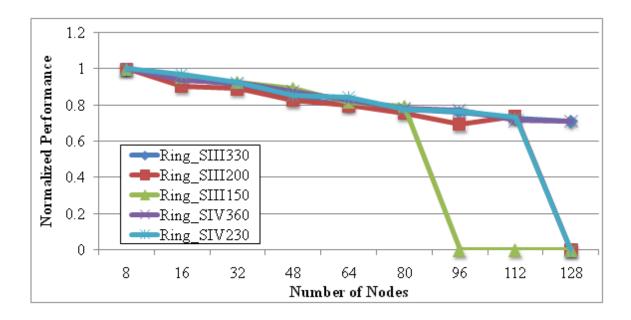

Since Xilinx and Altera FPGAs utilize the same routing fabric among their device families respectively, we expect that we should be able to apply the same analytical model. However, as they are two different FPGA vendors, we expect their respective fabrics to be different. Therefore, while the analytical model should be consistent, the coefficients defining the model have to be tuned to each vendor. In order to determine if this is true, we first look at the effects of changing device families when using the same network topologies. As explained in Section 3.3, a wide range of FPGAs are used to fully characterize the performance of NoCs on a number of platforms. Analyzing the performance results for different Xilinx and Altera FPGAs, we find that different devices and families within the same FPGA vendors exhibit similar trends in performance. When performance is normalized to an eight node ring topology for the selected family, performance has minimal variation between families and devices. Our training experiments involve the devices listed in Table 3.3. Figure 4.1

Figure 4.1: Ring topology on Xilinx FPGAs

Figure 4.2: Ring topology on Altera FPGAs

| Table 4.1 | . D | erformance | moriotion | for | LDC 1 | dorrigon | and | familiag |

|-----------|-----|------------|-----------|-----|-------|----------|-----|----------|

| Table 4.1 | : ٢ | eriormance | variation | 101 | FFGA  | devices  | and | rammes   |

|   |        | Xilinx    |                    | Altera    |                    |  |

|---|--------|-----------|--------------------|-----------|--------------------|--|

|   |        | Variation | Standard Deviation | Variation | Standard Deviation |  |

| F | Family | 3.5%      | 1.4%               | 4.1%      | 1.7%               |  |

| I | Device | 4.2%      | 1.6%               | 5.1%      | 1.2%               |  |

highlights this minimal variation by showing the ring topology for different Xilinx families and devices and Figure 4.2 shows them for different Altera families and devices.

For our Xilinx and Altera experiments, we find that there is minimal variation in performance when moving between different families and devices as shown in Table 4.1. Moving between different families exhibit smaller variations since the chosen devices between families have an equivalent amount of available resources. When moving between different devices, smaller devices have a higher percentage of global routing demand for larger designs. This is shown in Figures 4.1 and 4.2 by the dramatic drops in performance for smaller devices. Thus for very large systems on small devices, systems often fail to route or have very low performance compared to the same design on a larger device. Since performance has minimal variation between families and devices, the same conclusions drawn from our analysis can be applied to all Xilinx Virtex 2 Pro, Virtex 4, Virtex 5, and Virtex 6 FPGAs for our analysis of Xilinx FPGAs and all Altera Stratix III and Stratix IV FPGAs for Altera FPGAs.

## 4.3 Resource Usage

As seen in the previous sections, although trends between FPGA devices remain consistent up to a certain point, we see a drop of performance for smaller devices for a large number of nodes. We expect that this drop is due to resource usage. As a design becomes larger, the CAD tools distribute a design over the given FPGA fabric, and wires grow in length thus decreasing the maximum operating frequency of the system. However, long wire lengths are not always directly correlated with resource usage as the critical path could be a result of high local congestion, or poor design. In this section, we attempt to demonstrate the