# IN-PLACE BONDING OF III-V SEMICONDUCTOR HETEROSTRUCTURES

by

David L. Owen B.Sc., Queen's University, 2005

THESIS SUBMITTED IN PARTIAL FULFILLMENT

OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE

IN THE DEPARTMENT

$\mathsf{OF}$

PHYSICS

© David L. Owen 2009 SIMON FRASER UNIVERSITY Spring 2009

All rights reserved. This work may not be reproduced in whole or in part, by photocopy or other means, without permission of the author.

#### APPROVAL

Name: David L. Owen

Degree: Master of Science

Title of Thesis:

In-Place Bonding of III-V Semiconductor Heterostructures

**Examining Committee:** Dr. Jeffrey McGuirk (Chair)

Dr. Patricia Mooney

Dr. Karen Kavanagh

Dr. Simon Watkins

Dr. Michael Thewalt

**Date Approved:**

April 7th, 2009

# U SIMON FRASER UNIVERSITY

### Declaration of Partial Copyright Licence

The author, whose copyright is declared on the title page of this work, has granted to Simon Fraser University the right to lend this thesis, project or extended essay to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its users.

The author has further granted permission to Simon Fraser University to keep or make a digital copy for use in its circulating collection (currently available to the public at the "Institutional Repository" link of the SFU Library website <www.lib.sfu.ca> at: <a href="http://ir.lib.sfu.ca/handle/1892/112>">http://ir.lib.sfu.ca/handle/1892/112></a>) and, without changing the content, to translate the thesis/project or extended essays, if technically possible, to any medium or format for the purpose of preservation of the digital work.

The author has further agreed that permission for multiple copying of this work for scholarly purposes may be granted by either the author or the Dean of Graduate Studies.

It is understood that copying or publication of this work for financial gain shall not be allowed without the author's written permission.

Permission for public performance, or limited permission for private scholarly use, of any multimedia materials forming part of this work, may have been granted by the author. This information may be found on the separately catalogued multimedia material and in the signed Partial Copyright Licence.

While licensing SFU to permit the above uses, the author retains copyright in the thesis, project or extended essays, including the right to change the work for subsequent purposes, including editing and publishing the work in whole or in part, and licensing other parties, as the author may desire.

The original Partial Copyright Licence attesting to these terms, and signed by this author, may be found in the original bound copy of this work, retained in the Simon Fraser University Archive.

Simon Fraser University Library Burnaby, BC, Canada

## Abstract

Elastically strain-relaxed GaAs/In<sub>0.08</sub>Ga<sub>0.92</sub>As/GaAs heterostructures on GaAs(001) substrates were fabricated. Pseudomorphic heterostructures grown by MOCVD were patterned using conventional photolithography and a sacrificial AlAs layer was removed by selective etching. As etching proceeds and the GaAs/InGaAs/GaAs structure is released from the substrate, elastic strain relaxation occurs and the strain-relaxed structures are weakly bonded in-place to the substrate. The bond between the strain-relaxed structure and the substrate was then strengthened by annealing under conditions similar to those used for whole wafer bonding of GaAs. The strain, composition and thickness of the layers were determined using high resolution X-ray diffraction and the sample surface quality was examined using atomic force microscopy. The degree of strain relaxation of the InGaAs layer is determined by the relative thickness of the GaAs and InGaAs layers in agreement with a force balance model. The increase in the in-plane lattice parameter of the bonded GaAs/In<sub>0.08</sub>Ga<sub>0.92</sub>As/GaAs structures as compared to GaAs is 0.25-0.44%. To my parents

# Acknowledgments

I would like to thank the following individuals: David Lackner and Oliver Pitts for growing the samples used in this experiment, Phil Grant for teaching me how to use the AFM and Grace Li and the 4DLabs staff for their help in the 4DLabs cleanroom. Dr. Karen Kavanagh and Dr. Simon Watkins for their comments and advice regarding this work. Samantha Franks for reminding me to eat during my thesis writing days and Jennifer Godfrey for moral support and cookies. My parents, Annette and Arthur, to whom this thesis is dedicated and my sister, Megan, who introduced me to Ph.D. comics. Finally, Dr. Pat Mooney, my supervisor, who was always available when I had questions and always had helpful advice or suggestions when I was encountering problems.

# Contents

| Ар  | prova          | l                                     | ii  |

|-----|----------------|---------------------------------------|-----|

| Ab  | strac          | t                                     | iii |

| De  | dicati         | on                                    | iv  |

| Ac  | know           | ledgments                             | v   |

| Со  | ntent          | S                                     | vi  |

| Lis | st of <b>T</b> | ables                                 | ix  |

| Lis | st of F        | ligures                               | X   |

| 1   | Intro          | oduction                              | 1   |

| 2   | Wafe           | er Bonding                            | 3   |

|     | 2.1            | Development of Wafer Bonding          | 3   |

|     | 2.2            | Merits of Wafer Bonding               | 4   |

|     | 2.3            | Wafer Bonding Complications           | 5   |

|     | 2.4            | Wafer Bond Strength Tests             | 7   |

|     | 2.5            | Summary                               | 8   |

| 3   | Semi           | iconductor Mismatch, Strain & Defects | 9   |

|     | 3.1            | Mismatch Strain                       | 9   |

|     | 3.2            | Dislocations in III-V Semiconductors  | 10  |

#### CONTENTS

|   | 3.3   | Critical Thickness Behaviour                          | 12 |

|---|-------|-------------------------------------------------------|----|

|   | 3.4   | Summary                                               | 15 |

| 4 | Elas  | tic Strain Relaxation                                 | 17 |

|   | 4.1   | Physics of Elastic Strain Relaxation                  | 17 |

|   | 4.2   | Elastic Strain Relaxation using a Compliant Substrate | 19 |

|   | 4.3   | Elastic Strain Relaxation using a Sacrificial Layer   | 21 |

| 5 | Exp   | eriment Overview and Measurement Techniques           | 24 |

|   | 5.1   | Description of Experiment                             | 24 |

|   | 5.2   | Etchant Chemistry and Behaviour                       | 26 |

|   | 5.3   | Photolithography and Mask Design                      | 28 |

|   | 5.4   | X-Ray Diffraction Technique                           | 29 |

|   |       | 5.4.1 Measured Quantities                             | 30 |

|   | 5.5   | Atomic Force Microscopy                               | 35 |

|   |       | 5.5.1 Tip-Sample Forces                               | 36 |

|   |       | 5.5.2 Force Measurement                               | 37 |

|   |       | 5.5.3 Operating Mode                                  | 38 |

|   | 5.6   | Summary                                               | 39 |

| 6 | Initi | al Sample Characterization                            | 40 |

|   | 6.1   | Individual Layer Properties                           | 40 |

|   | 6.2   | Full Structure Samples                                | 47 |

|   | 6.3   | Determination of Sample Properties via Simulation     | 51 |

| 7 | Sam   | ple Processing                                        | 53 |

|   | 7.1   | Standard Cleanroom Procedure                          | 53 |

|   | 7.2   | Processing Problems                                   | 55 |

|   | 7.3   | Summary                                               | 59 |

| 8 | Post  | -Processing Analysis                                  | 60 |

|   | 8.1   | Strain Relaxation                                     | 60 |

|   | 8.2   | Surface Quality                                       | 64 |

#### CONTENTS

| 9              | Bone         | d Strengthening and Testing | 66 |

|----------------|--------------|-----------------------------|----|

|                | 9.1          | Cleave Test                 | 66 |

|                | 9.2          | Behaviour of Etched Samples | 67 |

|                | 9.3          | Summary                     | 70 |

| 10 Conclusions |              | 71                          |    |

| Bil            | Bibliography |                             |    |

#### viii

# **List of Tables**

| 6.1 | Growth conditions & measured roughness of a 50 nm AlAs layer with a 2 |    |

|-----|-----------------------------------------------------------------------|----|

|     | nm GaAs cap                                                           | 44 |

| 6.2 | Initial measured sample properties                                    | 52 |

| 8.1 | Measured strain relaxation of processed samples                       | 62 |

# **List of Figures**

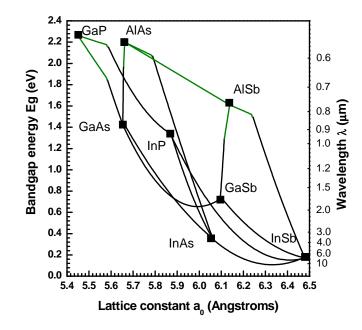

| 1.1 | Bandgap energy and wavelength vs lattice parameter for various III-V alloys.           | 2  |

|-----|----------------------------------------------------------------------------------------|----|

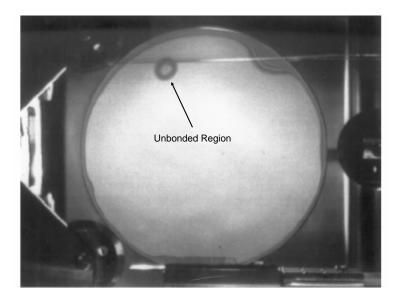

| 2.1 | Infrared micrograph of whole wafer GaAs-GaAs bonding showing an un-                    |    |

|     | bonded region[2].                                                                      | 6  |

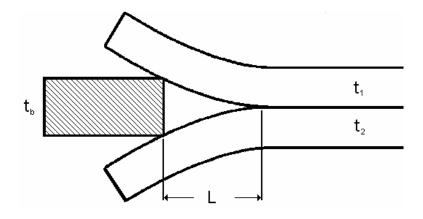

| 2.2 | Schematic diagram of the crack-opening method                                          | 7  |

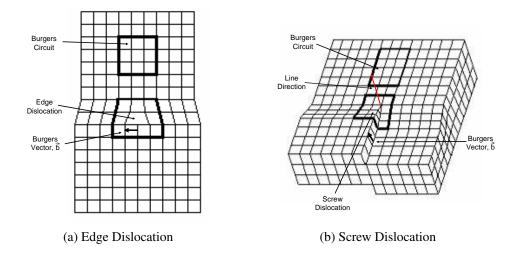

| 3.1 | Schematic diagram of dislocations and their Burgers vectors                            | 11 |

| 3.2 | Orientation of the glide plane in GaAs/In <sub>x</sub> Ga <sub>1-x</sub> As structures | 13 |

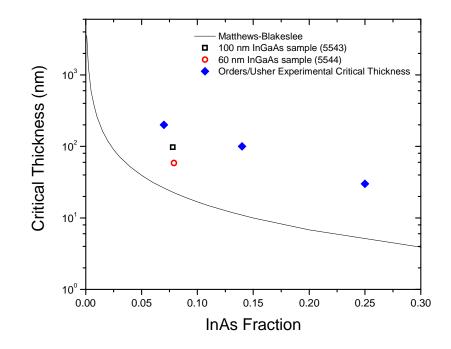

| 3.3 | Matthews-Blakeslee theory and experimental critical thickness data[35]                 | 14 |

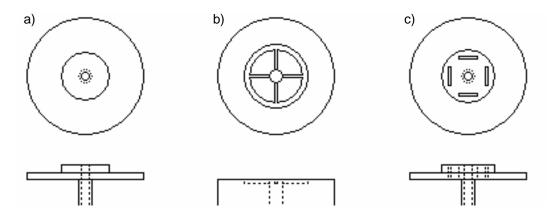

| 4.1 | Examples of layer structures for single layer, bilayer and multilayer groups.          | 18 |

| 4.2 | Trilayer structure                                                                     | 19 |

| 4.3 | Strain-relaxation of a trilayer structure vs layer thickness ratio                     | 20 |

| 4.4 | Schematic diagram demonstrating formation of a free-standing structure                 | 21 |

| 4.5 | Schematic diagram demonstrating a basic in-place bonding process                       | 23 |

| 5.1 | Schematic diagram of sample epitaxial layer structure                                  | 25 |

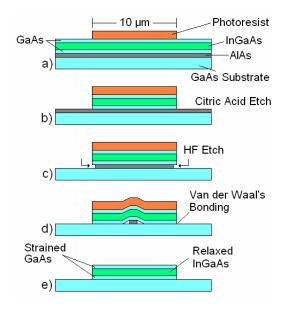

| 5.2 | Cleanroom fabrication process                                                          | 25 |

| 5.3 | Image of full mask pattern                                                             | 29 |

| 5.4 | Image of mask features                                                                 | 30 |

| 5.5 | Incident and diffracted Bragg angles for reflection planes parallel to the             |    |

|     | sample surface.                                                                        | 31 |

| 5.6 | Schematic diagram of X-ray system with relevant angles defined                         | 31 |

| 5.7 | Diagram of an asymmetric grazing incident XRD measurement, planes on                   |    |

|     | the left hand side of the sample are not shown for clarity.                            | 32 |

#### LIST OF FIGURES

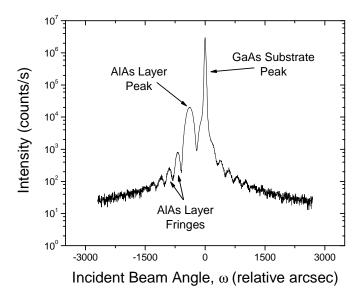

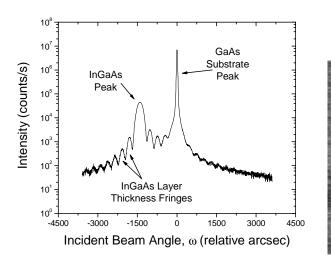

| 5.8                                                                                      | X-ray diffraction scan to demonstrate measurements of sample 5539                                                                                       | 33                              |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 5.9                                                                                      | AFM tip force diagram                                                                                                                                   | 36                              |

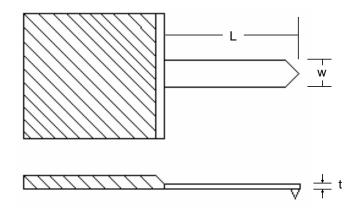

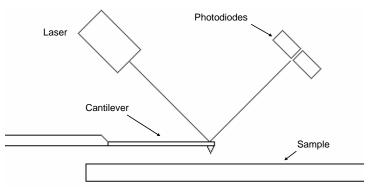

| 5.10                                                                                     | AFM cantilever                                                                                                                                          | 37                              |

| 5.11                                                                                     | Diagram of beam bounce deflection measurement method                                                                                                    | 38                              |

| 6.1                                                                                      | Single AlAs layer XRD scan (5507)                                                                                                                       | 41                              |

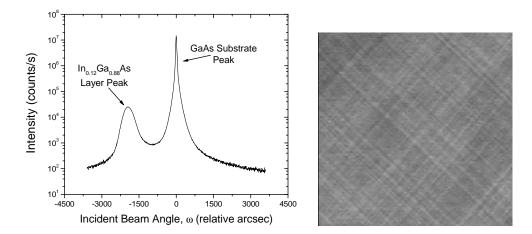

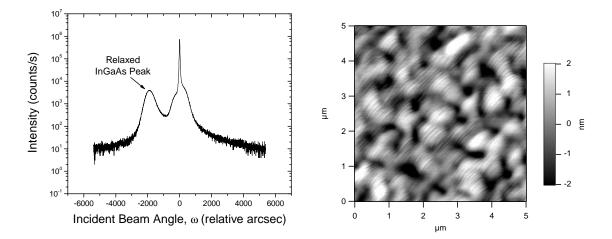

| 6.2                                                                                      | XRD and AFM data for single InGaAs layer                                                                                                                | 42                              |

| 6.3                                                                                      | XRD and AFM data for full layer structure sample from first batch                                                                                       | 43                              |

| 6.4<br>6.5                                                                               | AFM images of AlAs surfaces for varying growth conditions and substrates XRD and AFM data from sample 5539, a single strained $In_{0.078}Ga_{0.922}As$  | 45                              |

|                                                                                          | layer                                                                                                                                                   | 46                              |

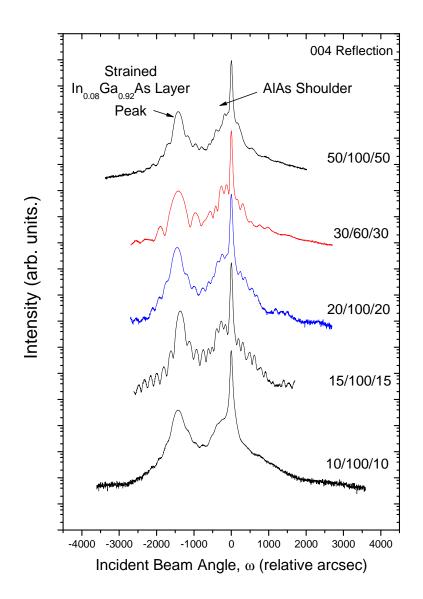

| 6.6<br>6.7                                                                               | Matthews-Blakeslee theory and experimental critical thickness data[35]<br>Rocking curves of 5543 (50/100/50), 5544 (30/60/30), 5561 (10/100/10)         | 48                              |

|                                                                                          | and 5562 (20/100/20)                                                                                                                                    | 49                              |

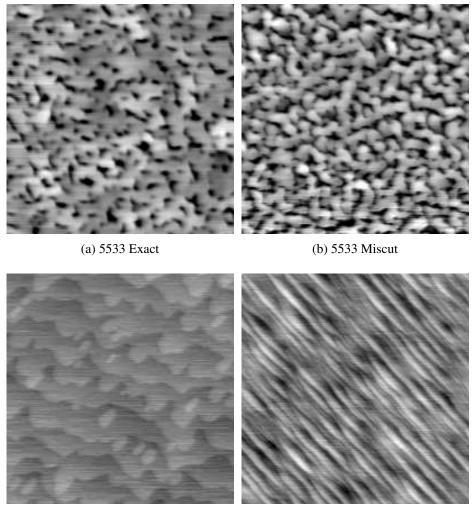

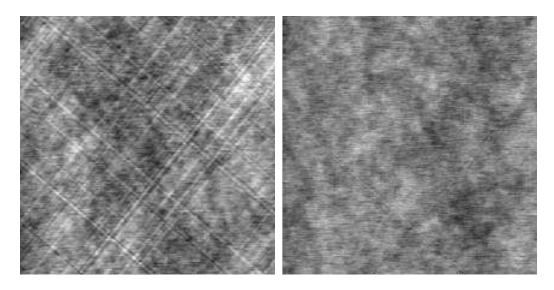

| 6.8                                                                                      | AFM scans of samples 5543 (50/100/50) and 5544 (30/60/30)                                                                                               | 50                              |

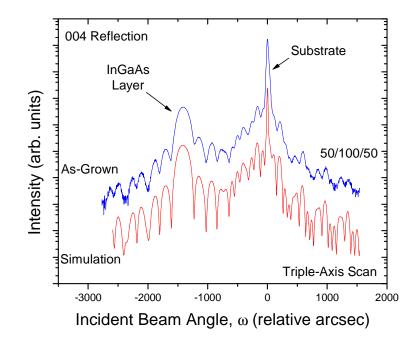

| 6.9                                                                                      | Comparison of measured and simulated scans for sample 5555 (50/100/50)                                                                                  | 51                              |

|                                                                                          |                                                                                                                                                         |                                 |

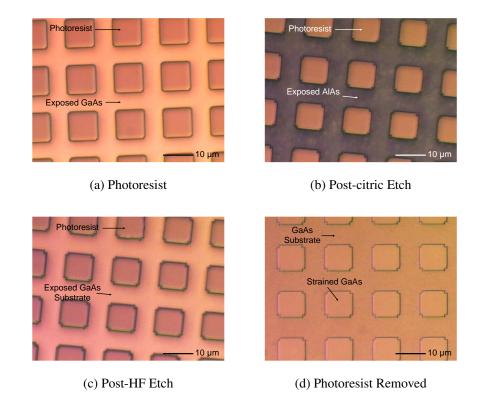

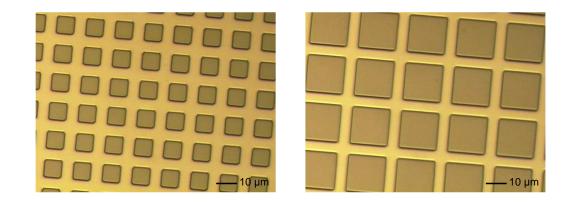

| 7.1<br>7.2                                                                               | Microscope photos of a sample at various stages of cleanroom fabrication<br>Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m | 54                              |

|                                                                                          | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m                                                                             | 54<br>55                        |

|                                                                                          | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m arrays                                                                      | 55                              |

| 7.2                                                                                      | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m arrays                                                                      |                                 |

| 7.2<br>7.3                                                                               | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m arrays                                                                      | 55                              |

| 7.2<br>7.3                                                                               | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m arrays                                                                      | 55<br>56<br>57                  |

| <ul><li>7.2</li><li>7.3</li><li>7.4</li></ul>                                            | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m arrays                                                                      | 55<br>56                        |

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> </ol>                           | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m arrays                                                                      | 55<br>56<br>57                  |

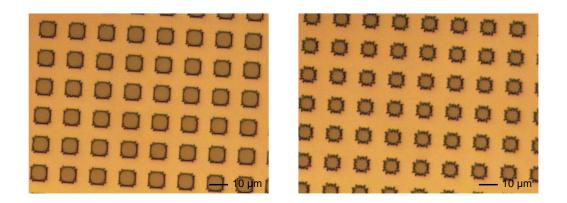

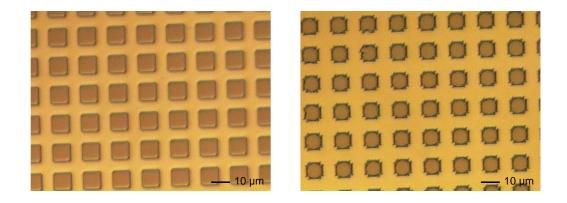

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> </ol>                           | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m arrays                                                                      | 55<br>56<br>57<br>58            |

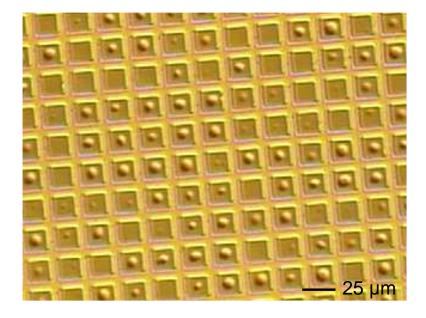

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ol>              | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m arrays                                                                      | 55<br>56<br>57<br>58            |

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> </ol>              | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m arrays                                                                      | 555<br>566<br>577<br>588<br>599 |

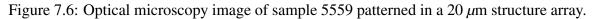

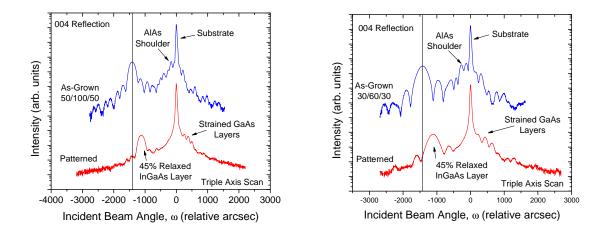

| <ol> <li>7.2</li> <li>7.3</li> <li>7.4</li> <li>7.5</li> <li>7.6</li> <li>8.1</li> </ol> | Whole wafer photo resist patterns, demonstrating both the 10 and 20 $\mu$ m arrays                                                                      | 555<br>566<br>577<br>588<br>599 |

#### LIST OF FIGURES

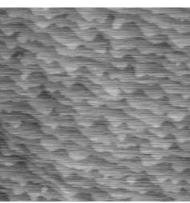

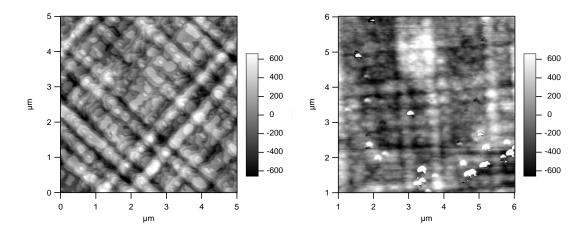

| 8.3 | AFM measurements of sample 5555 taken before (left) and after (right)           |    |

|-----|---------------------------------------------------------------------------------|----|

|     | processing. The dislocation density is 0.9 / $\mu$ m in both images             | 64 |

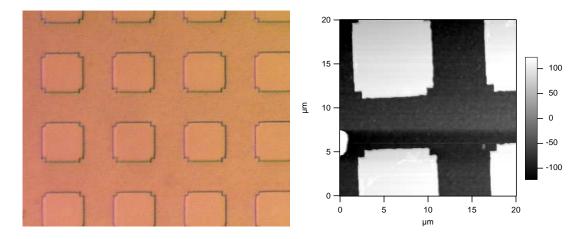

| 8.4 | Microscope and AFM images of sample 5555 patterned in a 10 $\mu$ m structure    |    |

|     | array                                                                           | 65 |

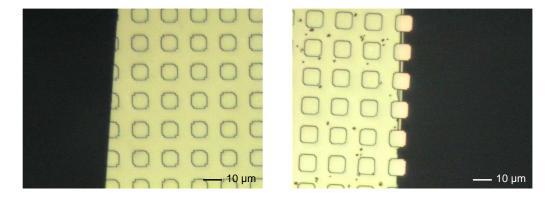

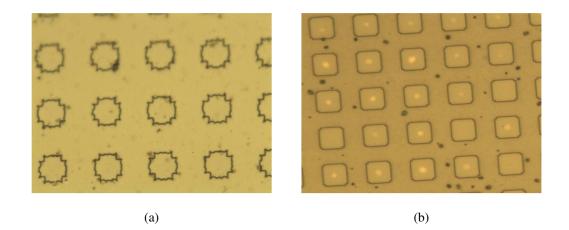

| 9.1 | Microscope pictures of annealed sample 5543 (left) and unannealed sample        |    |

|     | 5555 (right) (50/100/50)                                                        | 67 |

| 9.2 | Microscope pictures of annealed sample 5543 (left) and unannealed sample        |    |

|     | 5555 (right) after removal of upper GaAs layer and part of InGaAs layer.        |    |

|     | Light patches in the right picture are due to optical interference from the air |    |

|     | gap                                                                             | 68 |

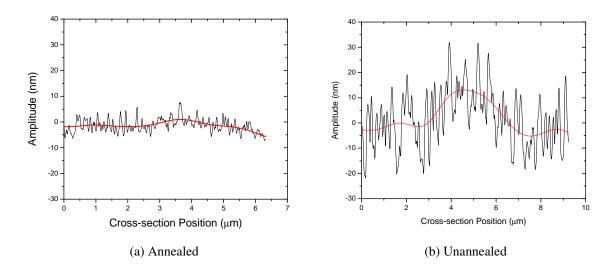

| 9.3 | AFM line scan across annealed and unannealed etched features                    | 69 |

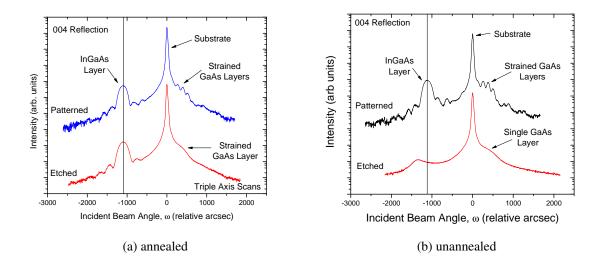

| 9.4 | XRD measurements of annealed sample 5543 before and after etching (left)        |    |

|     | and unannealed sample 5555 before and after etching (right)                     | 70 |

# Chapter 1

# Introduction

III-V semiconductor materials are compound semiconductors which contain elements from column III and column V of the periodic table, with a one-to-one ratio between the elements from each column. Silicon technology  $\approx 93\%$  of the market due to the low material cost, easy insulator integration in the form of SiO<sub>2</sub>, and higher hole mobility, which in turn leads to a lower logic circuit power consumption. However, III-V semiconductors in general possess a direct bandgap and a higher electron mobility than silicon. These advantages have led to considerable use of GaAs and other III-V materials in both high frequency electronics, such as power amplifiers in cellular phones, and photonic devices, such as light emitting diodes (LEDs)[3]. Additionally, many different III-V compounds are available, allowing a wide range of bandgap energies to be obtained by employing alloys, as demonstrated in Fig. 1.1. This extensive range of energies is particularly useful when attempting to engineer a semiconductor device which requires a specific bandgap. However, while determining which semiconductor material composition is required to obtain the necessary bandgap is simple, growing such a material of sufficient quality may be difficult. The small number of different high-quality crystalline III-V semiconductor substrates (GaAs, InP and GaSb) suitable for the epitaxial growth of such materials limits the range of heterostructures available for device applications. In an effort to expand the range of available substrate lattice parameters, there has been a substantial research effort to develop engineered substrates, which possess surface layers that have a different in-plane lattice constant than the underlying bulk semiconductor.

This research focuses on the in-place bonding method for creating engineered substrates

Figure 1.1: Bandgap energy and wavelength vs lattice parameter for various III-V alloys.

as first applied to III-V semiconductor materials. Chapters 2-4 are devoted to background material, dealing specifically with wafer bonding techniques, semiconductor mismatch and strain, and elastic strain relaxation. The following five chapters discuss fabrication processes, measurement methods, and results.

# Chapter 2

# Wafer Bonding

Wafer bonding is a process in which two wafers adhere to each other at room temperature without applying any manner of gluing layer material. This technique has been used to fabricate engineered substrates by thinning one wafer after bonding to achieve a thin layer of one material on a substrate of a different material. In general, the materials most often used in this process are semiconductor wafers, though metals, oxides and other chemical films have been bonded successfully using this method[17]. As the initial bonding is achieved at room temperature, it is weak compared to chemical bonding within solid crystals. Consequently a high temperature anneal is required to form covalent bonds at the interface before using the bonded material in device processing.

#### 2.1 Development of Wafer Bonding

In 1969 Wallis and Pomerantz reported the bonding of silicon wafers to glass wafers at an elevated temperature under an applied electric field. While this type of bonding is classified as anodic bonding, it served as a framework for later wafer bonding work accomplished in the mid-1980s by Shimbo *et al.* for direct Si-to-Si wafer bonding[39] and by Lasky for creation of silicon-on-insulator (SOI) wafers by wafer bonding[24]. In particular, the SOI technology was initially motivated by increased resistance to undesirable side effects caused by radiation-induced electron-hole pair production[41], as devices fabricated in the silicon layer are protected from the bulk silicon wafer by a silicon dioxide insulator. However, the most notable advantages of such technology became lower device operating voltages

and higher packing density of devices. While initial work dealt specifically with silicon technology, considerable research has also been carried out on bonding III-V semiconductor materials[18, 2, 1].

Wafer bonding is accomplished by bringing two clean, smooth wafers into contact. If the wafers are sufficiently smooth, their surfaces will experience a Van der Waals force attraction at the first point of contact. From this single point, neighbouring atoms will experience a similar attraction, causing the Van der Waals bonding to propagate across the surface of the wafer as the remainder of the wafer is brought into contact. This Van der Waals force is typically induced by one of three mechanisms: the dipole-dipole force between two polar molecules, the dipole induced force between a polar and nonpolar molecule, or the dispersion force between two nonpolar molecules due to temporary dipole moments. These three attractive mechanisms are created by chemical groups called bonding species.

While the required cleaning techniques for whole wafer III-V bonding are more complicated than the corresponding procedure in silicon technology, the means of bonding cleaned wafers remains very similar. However, there exists the additional complication of arsenic desorption when bonding GaAs wafers. In this case, arsenic atoms desorb from the wafer surfaces above 700°C [18], leading to gallium rich surfaces. Consequently, any wafer bonding anneal performed at such temperatures must be carried out in an arsenic rich atmosphere.

#### 2.2 Merits of Wafer Bonding

The refinement and use of the wafer bonding technique led to advances in two major areas: electronic devices and mechanical devices. For electronic device manufacturing, the primary advances came as a result of bonded SOI wafers, which could be cheaply and efficiently produced. These new wafers provided significant layer quality advantages over previous methods in which either amorphous silicon was grown on an oxide layer or an oxide layer was formed beneath an existing high quality silicon layer by high-energy oxygen implantation, known as separation by implanted oxygen (SIMOX)[41]. In the former case, the new silicon layer was not crystalline, and in the latter case, the implantation process resulted in an increased dislocation density. For microelectromechanical (MEMs) devices, wafer bonding was of particular importance in the development and production of semiconductor devices which required thin cantilevers or diaphragms. In particular, this led to pressure sensors and accelerometers of much smaller size than those designed prior to advances in wafer bonding technology.

In addition to these well established advances, wafer bonding technology has the potential to provide the means of achieving the integration of optical devices fabricated from III-V materials with silicon integrated circuit technology, providing new types of optoelectronic integrated circuits (OEICs)[41], an advance that would greatly benefit optical-fiber communications. Furthermore, wafer bonding technology may provide new material combinations or buried layers[41].

#### 2.3 Wafer Bonding Complications

While semiconductor wafer bonding might seem like an ideal means of joining two semiconductor materials without introducing a bonding agent, there are a number of complications which may arise from improper preparation of the sample, or poor choice of bonding or annealing conditions. Unbonded interface areas are one of the most common problems in wafer bonding methods; these voids or bubbles can form during the bonding process, storage or an anneal[41]. An example of such an unbonded area is shown in Fig. 2.1. Efforts to understand and eliminate these bubbles have found the causes of their formation during bonding to include: particles on the bonding surfaces, locally rough bonding surface areas, locally low density of bonding species, and trapped air pockets. The bonding species are the specific chemical groups terminating the surface that act as a catalyst for bonding. In the first case, bubbles form as the particles prevent a good bond from forming in the locality of the particle simply by keeping the two wafer bonding surfaces apart. Larger particles result in larger bubbles. Local roughness of the bonding wafers causes bubbles as the surfaces do not lie smoothly together, in this case the bubbles may simply be pits sealed by the wafer bonding process, which creates a void at the interface. Similarly, bubbles formed during either storage or annealing are typically created by: the reaction of interface bonding species and bonding materials (notably hydrogen release, as many wafer bonding processes utilize hydrogen terminated surfaces), the dissociation of bonding groups on the bonding surface, or the outgassing from contaminants either on or within the bonding materials[41].

The above list of causes demonstrates the importance of surface quality in the wafer

Figure 2.1: Infrared micrograph of whole wafer GaAs-GaAs bonding showing an unbonded region[2].

bonding process. Thus, the surfaces of the wafers to be bonded must possess sufficient smoothness, flatness, cleanliness and reactivity to prevent bubble formation during the bonding process. In silicon bonding this is a relatively simple process, with chemomechanical polishing providing a sufficiently smooth surface without creating any subsurface damage[36] and a standard RCA clean to remove any surface contaminants[22]. However, surface cleaning is more complicated when applied to III-V semiconductors such as GaAs, as the removal of both the Ga and As oxides must be synchronized, and a simple cleaning solution, such as the RCA clean used in silicon technology, does not exist. Furthermore, any wafer surface which has been exposed to air will additionally contain both carbon contaminants and absorbed water[2]. While the water can be thermally removed at low temperatures and any native oxides can be desorbed by heating up to 580°C, thermal cleaning cannot remove carbon contaminants completely, and furthermore, it causes increased surface roughness [42] and impurity accumulation. A number of different cleaning mechanisms have been investigated including electron plasma cyclotron resonance[43] and atomic hydrogen cleaning[2], both of which provide a better final surface than methods similar to those used in silicon cleaning. The second method has been applied to a variety of different III-V materials successfully[1].

#### 2.4 Wafer Bond Strength Tests

The strength of a bonded wafer pair can be defined as the work, W, per unit area associated with the mechanical separation of the pair of bonded surfaces from their original distance at contact,  $d_0$ , to infinity under adiabatic conditions as given by equation 2.1

$$W = \gamma_1 + \gamma_2 = \int_{d_0}^{\infty} F(x) dx, \qquad (2.1)$$

where  $\gamma_1$  and  $\gamma_2$  are the surface energies per unit area of surface 1 and surface 2 at the moment of separation, x is the separation of the two wafers and F(x) is the attraction force per unit area as a function of the separation of the surfaces. The standard method of measuring the surface energy of the bonded wafers is the crack-opening method[27, 41] shown in Fig. 2.2. In this case, when a separating material, such as a razor blade with thickness  $t_b$ , is in-

Figure 2.2: Schematic diagram of the crack-opening method of determining the surface energy of a bonded pair. The separation of the two wafers, x is equal to the thickness of the razor blade  $t_b$  at the point where the razor is contacting the wafers.

serted between the two wafers, each will bend, and generate a corresponding elastic energy,  $E_{Elas1}$  and  $E_{Elas2}$  respectively, given by

$$E_{Elasi} = \frac{E_i w t_i^2 t_b^2}{8L^3},\tag{2.2}$$

where  $E_i$  is the Young's modulus and  $t_i$  is the the thickness of each wafer. Additionally, the insertion of the blade between the wafers introduces two new surfaces of area Lw, where w is the width of the bonded area (into the page) and L is the crack length. Thus, the total energy for the system is given by

$$E_{total} = E_{Elas1} + E_{Elas2} + (\gamma_1 + \gamma_2)Lw.$$

(2.3)

In the equilibrium case where the first derivative of  $E_{total}$  with respect to L is zero, the surface energy, or bond strength, can be found by

$$W = \gamma_1 + \gamma_2 = -\frac{3t_b^2 E_1 t_1^3 E_2 t_2^3}{8L^4 (E_1 t_1^3 + E_2 t_2^3)}$$

(2.4)

for the case of differing materials and thicknesses in the bonded pair[41]. This method remains one of the primary methods of determining the bond strength following wafer bonding. It has been used in whole wafer GaAs/GaAs bonding and demonstrates that such bonded interfaces can achieve bond energies of  $\sim 0.7$ -0.8 J/m<sup>2</sup>, which is close to that of the bulk material[18]. However, this bond testing method is limited strictly to cases where a razor blade or other narrow object may be easily inserted between the bonded layers.

#### 2.5 Summary

Wafer bonding provides a means of obtaining an interface between different materials. This method avoids the introduction of dislocations and the materials involved may not experience strain as a result of the bonding as the bonding can occur at room temperature in some cases. However, this method is limited in possible layer structures to those which may be fabricated on whole wafers and unbonded areas may be present if bonding conditions are not ideal. The traditional method of measuring the bond strength of a wafer bond involves the use of a razor to separate the bonded wafers, with the bond strength defined as the sum of the two surface energies of the wafers.

# Chapter 3

# Semiconductor Mismatch, Strain & Defects

When growing semiconductor layers of different lattice parameter than that of the substrate, their quality, and thus their usefulness in electronic materials is limited by their critical thickness. The critical thickness of a material is defined as the point at which misfit dislocations within the crystal lattice of the epitaxial layer begin to propagate throughout the lattice. Misfit dislocations form to accommodate the mismatch strain created by a heterostructure containing layers of different lattice parameters.

#### **3.1** Mismatch Strain

Because the lattice constant of InAs is larger than that of GaAs, the alloy  $In_xGa_{1-x}As$  has a larger lattice constant than GaAs and a smaller lattice constant than InAs. This lattice constant can be estimated by use of Vegard's law

$$a_{InGaAs} \approx xa_{InAs} + (1 - x)a_{GaAs}, \tag{3.1}$$

where  $a_{GaAs} = 0.5653$  nm, and  $a_{InAs} = 0.6062$  nm, the lattice constants. This law assumes a linear relation, which for InGaAs, is a good approximation. Consequently, when a layer of In<sub>x</sub>Ga<sub>1-x</sub>As is grown on a GaAs wafer, there is a lattice mismatch dependent on x, the InAs fraction of that layer. This lattice mismatch produces a strain in the plane of the layer

$$\varepsilon_0 = \frac{a_s - a_l}{a_l},\tag{3.2}$$

This can be rewritten in terms of the Indium composition by substituting equation 3.1 into 3.2 yielding

$$\varepsilon_0(x) = \frac{a_{GaAs} - (xa_{InAs} + (1 - x)a_{GaAs})}{(xa_{InAs} + (1 - x)a_{GaAs})} = \frac{x(a_{GaAs} - a_{InAs})}{a_{GaAs} - x(a_{GaAs} - a_{InAs})}.$$

(3.3)

When inserting the lattice constants of GaAs and InAs, this yields a mismatch strain of  $\varepsilon_0 \approx -0.071x$ .

The layer stress in the plane of the interface can be written as[12]

$$\sigma = 2\mu\varepsilon_0 \frac{1+\nu}{1-\nu} \tag{3.4}$$

and the strain normal to the interface is given by

$$\varepsilon = \frac{-2\nu\varepsilon_0}{1-\nu} \tag{3.5}$$

where the elastic shear modulus,  $\mu = 32.6$  GPa, and Poisson's ratio,  $\nu = 0.31$ , for GaAs[40]. The elastic energy per unit of interface area produced by this mismatch strain is

$$E = \frac{2\mu h(1+\mathbf{v})\varepsilon_0^2}{1-\mathbf{v}}$$

(3.6)

where *h* is the thickness of the strained layer[12]. Equations 3.3 and 3.6 collectively allow for the calculation of stored elastic energy within an  $In_xGa_{1-x}As$  layer for a given *x*. When the stored energy exceeds a critical value, the critical thickness, the energy is relaxed by the formation of misfit dislocations.

#### 3.2 Dislocations in III-V Semiconductors

A dislocation is a line defect found in crystalline materials. Figure 3.1 demonstrates the two basic types of dislocation: edge dislocations and screw dislocations. In the image each vertex can be considered as an atom in the crystal lattice. Edge dislocations occur when a half plane of atoms is missing among full planes, leaving the edge of the remaining half

plane unbonded to atoms in one direction and distorting the crystal lattice as a result. An example of an edge dislocation is shown in Fig. 3.1(a). This image represents a single plane of a material containing an edge dislocation line that lies perpendicular to the page. Screw dislocations occur where a portion of a bulk crystal is offset by one or more atoms as shown in fig. 3.1(b). The screw dislocation line is perpendicular to the face of the crystal, and parallel to the Burgers vector. However, this is a simplistic view of dislocations and those found in semiconductors often contain components of both edge and screw dislocations. Consequently a system of identifying different types of dislocations is necessary, and this is accomplished by the Burgers vector and Burgers circuit[19].

Figure 3.1: Schematic diagram of an edge dislocation and a screw dislocation in a bulk crystal. The respective Burgers circuits and vectors are indicated for each dislocation.

The Burgers circuit is simply a closed atom to atom path taken in a crystal containing no dislocations, as shown in Fig. 3.1. If the same path taken in a crystal containing dislocations does not close, then the path encloses one or more dislocations. The resulting vector that is required to close the loop is called the Burgers vector,  $\vec{b}$ . For the basic dislocation types, the Burgers vector is normal to the dislocation line for edge dislocations, and parallel to the dislocation line for screw dislocations. It is of particular importance to note that the Burgers vector of a dislocation is always the same, independent of the location of the dislocation within the medium.

Once a dislocation is contained within a crystal, it may move in two primary ways: glide

and climb. Glide occurs along slip planes which are planes within the crystal along which plastic deformation is most likely to occur, and which are generally planes with the highest density of atoms. The direction of the glide is typically in the direction where the atoms are most closely spaced. Climb occurs when a dislocation moves out of its current slip plane and into another slip plane. Climb is primarily driven by vacancies in the crystal lattice and, consequently, occurs more rapidly at higher temperatures. Climb does not usually occur at the temperatures typically used for growth of InGaAs epitaxial layers.

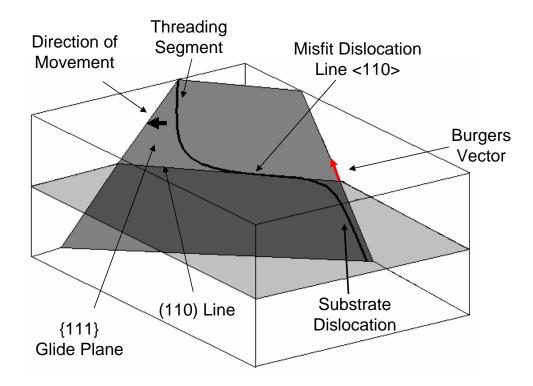

In all diamond or zinc blende crystal structures, the lowest energy slip planes are the {111} planes, and consequently, on <001> oriented substrates the slip planes intersect the interface in <110> lines, which provides the corresponding line directions of misfit dislocations in such structures, as shown in Fig. 3.2. The Burgers vectors of such dislocations is the slip direction and these can be along the line or in the glide plane at 60° to the line direction. However, in the first case, the misfit dislocation is a screw dislocation and relieves no misfit strain. The component of the 60° dislocations perpendicular to the line direction contributes to strain relaxation. Total strain relaxation depends on the number of dislocations per unit length perpendicular to the direction of strain relaxation i.e. those perpendicular to the <110> lines. The 60° Burgers vector is  $\vec{b} = \frac{a_l(1\bar{1}0)}{2}$  in a zinc blende crystal, and has a length along the interface perpendicular to the line of  $b_{\perp} = \frac{a_l}{2\sqrt{2}}$  [12]. For an InAs alloy fraction 0.08 the length of the Burgers vector,  $\vec{b}$ , is 0.20 nm.

#### 3.3 Critical Thickness Behaviour

Initial work on the critical thickness of semiconductor materials was published by Matthews and Blakeslee[29, 30, 31], who determined a mathematical relation for the critical thickness by examining the forces originating from both the misfit strain,  $F_{\varepsilon}$ , and the tension of the dislocation line,  $F_l$ . For cases where the elastic constants of two layers are equal and isotropic, then

$$F_{\varepsilon} = \frac{2\mu(1+\nu)}{(1+\nu)}bh\varepsilon\cos\lambda$$

(3.7)

where  $\mu$  is the shear modulus of the strained layer in question, v is the Poisson ratio, h is the thickness of the strained layer and  $\lambda$  is the angle between the slip direction and the direction perpendicular to the line of intersection of the slip plane and the interface.

Figure 3.2: The orientation of the glide plane in GaAs/In<sub>x</sub>Ga<sub>1-x</sub>As structures. Misfit dislocation and corresponding Burgers vector are shown. The (110) line is the intersection of the 111 glide plane with the (001) plane.

Similarly, the tension due to the dislocation line is

$$F_l = \frac{\mu b^2}{4\pi (1-\nu)} \left( (1-\nu \cos^2 \alpha) (\ln \frac{h}{b} + 1) \right)$$

(3.8)

where  $\alpha$  is the angle between the dislocation line and its Burgers vector.

The critical thickness,  $h_c$  is defined as the point at which the threading segment of a dislocation begins to glide as shown in fig. 3.2, and occurs when the misfit strain force,  $F_{\varepsilon}$ , is larger than the dislocation line tension force,  $F_l$ . And thus, at the critical thickness,  $F_{\varepsilon_{max}} = F_l$ , and the layer thickness is given by

$$h_c = \frac{b}{8\pi\epsilon} \frac{(1 - \nu \cos^2 \alpha)}{(1 + \nu) \cos \lambda} (ln \frac{h_c}{b} + 1)$$

(3.9)

In the case of GaAs-In<sub>x</sub>Ga<sub>1-x</sub>As, v = 0.31,  $b = a_l/\sqrt{2}$ ,  $cos(\lambda) = 1/2$  and  $cos(\alpha) = 1/2$ [40]. For the samples grown for these experiments, the InAs alloy composition, *x*, is 0.08 resulting in a critical thickness,  $h_c$ , of 22 nm.

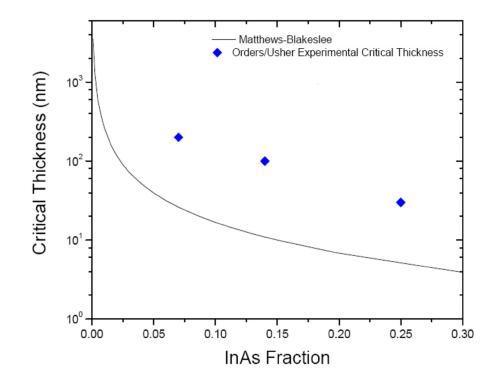

Figure 3.3 shows the critical thickness of  $In_xGa_{1-x}As$  for varying Indium concentration calculated from eq. 3.9. The experimental critical thicknesses (diamonds) were determined

Figure 3.3: Plot of Matthews-Blakeslee theory (equation 3.9) and experimental data points for the critical thickness of various InAs % samples as measured by x-ray diffraction are also shown (diamond)[35].

by measuring the perpendicular lattice spacing by x-ray diffraction and determining the point at which the lattice spacing began to shift, indicating the relaxation of strain[35]. Layers with thicknesses between the points and line may experience movement of dislocations within the material, however the misfit dislocation density is not sufficient to relieve enough strain to observer a detectible shift in the lattice parameter.

However, Freund[12] lists specific limitations of the Matthews-Blakeslee Criterion,

namely that it:

- Provides the point at which any threading segment may advance, and thus, relaxation may not be detected at this point unless the method of observation provides sufficient resolution to detect the change in strain caused by a single dislocation. Therefore large area measurement techniques such as X-ray diffraction (XRD) will not detect the relaxation caused by a single dislocation as they measure average strain over areas on the order of a square millimeter.

- 2. Assumes a dislocation exists, and thus, neglects the nucleation of new dislocations. In the case of GaAs, the initial wafers contain  $\approx 2 \times 10^3$  dislocations/cm<sup>2</sup>.

- 3. Only indicates the tendency for a threading segment to move, but does not specify the manner of dislocation movement. This means a kinetic model of glide is required to take the movement of dislocations into account when considering critical thickness and relaxation.

- 4. Examines the case of only a single dislocation in a uniform layer, and assumes that no other dislocations are present.

- 5. Neglects entirely the effects of glide resistance, surface or interface energy, and surface ledge creation resistance[28, 6], since the criterion is based solely on elastic continuum concepts.

From #1 it is not surprising that the experimental critical thickness as measured by x-ray diffraction is greater than that predicted by the mechanical equilibrium model of Matthews-Blakeslee. This also indicates that although samples grown with thickness below the experimental data of the Orders/Usher experiment should not experience a significant change of the perpendicular lattice spacing[35], there are misfit dislocations present.

#### **3.4** Summary

The difference in the lattice parameters of a semiconductor layer compared to that of the substrate results in strained epitaxial layers. At the critical thickness, this strain begins to relax through movement of dislocations. The critical thickness of the samples used in this

experiment is 22 nm as calculated by the Matthews-Blakeslee equation, 3.9. The experimental critical thickness which is determined from measurements of the lattice constant of an epitaxial layer made by XRD[35] is larger than predicted by Matthews-Blakeslee since this technique is limited in sensitivity, as suggested by Freund[12].

# Chapter 4

# **Elastic Strain Relaxation**

When engineering semiconductor devices, it may be desirable to obtain a relaxed or strained layer of semiconductor material without creating dislocations. Several different methods have been used to achieve such layers, including compliant substrates [46, 47] and sacrificial sublayers[37]. This chapter will review the physics of elastic strain relaxation and the use of the two methods mentioned in obtaining elastically strain relaxed materials.

#### 4.1 **Physics of Elastic Strain Relaxation**

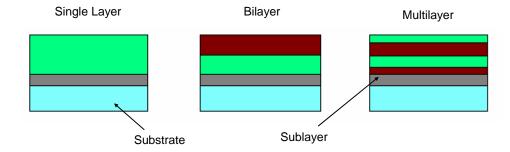

Elastic strain relaxation is strain relaxation that is reversible, and does not introduce dislocations. There are several different methods for achieving elastic strain relaxation, each of which relies on the use of a special sublayer to obtain the desired relaxation. This sublayer is either a compliant layer or a sacrificial layer to be etched away. In each case, the relaxation of the semiconductor material is dictated by the layer structure that was grown on top of the sublayer. While there are limitless layer structures which can be grown, their relaxation behaviour can be broadly classified into three groups: single layer, bilayer and multilayer as shown in Fig. 4.1. The single layer structure consists of a strained semiconductor layer grown on the sublayer. In this case the layer will optimally relax one hundred percent and is limited only by the choice of the method used to cause elastic strain relaxation.

The bilayer structure consists of two layers with a different lattice constant. Typically one layer is strained and the other layer is lattice matched to the substrate. Following the strain relaxation treatment, the two layers share the strain between them. This can result in

Figure 4.1: Examples of layer structures for single layer, bilayer and multilayer groups.

bending in a manner similar to that of a bimetallic strip if the relaxation method allows for bending. The curvature of a free-standing bilayer bending in one dimension is given by

$$\kappa = \frac{6E_1E_2(t_1+t_2)t_1t_2\varepsilon_0}{E_1^2t_1^4 + 4E_1E_2t_1^3t_2 + 6E_1E_2t_1^2t_2^2 + 4E_1E_2t_2^3t_1 + E_2^2t_2^4}$$

(4.1)

where  $E_1$  and  $E_2$  are Young's modulus of the two materials,  $\varepsilon_0$  is the mismatch, and  $t_1$  and  $t_2$  are the corresponding thicknesses. However, this is a simplified model, since depending on the mechanism used to induce elastic strain relaxation and the shape of the structure experiencing relaxation, the layers may curve in two directions (as a dome would); may not curve at all and instead relax according to the force-balance model discussed below[45]; or may relax under some combination of these mechanisms. While bilayer systems may seem unpredictable, it should be noted that, for any given layer structure, the forces, and thus the relaxation behaviour, remain the same in identical samples.

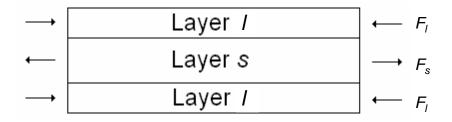

A multilayer system requires a more complicated model for strain relaxation. However, in the case of a trilayer system as depicted in Fig. 4.2 the relaxation model is simple. In this case the top and bottom layers are of equal thickness, which provides equal magnitude bending forces on both the top and bottom of the middle layer and the bending forces cancel out. This force-balance model, discussed by both Mooney et al. and Freund & Suresh [34, 13], is a model to determine the proportion of mismatch strain that each layer of the structure holds. In the case shown in Fig. 4.2 the mismatch strain between the two materials can be calculated from equation 3.3. The balance of strain between the layers is given by

$$\varepsilon_l - \varepsilon_s = \varepsilon_0 \tag{4.2}$$

where  $\varepsilon_l$  and  $\varepsilon_s$  are the elastic strain contained in layers l and s, and the stresses associated

Figure 4.2: Trilayer structure with identical thickness layers *l* and single layer *s*. The forces are denoted and given by  $F = \frac{P}{A}$ , where P is the pressure and A is the cross-sectional area.

with them are  $\sigma_l = M_l \varepsilon_l$  and  $\sigma_s = M_s \varepsilon_s$ , where  $M_l$  and  $M_s$  are the biaxial moduli for the materials comprising the two layers. Furthermore, as the structure is at equilibrium, the net force on any cross-section must be zero, consequently

$$2\vec{F}_l + \vec{F}_s = 0 \tag{4.3}$$

$$2M_l \varepsilon_l t_l + M_s \varepsilon_s t_s = 0 \tag{4.4}$$

where  $t_l$  and  $t_s$  are the thicknesses of the respective layers. In this case, equal thicknesses of the *l* layers will cause the net bending forces to cancel, and thus, by combining equations 4.2 and 4.4 the following relations can be obtained for the elastic strain in each layer

$$\varepsilon_l = -\varepsilon_0 \frac{t_s M_s}{2t_l M_l + t_s M_s}, \ \varepsilon_s = \varepsilon_0 \frac{2t_l M_l}{2t_l M_l + t_s M_s} \tag{4.5}$$

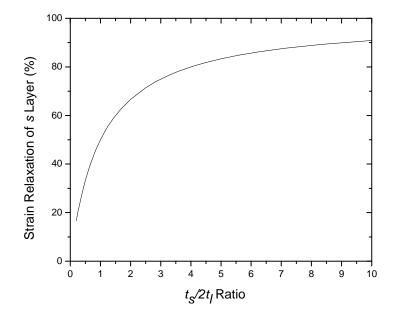

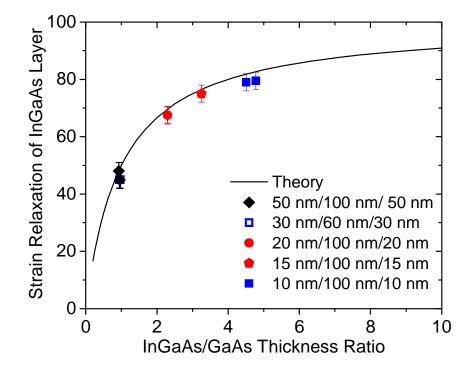

Consequently, for such a structure, the percentage of initial mismatch strain contained within the center layer after the structure has reached equilibrium is easily calculated. Figure 4.3 shows the strain relaxation of layer s as a function of the layer thickness ratio,  $t_s/2t_l$ .

#### 4.2 Elastic Strain Relaxation using a Compliant Substrate

The use of a compliant substrate as a possible means of elastically relaxing strained thin films was first proposed by Lo [26], and has been successfully used more recently to achieve strain-relaxation in Si/SiGe structures by Yin *et al.* [46, 47]. Yin's work utilized a borophosphorosilicate glass (BPSG) on a Si substrate as a compliant film onto which strained pseudomorphic SiGe films were transferred by wafer bonding. The films were then patterned

Figure 4.3: Percentage of strain-relaxation occurring within the center layer of a trilayer structure, as shown in fig. 4.2, for different thickness ratios.

into islands of various sizes. The BPSG is initially viscous and consequently the strained SiGe films remain strained following transfer; however, the viscosity of the BPSG drops rapidly when samples are heated above 750 °C allowing the SiGe film to relax as the compliant layer may now flow. It was noted that small islands of SiGe tended to relax laterally as intended, but larger areas frequently relaxed by buckling, which greatly increased the surface roughness of the SiGe film[46]. Additionally, small islands relax faster than large islands. As relaxation occurs, the lattice spacing between the strained atoms either increases (for initially compressively strained layers), or decreases (for initially tensilely strained layers). Since the strained layers are expanding over a fluid-like layer, the rate of expansion is limited by the viscosity of the compliant substrate. Thus, larger islands will take longer to expand, and therefore, relax due to the larger migration of the island edge required to achieve the same net shift in lattice parameter. While the buckling was eliminated through the use of a cap layer, the processing steps required to achieve smooth large areas required a combination of repeated etchs and long anneal times[45]. The compliant substrate method can also be employed to provide uniaxial in-plane strained layers[47]. As the speed at which strain relaxation occurs is dependent on the size of a feature as discussed above, uniaxial relaxation was accomplished by use of rectangles rather than squares as the shape of the island. However, applying this mechanism to III-V materials has shown a considerable increase in the rms surface roughness of films wafer bonded to BPSG compared to those grown epitaxially on lattice matched substrates[16].

#### 4.3 Elastic Strain Relaxation using a Sacrificial Layer

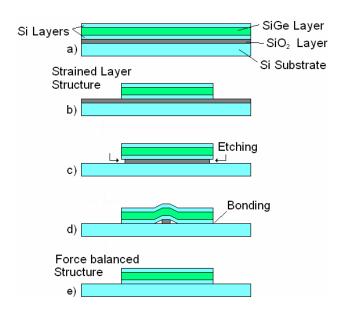

There are three main techniques for achieving elastic strain relaxation when using a sacrificial sublayer: free-standing structure formation, layer liftoff and in-place bonding. Formation of free-standing structures has been used in both SiGe/Si and III-V semiconductor structures [34, 21]. Principally, it employs a controlled etch of a sacrificial sublayer to cause the strained layer structure to be supported above the substrate by a pillar created from the sacrificial sublayer as shown in Fig. 4.4[33]. In this case, the conditions must be

Figure 4.4: Schematic diagram demonstrating formation of a free-standing structure.

such that the supported layer structure does not remain in contact with the substrate following etching. This is typically accomplished by a combination of parameters, including a stiff supported structure and a thick sacrificial layer. The layer will relax as discussed in 4.1. Due to the nature of the mechanism, a bilayer structure is unsuitable for this type of strain relaxation as bending can freely occur and, consequently, the layer structure subject to bending forces will not be flat. Single layer membranes fabricated in this way have been used for regrowth both with[21] and without[33] prior reinforcement of the pillar.

Layer liftoff is a process involving the complete removal of the sacrificial layer. This allows the strained layer structure to detach from the substrate in the etch solution[37]. The structure is then able to relax as described in section 4.1. A sufficiently thick sacrificial layer prevents the layer from adhering to the substrate during the etch process. The floating layer can then be attached to any new substrate, including those on which semiconductor crystals cannot be grown.

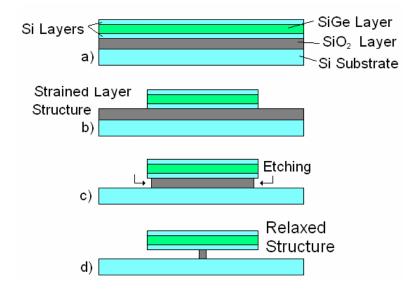

The final method to be discussed that involves a sacrificial layer is in-place bonding[8]. The in-place bonding method is similar to that of layer liftoff, but with the notable difference that the strained layer structure relaxes and then weakly bonds in-place on the substrate. Presently, it is believed that this method may only be used in a water based etchant bath (i.e., most typical acids) and only with hydrophobic material surfaces, as initial work demonstrated that the method failed when hydrophilic surfaces were used[8]. A schematic diagram showing the basic in-place bonding method is shown in Fig. 4.5. Initially, blanket epitaxial SiGe and Si layers were grown on a silicon-on-insulator substrate(Fig. 4.5(a)). Structures were then fabricated by photolithography and etching (Fig. 4.5(b)). The sacrificial SiO<sub>2</sub> sublayer was then removed (Fig.4.5(c)), and during etching, the strained layer relaxed and experienced a hydrophobic attraction to the substrate (Fig.4.5(d))[25]. Finally, when the sample was removed from the etchant bath, strain-relaxation had occurred as described above and the Si/SiGe/Si structure was weakly bonded to the substrate (Fig.4.5(e)). An 800°C anneal was performed to strengthen the bond. This final method was used as a basis for the design of the in-place bonding experiment described in this thesis.

Figure 4.5: Schematic diagram demonstrating a basic in-place bonding process.

## Chapter 5

# **Experiment Overview and Measurement Techniques**

This chapter will discuss in detail the experiments performed for this thesis. In particular it will discuss the procedure used and justify the choices made throughout that procedure, including etchant selection and mask design. Furthermore, a discussion of the underlying physics of the methods used to analyze the samples is presented.

## 5.1 Description of Experiment

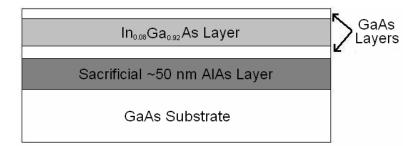

The objective of this work was to determine if the in-place bonding method demonstrated in SiGe/Si[8] can be applied to III-V semiconductor materials. This will primarily provide a suitable base technique for further exploration of strain-relaxed engineered substrates in III-V materials. GaAs and InGaAs were chosen as materials since there is an interest in obtaining high quality InGaAs layers, which are usually grown on InP substrates on GaAs substrates, because of the lower cost of GaAs substrates. A GaAs/InGaAs layer structure was chosen as GaAs substrates possess a suitable sacrificial layer, AlAs, which has a lattice parameter close to that of GaAs. The layer structures shown in Fig. 5.1 were grown on GaAs(001) wafers by metal-organic chemical vapour deposition (MOCVD). Since AlAs is essentially lattice matched to GaAs, this layer is unstrained. However, as the lattice constant of the In<sub>0.08</sub>Ga<sub>0.92</sub>As layer is 0.6% larger than that of the substrate, the In<sub>0.08</sub>Ga<sub>0.92</sub>As layer

#### CHAPTER 5. EXPERIMENT OVERVIEW AND MEASUREMENT TECHNIQUES 25

Figure 5.1: Schematic diagram of sample epitaxial layer structure

will be compressively strained, as described in section 3.1. The samples were analyzed with X-ray diffraction (XRD) to determine the alloy composition, the strain, and the layer thickness. Atomic force microscopy (AFM) was used to determine the roughness of each sample. Following this initial characterization, the samples were patterned by conventional optical lithography and etched in a cleanroom environment as shown in Fig. 5.2 to allow the strained layer structure to relax elastically and to achieve in-place Van der Waals bonding.

Figure 5.2: Schematic diagram of the cleanroom fabrication process for in-place bonding of a InGaAs/GaAs layer structure.

After the samples were processed, they were analyzed with the aforementioned methods to determine: a) if elastic strain relaxation had occurred, b) if in-place bonding occurred, and c) if significant roughening of surfaces had occurred, which could impact the usefulness of this technique in future experiments. Since elastic strain relaxation has in fact occurred, then select samples will be annealed to improve the bond strength. It should be noted, that while this work is focused on transferring a technique from one set of materials to another, the technique, in itself, is very new and not entirely understood.

### 5.2 Etchant Chemistry and Behaviour

Etchant selection is very important in any experiment involving different materials and small features. In general, this involves choosing etchants with appropriate etch rates for the desired materials. Selectivity becomes particularly important and is expressed by the ratio of the rates at which the etchant removes two different types of material. In the case of this particular experiment, the samples contain a trilayer structure comprised of a GaAs layer, an InGaAs layer and a GaAs layer as shown in Fig. 5.1. This structure limits the choice of etchants to either a single one with equal etch rates for both the GaAs and the InGaAs layers, or two etchants with high selectivity between the GaAs and InGaAs layers, as etching both materials at unequal rates may change the geometry, and thus the relaxation of the layer structure. The potentially small indium alloy composition of the InGaAs layer indicates that an equal rate etch will provide the most accurate etch. Additionally, this structure sits upon a sacrificial AlAs layer which must be removed without damaging the trilayer structure described above. Consequently, at least two etchants are needed for this experiment, one to etch through the structure, and one to remove the sacrificial layer.

Chemical etching in most III-V semiconductor materials proceeds by an oxidationreduction reaction at the semiconductor surface, followed by dissolution of the oxide material, resulting in the removal of the semiconductor material[3]. This is generally accomplished through the use of an acid mixed with an oxidizing agent such as hydrogen peroxide  $(H_2O_2)$ . Etchants are additionally classified into two broad categories: reaction rate limited and diffusion limited. Reaction rate limited etchants have a constant etch rate, the amount of material removed is linearly proportional to the etching time, unaffected by agitation of the etchant, faster at higher temperatures, and susceptible to large changes in etch rate caused by small changes in the proportions of the etchant components. Diffusion-limited etchants remove an amount of material proportional to the square root of the etch time, experience an etch rate increase when agitated, and possess temperature independent etch rates[9]. Because the various samples to be grown for this experiment have different layer thicknesses, a reaction rate limited etchant is preferable because the etch rate is more easily predicted and would be consistent for all layer thicknesses. However, the measurement and mixing of such an etchant must be done carefully to achieve consistent etch rates.

DeSalvo performed considerable characterization of a citric acid/hydrogen peroxide  $(C_6H_8O_7:H_2O_2)$  etch, and showed that at a volume ratio of 3:1 it would provide equal etch rates for GaAs and InGaAs with indium alloy composition of 20% or less[9]. The citric acid was prepared by mixing 1 g of anhydrous citric acid crystals with 1 mL of deionized (DI) water. It was necessary to prepare this solution at least one day prior to use, as the citric acid/water reaction is endothermic and wait time is necessary to allow the mixture to return to room temperature. The hydrogen peroxide had a concentration of 30%. This etch is selective, allowing the GaAs/InGaAs etch to proceed to completion without etching of the AlAs layer. This proposed etch was reported to act at a rate of ~200 nm/min, thus yielding an expected total etch time ranging from 40-70 seconds depending on layer thick-nesses of the sample. This range of times also includes additional overetch time to allow for complete removal of material in the areas being etched.

A second etch is required to remove the AlAs layer without damaging the underlying GaAs substrate, or the trilayer GaAs/InGaAs/GaAs structure. In this case, the better method was to use an etchant utilizing an inorganic acid which preferentially attacks the AlAs. Hydrofluoric acid (49% concentration) was chosen as the etchant, as it provided selectivities of greater than 100:1 for high Al content materials.[3] The high concentration was chosen in order to minimize potential damage to the GaAs layers. Due to the extremely small amount of AlAs to be removed, and the high etch rate, the total expected etch time is only on the order of 10-20 seconds. Additionally, the photoresist used is unaffected by either etch. This provides a means to easily preserve the upper structure surface to prevent roughening during the second etch.

## 5.3 Photolithography and Mask Design

Photolithography is a well established means of patterning semiconductor samples. This process uses a photoreactive compound (photoresist) which either becomes soluble or insoluble in a developer solution after being exposed to ultraviolet light. It is broadly classified, based on the solubility following exposure, into positive resist, where the exposed portions are removed by the developer, and negative resist, where the exposed portions become insoluble and remain following development. The areas to be exposed are defined by a mask which is a glass plate with a chrome pattern on one side. The chrome protects certain areas from exposure to the UV light. Consequently, for this experiment, a commonly used positive photoresist, diazonaphthoquinone (DNQ), was used as the photoresist.

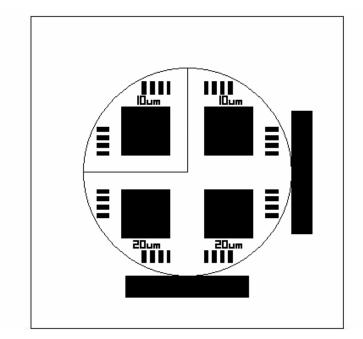

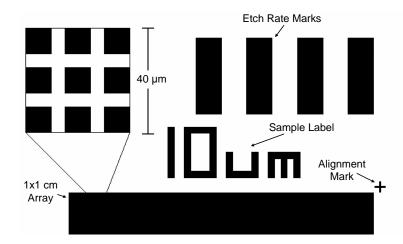

The mask for the photolithography process was designed to meet a number of objectives for this project, as well as to have characteristics which could make it useful for future projects. Specifically, the mask was designed to be usable for both full 2 inch wafers and quarters of 2 inch wafers. Figure 5.3 shows the entire mask pattern. Note that lines marking a circle and a quarter of that circle indicate the size and intended position of full 2 inch wafers and quarter wafers, and are not features on the mask. It was intended that the majority of processing would occur on quarter wafers, which would be affixed to whole wafers using photoresist and aligned with the mask. Additionally, an area of sufficient size to measure with XRD was needed for the patterned area with the maximum surface coverage of the structure of interest. It was determined that an array of either 10  $\mu$ m, shown in Fig. 5.4(inset) or 20  $\mu$ m squares with 5  $\mu$ m spaces between them would provide sufficient spacing between each structure and still provide a high surface area coverage. The features covered 45% and 64% of the array area for the 10  $\mu$ m and 20  $\mu$ m structures respectively. These arrays filled a 10x10 mm<sup>2</sup> area which would lie approximately 5 mm from the cleaved edges of a quarter wafer piece, as shown in Fig. 5.3. This area of unpatterned sample provides the ability to measure both the patterned and unpatterned area using XRD following sample processing. Three additional features, shown in Fig. 5.4, were included on the mask in unused areas. The sample label was included to ease distinction between samples patterned with different array sizes without the need to use a microscope. The etch rate marks were included to provide an area to quantify the etch rates of various etchants being used if necessary. The alignment marks were included to allow for the possibility of

Figure 5.3: Image of full mask pattern, the large bars at the edges of the full wafer marker are used to align the wafer. The large squares are patterned arrays of 10  $\mu$ m and 20  $\mu$ m features.

using this mask later as part of a multimask patterning procedure, where alignment marks would be necessary.

## 5.4 X-Ray Diffraction Technique

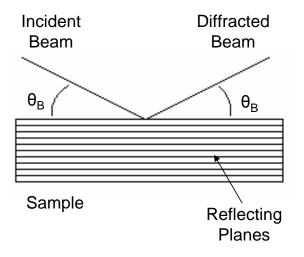

Any radiation striking a material will be both scattered and absorbed. X-ray diffraction makes use of photons that are elastically scattered from the electron clouds of individual atoms of a crystal lattice. Each photon path from the source to the detector is indeterminant and all the possible paths are coherent[11]. These paths are determined by the collimation of the photon beam as it exits the source. The detector will measure the contributions of all possible paths of these photons. The diffraction pattern will be a result of phase difference in different paths. For a single crystal, Bragg's equation describes the angle of the maximum diffracted intensity

$$n\lambda = 2dsin\theta_B \tag{5.1}$$

Figure 5.4: Close up of additional mask features, including sample label, alignment mark and etch rate determination pits.

where *n* is an integer giving the order of diffraction,  $\lambda$  is the wavelength, *d* is the interplanar spacing of the diffracting atomic planes, and, the Bragg angle,  $\theta_B$  is the angle of the incident and diffracted waves relative to the reflecting plane as shown in fig. 5.5. However, Bragg's equation is an idealized case, as the electrons from which the X-rays are scattering populate a cloud around an atom, and the atoms themselves vibrate at non-zero temperatures. The contributions of atomic vibration and electron density can be accounted for by including a scattering factor[11]. Furthermore, Bragg's equation neglects several key aspects of diffraction within the crystal, such as the change in refractive index as the X-rays enter the crystal, and the possibility of photon rediffraction, in which a photon is diffracted multiple times within the crystal. Despite these issues, Bragg's law allows for the extraction of several basic properties of a crystalline layer.

#### 5.4.1 Measured Quantities

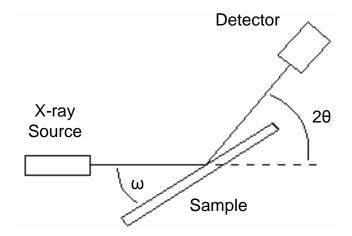

High resolution X-ray diffraction is an important tool for the characterization of epitaxial structures in semiconductors. X-ray scans may be used to determine properties of individual layers, such as mismatch, thickness, and composition. Additionally, X-ray measurements may be used to detect defects within epitaxial layers or samples, including misorientation, mosaic spread, curvature, and strain relaxation. Rocking curve measurements are done with

Figure 5.5: Incident and diffracted Bragg angles for reflection planes parallel to the sample surface.

a wide detector aperture such that the entire reflected beam is detected and involve adjusting the angle of the detector and sample simultaneously such that the reflections from a plane of atoms are measured over a range of incident and detector angles. In this case, the incident beam angle is defined as  $\omega$  and the detector is positioned at 2 $\theta$  as shown in fig. 5.6. In

Figure 5.6: Schematic diagram of X-ray system with relevant angles defined.

this case, both angles are relative to the incident beam. Two types of rocking curve scans are used: symmetric and asymmetric. In the symmetric case, the reflecting lattice planes

are approximately parallel to the sample surface and  $\omega \approx \theta(\frac{2\theta}{2})$ . In the asymmetric case, the reflecting planes are at an angle with the sample surface as shown in Fig. 5.7 where  $\omega = \theta_B - \phi$  for grazing incident ( $\omega = \theta_B + \phi$  for grazing exit) and  $\phi$  is the angle between the lattice planes to be measured and the sample surface.

Figure 5.7: Diagram of an asymmetric grazing incident XRD measurement, planes on the left hand side of the sample are not shown for clarity.

The basic requirement to derive the layer parameters from an X-ray diffraction measurement is a recorded rocking curve. For a sample consisting of a single epitaxial layer on a substrate[4], such a scan will show two peaks, one from the substrate and one from the layer. It should be noted that while this section discusses the derivation of properties of a single layer structure, these techniques would apply to multiple peaks.

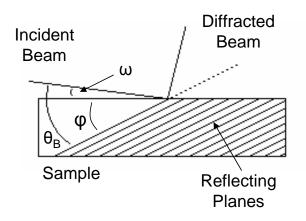

#### Mismatch

For the purpose of demonstration, sample analysis will be carried out on the symmetric (004) reflection scan of a sample consisting of a strained InGaAs layer on a GaAs(001) substrate shown in Fig. 5.8. In this case, the separation between the GaAs and InGaAs peaks,  $\delta\omega$ , is measured to be  $0.388^{\circ} = 0.00677$  rad. A relationship between this peak separation and the atomic layer spacing normal to the substrate can be obtained by taking the derivative of equation 5.1, and is given by

$$\frac{\delta d}{d} = -\delta\theta \cot\theta_B \tag{5.2}$$

Figure 5.8: X-ray diffraction scan to demonstrate measurements of sample 5539.

where  $\delta \omega = \delta \theta$  with respect to the position of the Bragg reflection of the substrate at  $\theta_B$ [4]. In the case where a 004 symmetric reflection is used, then this is the out-of-plane x-ray strain

$$m^* = \frac{\delta d}{d} \tag{5.3}$$

However,  $m^*$  is not the in-plane mismatch, which relates the layer and substrate in-plane lattice parameters and is given by

$$m = \frac{a_l - a_s}{a_s} \tag{5.4}$$

where  $a_l$  is the lattice constant of a the free layer and  $a_s$  is the lattice constant of the substrate. This is related to  $m^*$  by elasticity theory[23] yielding the following relationship

$$m = m^* \frac{1 - \nu}{1 + \nu} \tag{5.5}$$

where v is the Poisson ratio. For the above case for a GaAs substrate, where  $\delta \omega = 0.00677$  rad and  $\theta_B = 0.543$  rad, m was found to be 0.0057. From this mismatch, equations 5.4 and 3.1 can be used to determine the composition of any coherently strained sample. In the example case, these equations yield the result of 7.8% InAs, which closely matches the target composition of 8% InAs.

#### **Strain Relaxation**

In the case where a layer is partially relaxed, the mismatch calculated from the out of plane interatomic spacing will not provide an accurate measure of either composition or strain, unless one is known. In order to determine both quantities, the in-plane lattice constant must be measured in addition to the out of plane lattice constant. By the use of asymmetric (224) scans, two additional peak separations are measured:  $\Delta \omega_i$ , the separation between the layer and substrate peaks for a grazing incident scan (224), and  $\Delta \omega_e$ , the separation between the layer and substrate peaks for a grazing exit (-2-24) scan[4]:

$$\Delta \omega_i = \delta \omega + \delta \phi, \ \Delta \omega_e = \delta \omega - \delta \phi \tag{5.6}$$

where  $\delta \omega$  is the separation of the layer and substrate peaks for a symmetric scan of these lattice planes, and  $\delta \phi$  is the additional separation of the peaks in an asymmetric scan due to tilt from elastic strain. With the assumption that in-plane strain will be equal in the two perpendicular in-plane directions, the equation for the interplanar spacing is

$$\frac{1}{d_{hkl}^2} = \frac{h^2 + k^2}{b_l^2} + \frac{l^2}{c_l^2},$$

(5.7)

where  $b_l$  and  $c_l$  are the in and out of plane lattice constants, respectively and h, k, l are the Miller indices. This can be related to angles using Bragg's law (eq. 5.1) to

$$\frac{4sin^2\omega_l}{\lambda^2} = \frac{h^2 + k^2}{a_l^2} + \frac{l^2}{c_l^2},$$

(5.8)

where  $\omega_l$  is the Bragg peak of the layer. This may be further simplified for a (001) oriented surface by using the formula for interplanar angles in the crystal to

$$sec^{2}\phi_{l} = \frac{c_{l}^{2}}{l^{2}}\left(\frac{h^{2}+k^{2}}{b_{l}^{2}} + \frac{l^{2}}{c_{l}^{2}}\right),$$

(5.9)

where  $\phi_l$  is the angle between the reflecting planes layer and the sample surface. Then using the above relations for  $\Delta \omega_i$  and  $\Delta \omega_e$  provide the atomic spacing both in-plane ( $a_l$ ) and out of plane[4] ( $c_l$ )

$$c_l = \frac{l\lambda}{2sin\omega_l cos\phi_l}, \ b_l = \frac{l\lambda}{2sin\omega_l}\sqrt{\frac{h^2 + k^2}{l^2}}$$

(5.10)

The relaxation is then

$$R = \frac{b_l - a_s}{a_l - a_s} \times 100 \tag{5.11}$$

where  $a_l$  is the lattice parameter of the fully relaxed layer.

#### Thickness

The preferred method for measuring layer thickness is to use the periodic oscillations around the layer peak, labeled thickness fringes in fig. 5.8. In the single layer case, the separation,  $\Delta \omega_p$  is given by[4]

$$\Delta \omega_p = \frac{\lambda \gamma_g}{t \sin 2\theta} \tag{5.12}$$

where  $\lambda$  is the wavelength, *t* is the thickness, and  $\gamma_g$  the cosine of the angle between the diffracted beam and the surface normal. For the case of a symmetric reflection, this simplifies to

$$t = \frac{\lambda}{2\Delta\omega_p \cos\theta} \tag{5.13}$$

It should be noted that these equations do not contain anything about either the material or diffraction conditions besides the Bragg angle and the geometry. This independence is a result of the refractive index for X-rays being very close to unity.

It should be noted that the most reliable way to determine layer thicknesses from a multiple layer structure is by using a simulation. Using X'pert Epitaxy software from Panalytical[10], simulations were performed and then manual adjustments of the parameters, combined with use of the fitting algorithm provided in the software, were utilized to obtain a good fit. The software employs dynamical diffraction physics to obtain the simulated data[4]. Triple-axis measurements were used for the fitting of simulations. These measurements are performed with a detector aperture of 12 arcseconds, which lowers both the signal and background; however, the background is reduced more than the signal resulting in a better signal-to-noise ratio, allowing for a better fit to be obtained than for a similar rocking curve measurement.

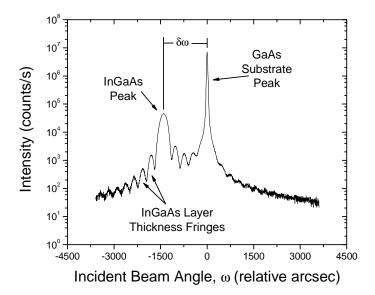

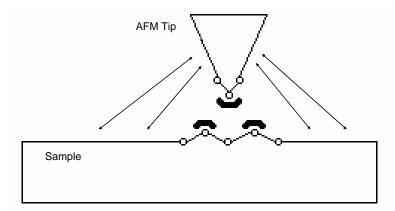

## 5.5 Atomic Force Microscopy

Atomic force microscopy (AFM) is a useful tool for examining the surfaces of materials. In this experiment, an Asylum Research scanning probe microscope was used to measure the surface topography of samples and to detect the presence and density of dislocations by means of the surface steps they produce. The principal behind AFM is that of using a sharp tip to interact with the sample surface and a flexible beam to measure the resultant force with high sensitivity[38]. An AFM tip near a sample will experience both long and short range forces as shown in Fig. 5.9[14]. The short range forces are a result of chemical

Figure 5.9: Diagram of forces experienced by an AFM tip near a surface. Short-range forces are indicated by crescents and long-range forces are indicated by arrows[14]