# InAs/AISb Heterostructure

## **Field-Effect Transistors**

by

Martin W. Dvorak B.Sc. (Eng.), Queen's University, 1995

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF APPLIED SCIENCE

in the School of Engineering Science

© Martin W. Dvorak 1997 Simon Fraser University August, 1997

All rights reserved. This thesis may not be reproduced in whole or in part, by photocopy or other means, without the permission of the author.

# National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 <sup>3</sup> Canada

#### Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file. Votre réference

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence pon exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-24125-4

# Canadä

# **APPROVAL**

NAME:

Martin Dvorak .

DEGREE:

Master of Applied Science (Engineering Science)

TITLE OF THESIS:

InAs/AISb Heterostructure Field Effect Transistors

EXAMINING COMMITTEE:

Chairman: Dr. Shawn Stapleton

Dr. Colombo R. Boløgnesi Senior Supervisor

Dr. Simon P. Watkins Supervisor

Dr. David H. Chow External Examiner Hughes Research Laboratories, Malibu, CA

| DATE APPROVED: | August 7 | 1997 |  |

|----------------|----------|------|--|

|                |          |      |  |

### ABSTRACT

Heterostructure field-effect transistors (HFETs) based on AlSb/InAs/AlSb quantum wells have demonstrated significant high speed performance:  $0.5 \,\mu\text{m}$  gate HFETs with cut-off frequencies  $f_T$  of 93 GHz at drain voltages of 1V have been achieved. The  $\Gamma$ -L intervalley separation of ~0.9eV in InAs, large InAs/AlSb interface conduction band discontinuity of ~1.35 eV, and high room temperature mobilities of 20,000-30,000 cm<sup>2</sup>/V·s make this material system very attractive for low-power, high speed transistor applications.

Because of the relatively narrow band gap of InAs (~0.36eV), these HFETs are subject to several impact ionization related non-idealities, some of which may involve trapping of holes generated by impact ionization. The DC drain characteristics feature an abruptly increased output conductance with increasing drain bias (kink effect). In the present dissertation, two methods aiming to reduce impact ionization effects were studied. The first approach was the fabrication of dual gate HFETs which have demonstrated significant improvements over single gate HFETs under DC operating conditions. Secondly, quantum confinement was used to increase the quantization energies and the effective forbid-den energy gap within the InAs quantum well in an effort to increase the impact ionization threshold. Temperature and frequency dependent sidegating measurements were also used to provide the first evidence for the effect of hole traps in InAs/AISb HFET buffer layers.

Microwave measurements show a strong dependence on the quantum well width: the higher mobility in wider wells result in superior frequency performance that is likely due to an enhanced peak electron velocity in the channel. At microwave frequencies, conventional microwave FET models prove to be inappropriate because they do not account for impact ionization effects which become progressively severe in wider wells. In the course of this work, we have fabricated  $0.55 \,\mu m$  gate InAs/AlSb HFETs with a unity current gain

cut-off frequency  $f_T = 67$  GHz: these are some of the fastest FETs ever fabricated for that gatelength.

, 1

.

### ACKNOWLEDGEMENTS

First and foremost I wish to thank Colombo for his endless, patient guidance that made this work possible. I also thank Dave Chow for growing the device layers used, and for temporarily leaving the sunny beaches of Malibu for rainy Vancouver just to be my external examiner. Thanks are due to Simon for being a good sport in being a co-supervisor and for supplying wafers vitally needed for etch studies. Shawn I thank for use of his microwave characterization equipment (and for chairing the examining committee), and Prof. Deen for the use of his facilities. Noureddine I thank for his expert advice, and in advance for my next thesis! I thank Plamen for his expert wirebonding of un-wirebondable devices and help with device characterization. Many thanks to Brigitte for doing everything she does best, always managing even when I hand her my application forms after the last minute! I thank many others in Engineering, Physics and down at MPR for various little favors that added up to make my job easier, and I thank the staff of SFU library that have allowed huge volumes of borrowed material and interlibrary loan requests. But I most especially thank Sunjae, whose infinite love and support made it all worthwhile. I'll need you for the Ph.D., too!

# TABLE OF CONTENTS

| Approval          |                                                              | ii  |

|-------------------|--------------------------------------------------------------|-----|

| Abstract          |                                                              | iii |

| Acknowledgemen    | ts                                                           | v   |

| Table of contents | · · · · · · · · · · · · · · · · · · ·                        | vi  |

| List of tables    |                                                              | ix  |

| List of figures   |                                                              | X   |

| CHAPTER 1         |                                                              |     |

| Introducti        | D <b>n</b>                                                   | 1   |

| 1.1               | Compound semiconductor MESFETs & HFETs                       | 1   |

| 1.2               | InAs/AlSb HFETs                                              |     |

|                   | 1.2.1 Difficulties with InAs/AISb HFETs                      |     |

|                   | 1.2.2 Other work on InAs/AlSb HFETs 1                        |     |

| 1.3               | Scope of dissertation 1                                      | .7  |

| CHAPTER 2         |                                                              |     |

| Device Fal        | prication                                                    | 9   |

| 2.1               | HFET epitaxial layer structure                               |     |

| 2.1               | Prototypical HFET processing sequence                        | 22  |

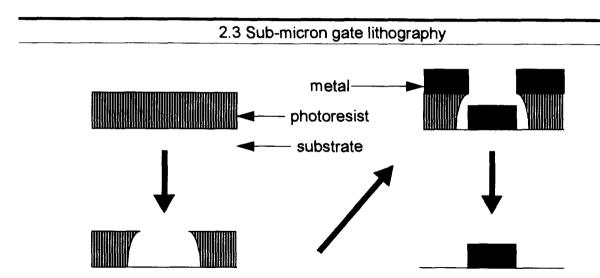

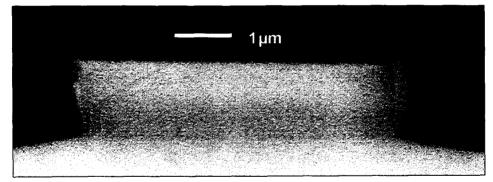

| 2.3               | Sub-micron gate lithography                                  |     |

|                   | 2.3.1 Overhanging photoresist profile obtained using toluene |     |

|                   | soak                                                         |     |

| 2.4               | Ohmic contacts                                               |     |

|                   | <b>2.4.1</b> Introduction                                    | 1   |

| 2.4.2 | Experimental                 | 33 |

|-------|------------------------------|----|

| 2.4.3 | Other recently reported work | 35 |

.

## **CHAPTER 3**

| Impact Ion | ization                                       | . 37 |

|------------|-----------------------------------------------|------|

| 3.1        | The kink effect in InAs/AISb HFETs            | . 38 |

| 3.2        | Attempts to reduce the kink effect            | . 42 |

|            | 3.2.1 Dual-gate HFETs                         | . 42 |

|            | 3.2.2 AlSb/InAs/AlSb quantum well engineering |      |

|            | 3.2.3 Back-gate HFETs                         | . 55 |

## **CHAPTER 4**

| Evidence of | Traps in InAs/AISb HFETs: Sidegating Measurements |    |

|-------------|---------------------------------------------------|----|

| 4.1         | Previous evidence of traps in InAs/AlSb system    | 58 |

| 4.2         | Sidegating measurements of InAs/AISb HFETs        | 59 |

|             | 4.2.1 Test structure fabrication                  | 59 |

|             | 4.2.2 Room temperature measurements.              | 59 |

|             | 4.2.3 Variable sweep frequency measurements       | 61 |

|             | 4.2.4 Temperature dependence of SINDR             | 64 |

|             | 4.2.5 Measurements with illumination              | 67 |

| 4.3         | Analysis and discussion                           | 69 |

| 4.4         | Conclusion                                        | 73 |

## CHAPTER 5

| Microwave l | Performance of InAs/AISb HFETs                               | 75 |

|-------------|--------------------------------------------------------------|----|

| 5.1         | Microwave performance and InAs quantum well width            | 76 |

|             | 5.1.1 Introduction                                           | 76 |

|             | 5.1.2 Microwave measurements                                 | 77 |

|             | 5.1.3 Results                                                |    |

|             | 5.1.4 Analysis                                               |    |

| 5.2         | S-parameter frequency evolution with high rate of impact     |    |

|             | ionization                                                   | 84 |

|             | 5.2.1 Introduction                                           | 84 |

|             | 5.2.2 Drain bias dependence of reflection S-parameters for 5 | 0Å |

|             | quantum well devices                                         |    |

|             | 5.2.3 S-parameters for 100Å quantum well device              |    |

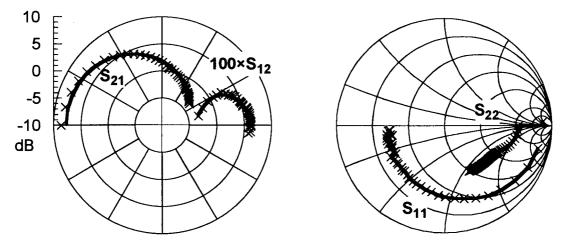

|           |         | <ul> <li>5.2.4 Dispersion of extracted small-signal equivalent circuit parameters.</li> <li>5.2.5 Analysis and modelling</li></ul>                                                                                                                                                                                                     | )5                   |

|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|           | 5.3     | Current gain roll-off with frequency for InAs/AlSb HFETs9                                                                                                                                                                                                                                                                              | ŏ                    |

| CHAPTER 6 |         |                                                                                                                                                                                                                                                                                                                                        |                      |

| Summ      | ary and | d Conclusions                                                                                                                                                                                                                                                                                                                          | 13                   |

|           |         | Summary of research findings       10         6.1.1       Control of the kink effect: dual gate HFETs and quantum well engineering       10         6.1.2       Hole traps       10         6.1.3       Microwave performance dependence on mobility       10         6.1.4       Impact ionization and microwave performance       10 | )4<br>)5<br>)5<br>)6 |

|           | 6.2     | Future directions106.2.1Compliant substrates6.2.2Other buffer layer schemes6.2.3Device characterization and modeling10                                                                                                                                                                                                                 | )7<br>)9             |

## **APPENDIX** A

| Α | Process run sheet for alloyed Ohmic contact HFET 111     |

|---|----------------------------------------------------------|

| В | Process run sheet for non-alloyed Ohmic contact HFET 113 |

| С | Note on edge bead removal 114                            |

| C |                                                          |

# LIST OF TABLES

| Table 1-1 : Material properties of selected semiconductors at 300K                    |

|---------------------------------------------------------------------------------------|

| Table 5-1 : Calculated parameters for 50Å and 100Å quantum well HFETs for gatelengths |

| of $0.7 \mu m$ and $0.6 \mu m$ . Measured parameters at $V_{DS} = 1.0 V.$             |

# LIST OF FIGURES

| Figure | 1-1 : Schematic cross-section of a conventional MESFET                                                                                                                                                                                                                                                                                                                                               |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 1-2 : Representative I-V characteristics of a GaAs MESFET fabricated in the CSDL                                                                                                                                                                                                                                                                                                                     |

| Figure | 1-3 : Simplified small-signal equivalent circuit of MESFET or HFET7                                                                                                                                                                                                                                                                                                                                  |

| Figure | 1-4 : Energy gap vs. lattice constant for III-V compound semiconductors of most interest. The 6.1 Å family is blackened                                                                                                                                                                                                                                                                              |

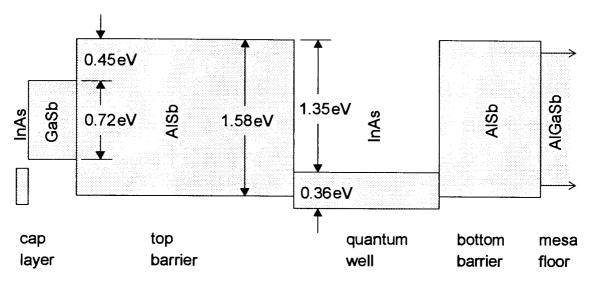

| Figure | 1-5 : Basic band structure of HFET active layers used in this study                                                                                                                                                                                                                                                                                                                                  |

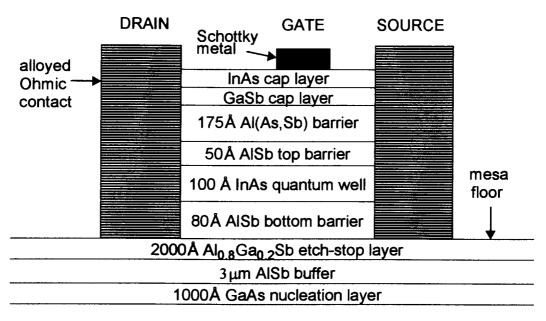

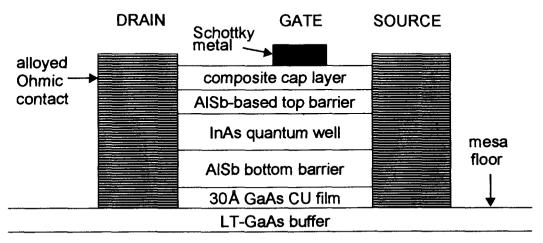

| Figure | 2-1 : Cross-section of prototypical InAs/AlSb HFET with alloyed Ohmic contacts (not to scale)                                                                                                                                                                                                                                                                                                        |

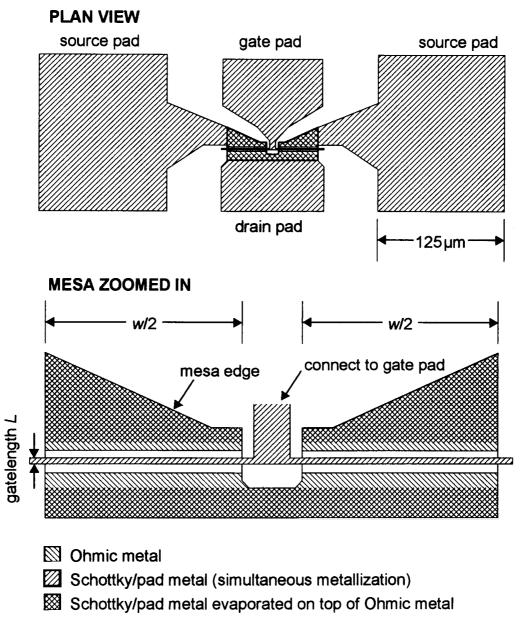

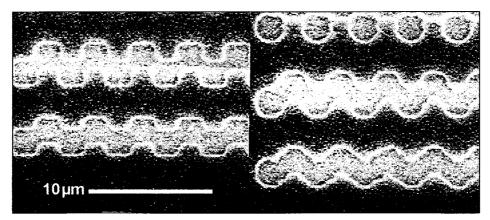

| Figure | 2-2 : Layout of InAs/AlSb HFET configured for microwave probing. The process<br>only requires 3 photolithographic steps to produce microwave testable devices. The<br>gatelength (here, the narrow gate finger dimension as shown in the zoomed image)<br>is in the range of $L \sim 0.5$ -3.0 µm and the transistor width (gate width) is w/2 + w/<br>$2 = 80 \mu$ m. Pads are on AlGaSb mesa floor |

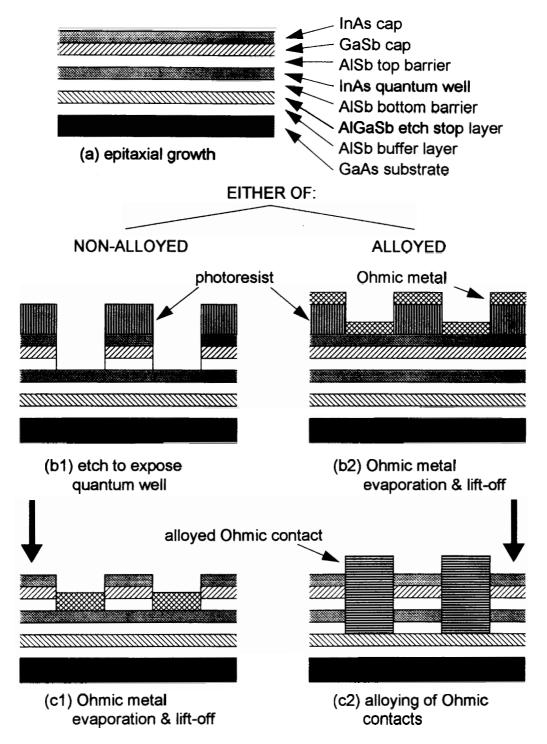

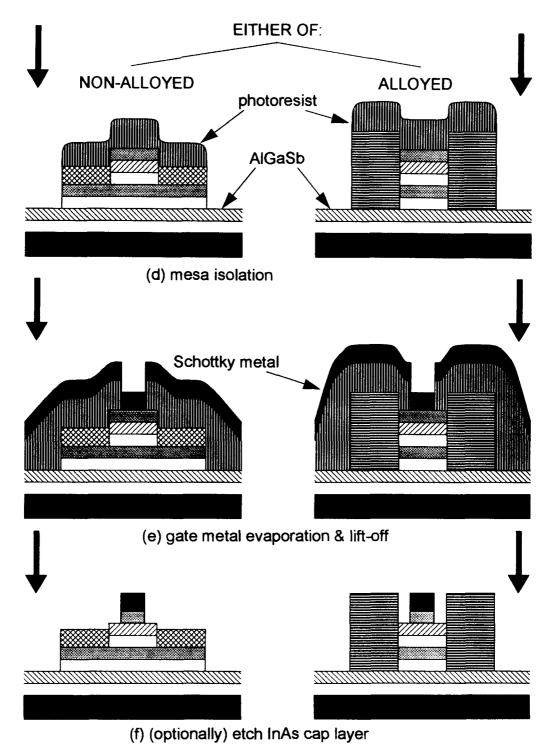

| Figure | 2-3 : Process run for HFETs (not to scale)                                                                                                                                                                                                                                                                                                                                                           |

| Figure | 2-4 : Process run for HFETs (continued; not to scale)                                                                                                                                                                                                                                                                                                                                                |

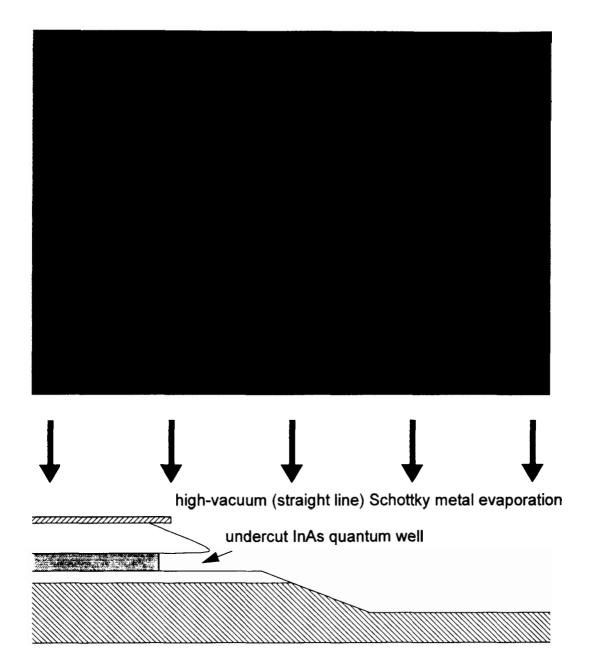

| Figure | 2-5 : Side-on cross-section view of HFET gate evaporation showing how an undercut is required to avoid gate & pad metal to quantum well short-circuiting (approximately to scale). Because metal evaporated under high vacuum will travel in straight lines, an air gap will prevent metal-InAs contact. 27                                                                                          |

| Figure | 2-6 : Steps in the lift-off metallization process                                                                                                                                                                                                                                                                                                                                                    |

| Figure | 2-7 : Comparison of step coverage of undercut and non-undercut photoresist resulting from high-vacuum evaporation and sputtering                                                                                                                                                                                                                                                                     |

| Figure | 2-8 : Photoresist edge profiles following lift-off process                                                                                                                                                                                                                                                                                                                                           |

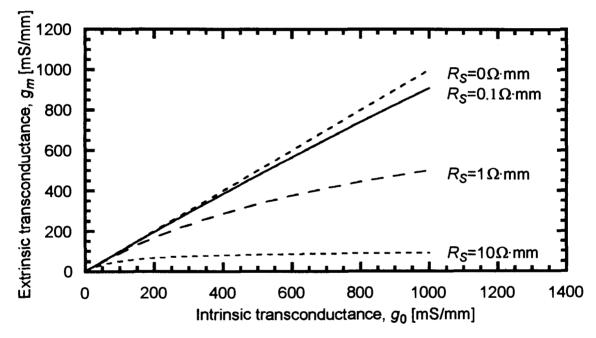

| Figure | 2-9 : Extrinsic transconductances $g_m$ as a function of source resistance RS and intrinsic transconductance $g_0$ (quantities normalized to unit transistor width) 32                                                                                                                                                                                                                               |

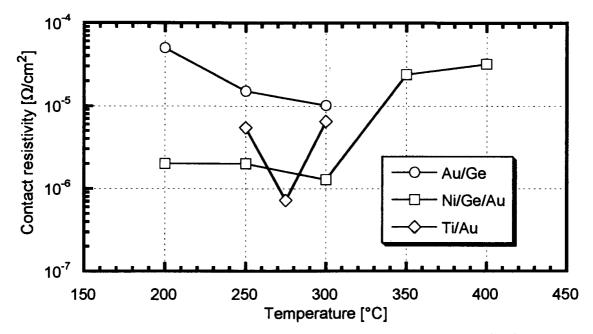

| Figure | 2-10 : Ohmic contact resistances for various annealing temperatures for three different metallizations                                                                                                                                                                                                                                                                                               |

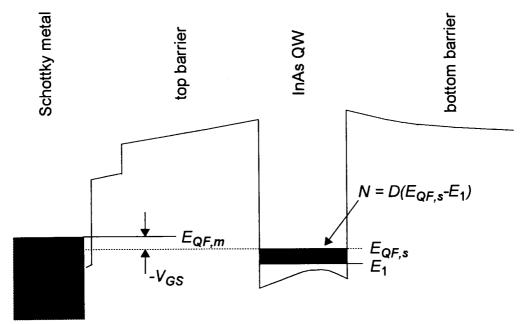

| Figure | 3-1 : Schematic of conduction band edge of biased InAs/AlSb HFET. N is the electron charge in the quantum well, D is the density of states in the quantum well, $E_{QF,s}$ is the quasi-Fermi level in the semiconductor, $E_{QF,m}$ is the quasi-Fermi level in the Schottky metal, $E_1$ is the ground state energy in the quantum well, and $-V_{GS}$ is a negative gate bias.                    |

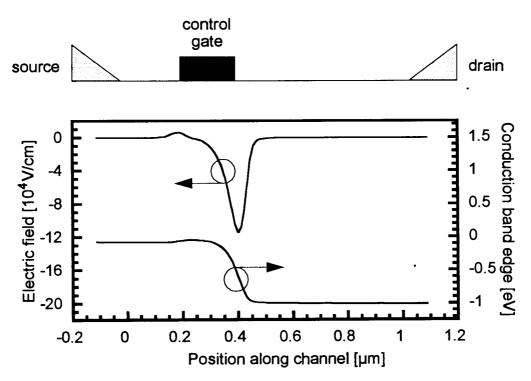

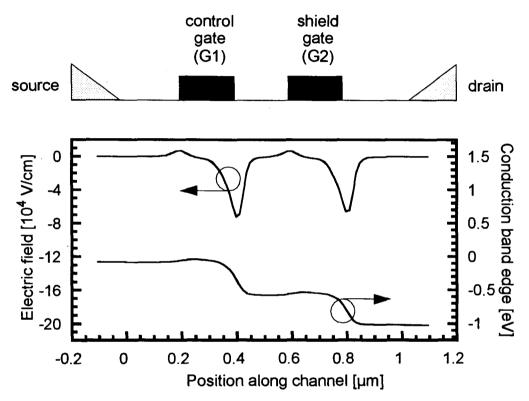

| Figure | 3-2 : Simulated conduction band energy and electric field along the channel of a standard HFET (drain bias $V_{DS} = 1 V$ , gate bias $V_{GS} = -0.6 V$ )                                                                                                                                                                                                                                                                                                                                              |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

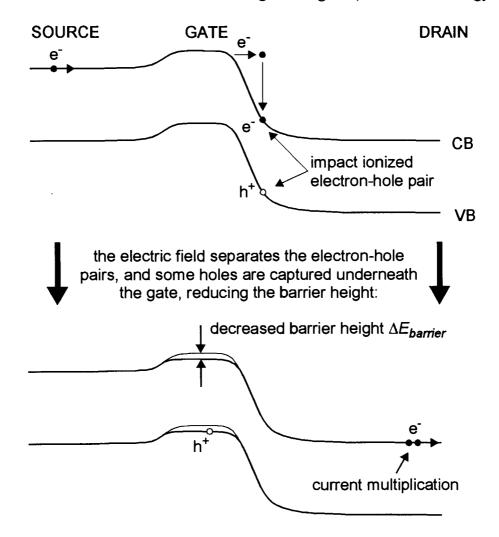

| Figure | 3-3 : Impact ionization in the high-field region of channel and increase in effective<br>barrier height under the gate. Some of the impact ionization holes appear as gate<br>leakage current due to the lack of confinement in the channel (not shown). Vertical<br>scale exaggerated for clarity of presentation                                                                                                                                                                                     |

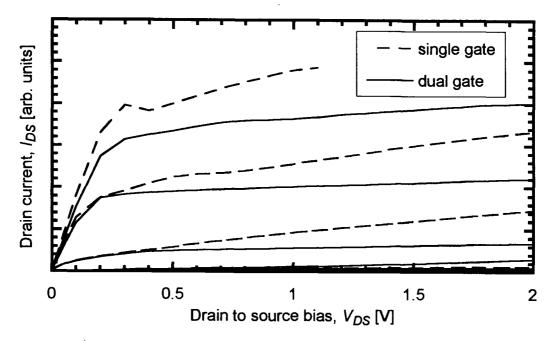

| Figure | 3-4 : Simulated drain I-V characteristics for single- and dual-gate 0.2μm prototypical AlGaAs/InGaAs/AlGaAs HFETs                                                                                                                                                                                                                                                                                                                                                                                      |

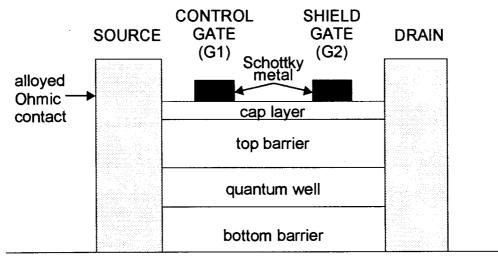

| Figure | 3-5 : Simplified cross-section of typical dual-gate InAs/AlSb HFET with alloyed<br>Ohmic contacts (not to scale)                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure | 3-6 : Simulated conduction band energy and electric field along the channel of a dual-gate HFET ( $V_{DS} = 1 V$ , $V_{GS} = -0.6 V$ , $V_{shield} = 0 V$ )                                                                                                                                                                                                                                                                                                                                            |

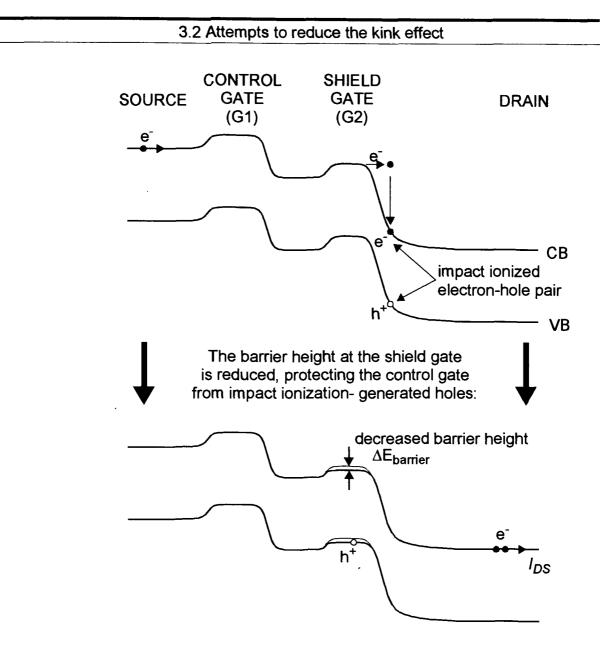

| Figure | 3-7 : Collection of impact ionization generated holes underneath the shield gate and away from the control gate                                                                                                                                                                                                                                                                                                                                                                                        |

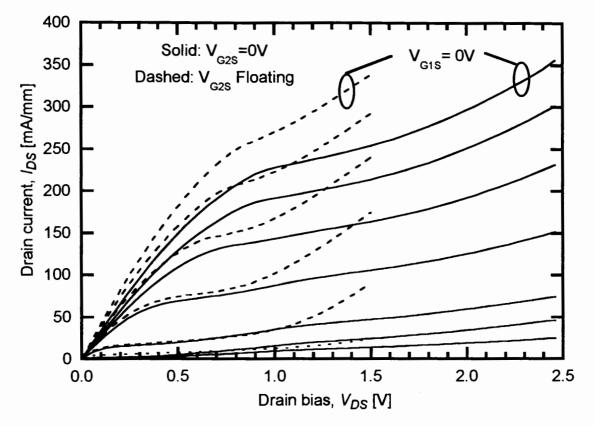

| Figure | $3-8: Measured \ drain \ I-V \ characteristics \ for \ otherwise \ identical \ single- \ and \ dual-gate 1.0 \ \mum \ InAs/AlSb \ HFETs. \ Gate \ voltages \ V_G \ stepped \ from \ 0 \ to \ -1.2 \ V. \ \dots \ .48$                                                                                                                                                                                                                                                                                  |

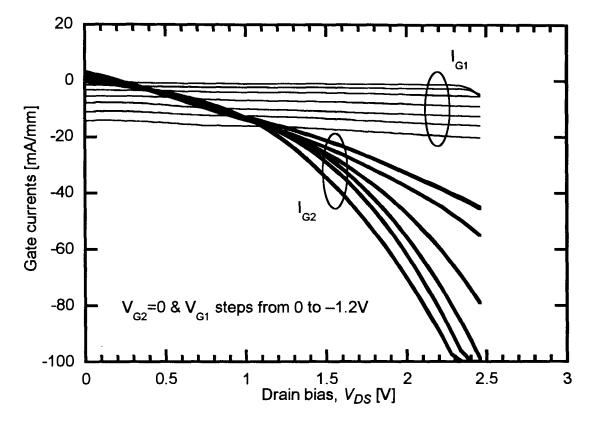

| Figure | 3-9 : Measured control gate (thin lines) and shield gate (thick lines) currents for dual-gate 1.0 µm InAs/AlSb HFET                                                                                                                                                                                                                                                                                                                                                                                    |

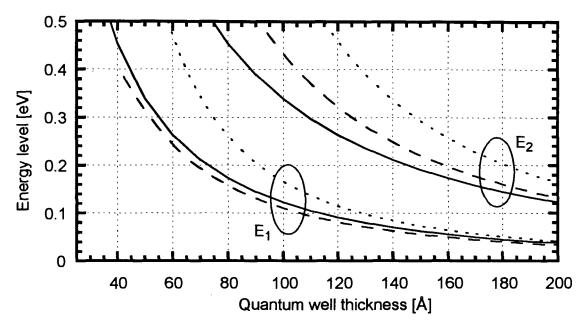

| Figure | 3-10 : First two energy levels of InAs/AlSb quantum well: infinite quantum well including non-parabolicity of bands [73], solid lines; 1.3 eV quantum well neglecting non-parabolicity, dashed lines; infinite quantum well neglecting non-parabolicity, dotted lines                                                                                                                                                                                                                                  |

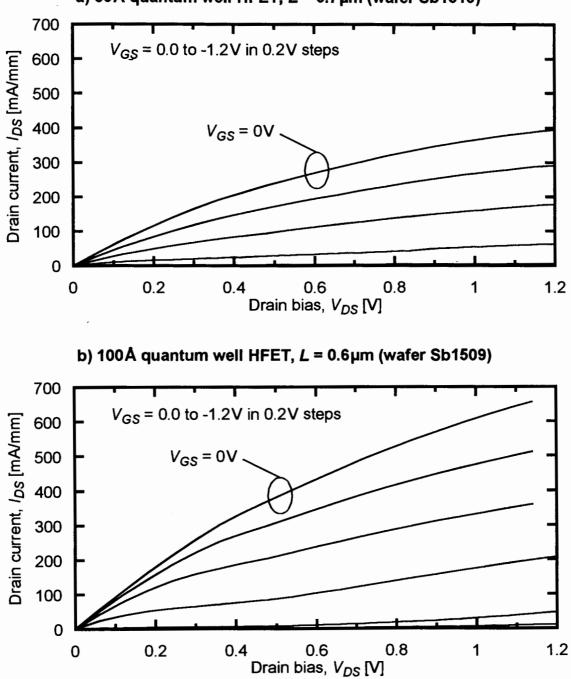

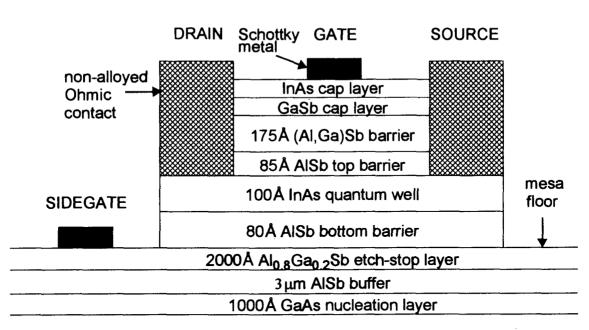

| Figure | 3-11 : Drain characteristics of (a) 50Å and (b) 100Å quantum well HFETs that are otherwise nominally identical                                                                                                                                                                                                                                                                                                                                                                                         |

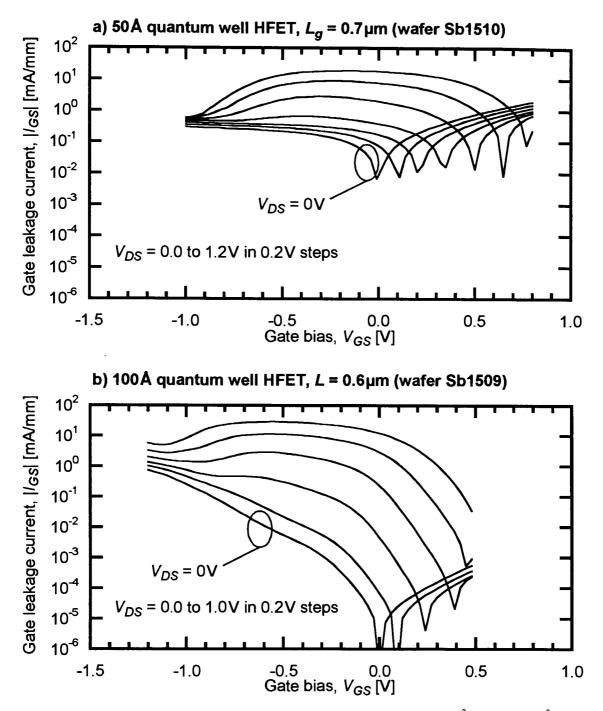

| Figure | 3-12 : Bell-shaped gate leakage current characteristics of (a) 50 Å and (b) 100 Å quantum well HFETs that are otherwise nominally identical. Hole leakage is reduced beyond pinch-off (when little current is flowing) and when gate is positively biased. Diode leakage increases with gate-channel bias. The 50 Å device suffers from anomalously high diode leakage that may relate to mesa sidewall leakage. The bell shape arises from impact ionization generated holes drained through the gate |

| Figure | 4-1 : Cross-section of sidegating InAs/AlSb HFET test structure with non-alloyed<br>Ohmic contacts (not to scale)                                                                                                                                                                                                                                                                                                                                                                                      |

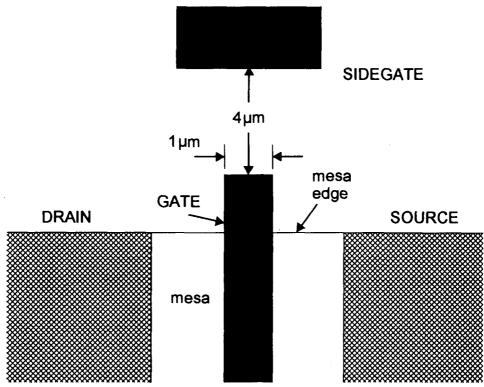

| Figure | 4-2 : Top view of sidegating InAs/AlSb HFET test structure (approx. to scale) 61                                                                                                                                                                                                                                                                                                                                                                                                                       |

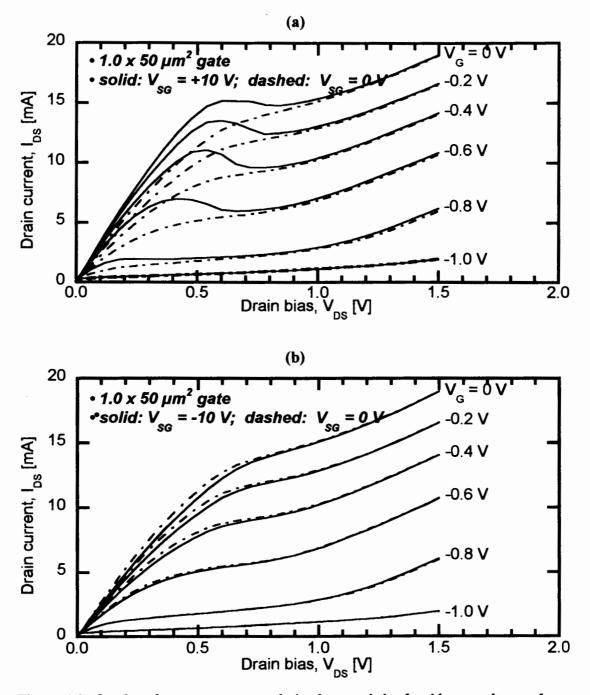

| Figure | 4-3 : Overlay of room temperature drain characteristics for sidegate voltages of $V_{SG} = 0V$ (dashed lines), and simultaneously (a) $V_{SG} = +10V$ or (b) $V_{SG} = -10V$ (solid lines). At large positive sidegate voltages SINDR appears for low $V_{DS}$ . The                                                                                                                                                                                                                                   |

| characteristics show no sidegating effect at high drain biases. Large negative sidegate voltages have almost no effect on the drain I-V characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

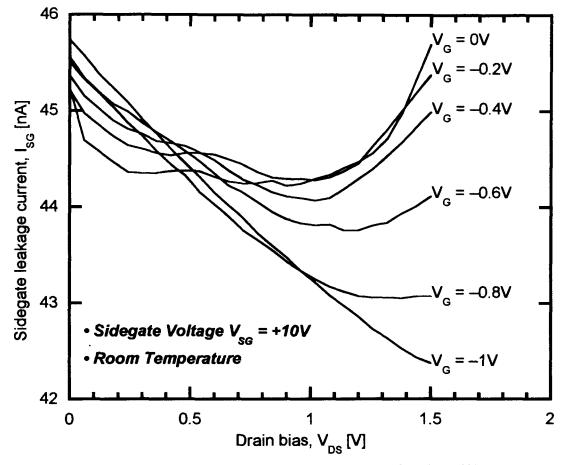

| Figure 4-4 : Room temperature sidegate leakage current as a function of bias conditions for<br>a sidegate electrode located 4µm away from the InAs/AISb HFET mesa edge for<br>sidegate voltage V <sub>SG</sub> = +10V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                |

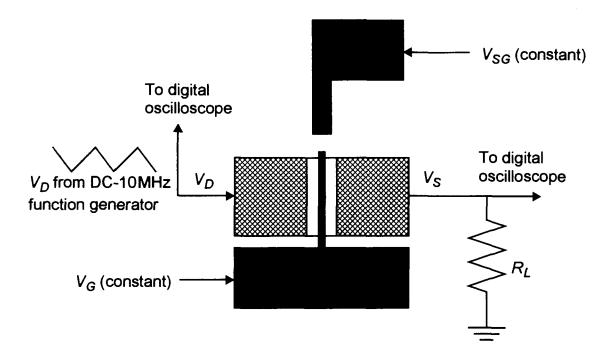

| Figure 4-5 : Diagram of variable-frequency sidegating measurement circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 54                                                             |

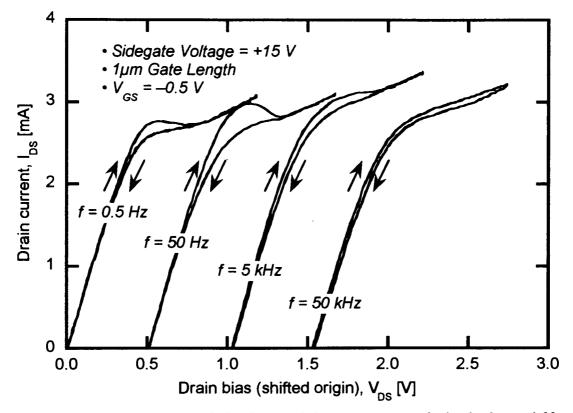

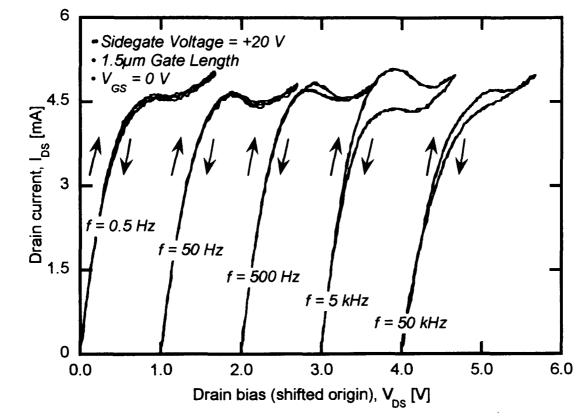

| Figure 4-6 : Room temperature drain characteristic measurements obtained using variable<br>sweep frequency circuit with a sidegate potential $V_{SG} = +15$ V, and a gate bias of<br>$V_G = -0.5$ V. The NDR regions and the associated hysteresis disappear at higher<br>frequencies. This behavior suggests that a slow deep level is associated with<br>SINDR.                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |

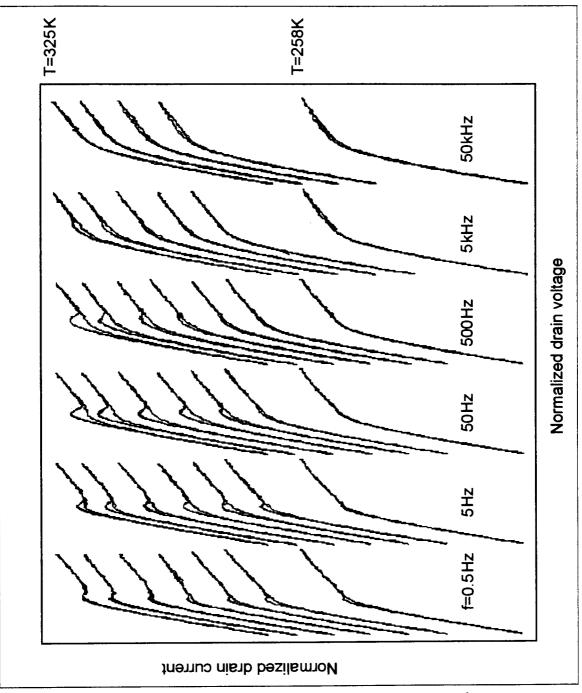

| Figure 4-7 : Temperature and frequency dependence of SINDR measured at temperature<br>of 358, 278, 288, 298, 308, 318, and 325K, at sweep frequencies of 0.5, 5, 50, 500<br>5000 and 50,000 Hz. The voltage and current axes are normalized for clarity, and<br>offset to show temperature-frequency dependence. No SINDR is observed below<br>260 K.                                                                                                                                                                                                                                                                                                                                                                                                 | 0,                                                             |

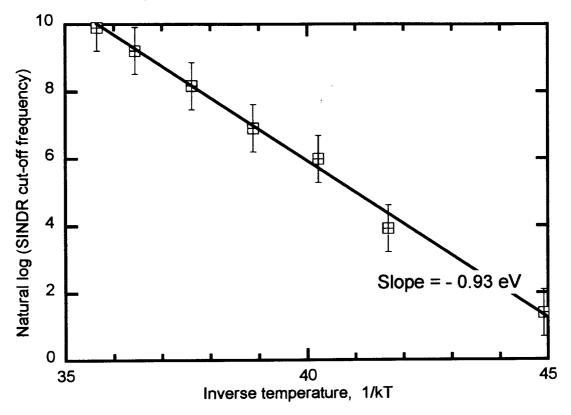

| Figure 4-8 : Plot of the natural logarithm of the SINDR cut-off frequency as a function of inverse temperature. SINDR displays an activation energy of 0.93±0.05 eV 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                |

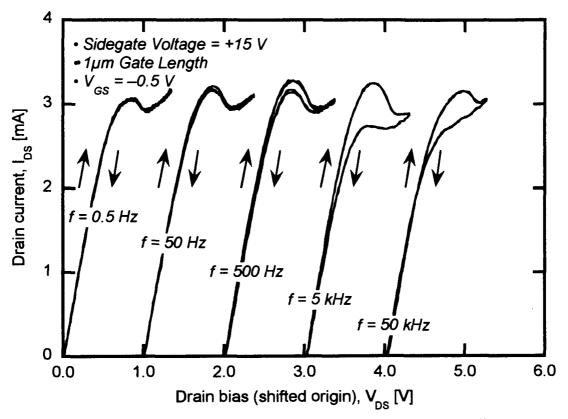

| Figure 4-9 : Room temperature drain I-V measurements obtained with low illumination through the microscope lens. Measurements were obtained with variable sweep frequency measurement circuit, using a sidegate potential $V_{SG} = +15$ V, and a gat bias of $V_G = -0.5$ V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | te<br>58                                                       |

| Figure 4-10 : Room temperature drain I-V measurements obtained with maximum illumination through the microscope lens. Measurements were obtained with variable sweep frequency measurement circuit, using a sidegate potential $V_{SG} = +20V$ , and a gate bias of $V_G = 0V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59                                                             |

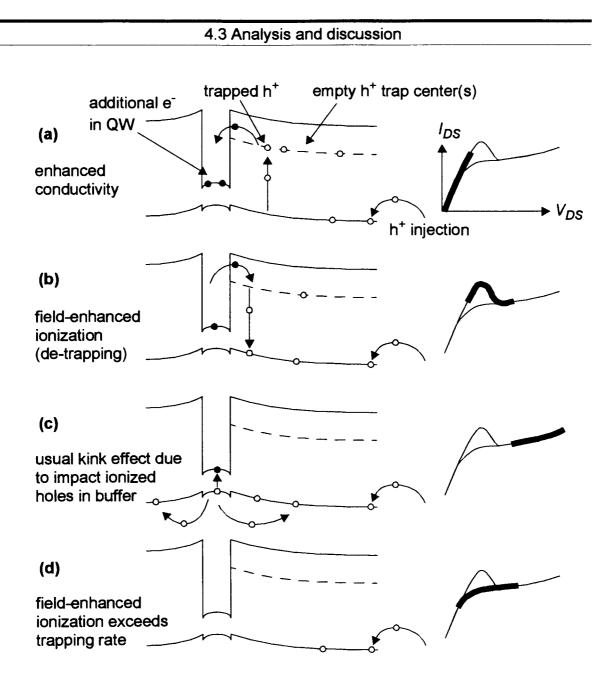

| Figure 4-11 : Proposed mechanism for sidegating-induced negative differential resistance<br>(SINDR) in InAs/AISb HFETs: a) at low drain biases, hole traps are occupied by<br>holes injected from the positively biased buffer, and so add electron charge $\Delta f_T N$<br>to QW; b) as the drain bias $V_{DS}$ is increased, a net emission of holes takes place; c<br>at high drain biases, no holes remain trapped and a regular kink regime is entered<br>d) as the bias is lowered, no holes are trapped until below the SINDR hump. SRH<br>statistics link the presence of trapped holes with an increased electron density, as<br>long as the characteristic frequencies of the trapping process is high compared wit<br>the sweep frequency | , (T);<br>(T);<br>(T);<br>(T);<br>(T);<br>(T);<br>(T);<br>(T); |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                |

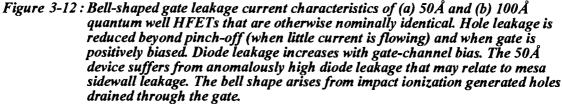

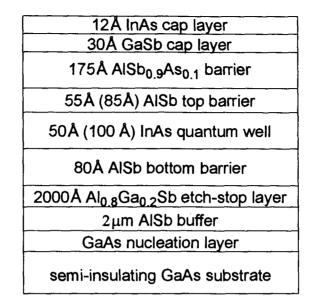

| Figure 5-1 : Layer structure of 50Å and 100Å InAs quantum well HFETs used in this study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                |

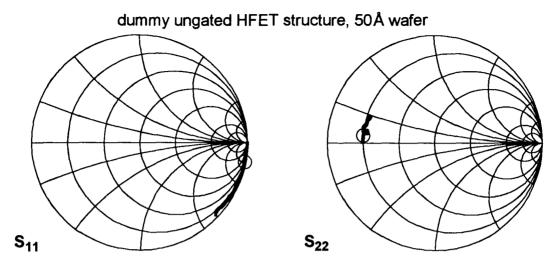

| Figure 5-2 : S <sub>11</sub> and S <sub>22</sub> of dummy ungated HFET structure from 0-40 GHz (smoothed data). S <sub>11</sub> is capacitive (C <sub>pad</sub> = 28 fF) and S <sub>22</sub> is inductive. Marker indicates 10 GHz                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

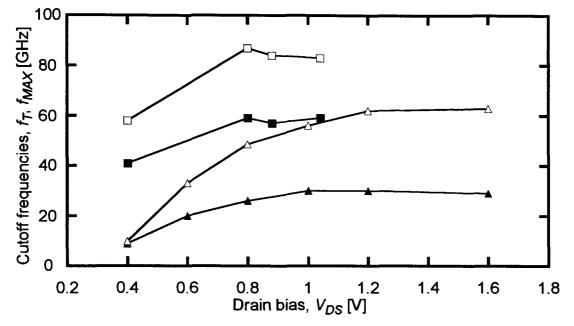

| Figure 5-3 : Unity current gain and MAG intrinsic cutoff frequencies $f_T$ (filled markers) and $f_{MAX}$ (hollow markers) as a function of $V_{DS}$ . Square markers: 100Å InAs quantum well, 0.6 $\mu$ m gatelength; triangular markers: 50Å InAs quantum well, 0.7 $\mu$ m gatelength. We see that the values for $f_T$ are much higher for the 100Å devices but the ratios $f_T/f_{MAX}$ are much greater for the 50Å devices                                                                                                                                       |

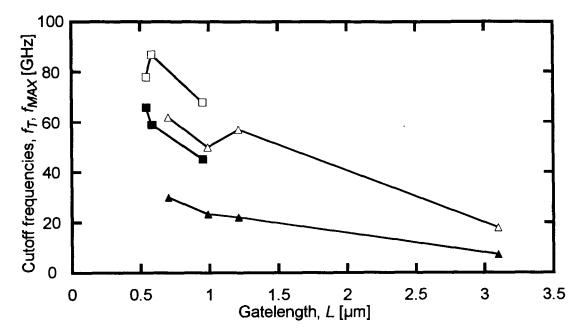

| <ul> <li>Figure 5-4 : Maximum f<sub>T</sub> (filled markers) and f<sub>MAX</sub> (hollow markers) as a function of gatelength for optimized V<sub>DS</sub> and V<sub>GS</sub>. Square markers: 100Å InAs quantum well, 0.6 μm gatelength; triangular markers: 50Å InAs quantum well, 0.7 μm gatelength</li></ul>                                                                                                                                                                                                                                                        |

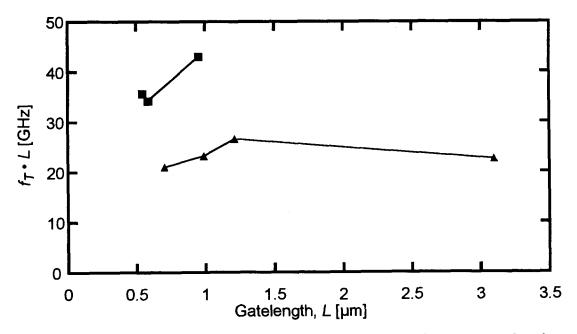

| Figure 5-5 : Unity current gain cutoff frequency × gatelength product f <sub>T</sub> •L as a function of gatelength. Solid square markers: 100Å InAs quantum well; solid triangular markers: 50Å InAs quantum well                                                                                                                                                                                                                                                                                                                                                      |

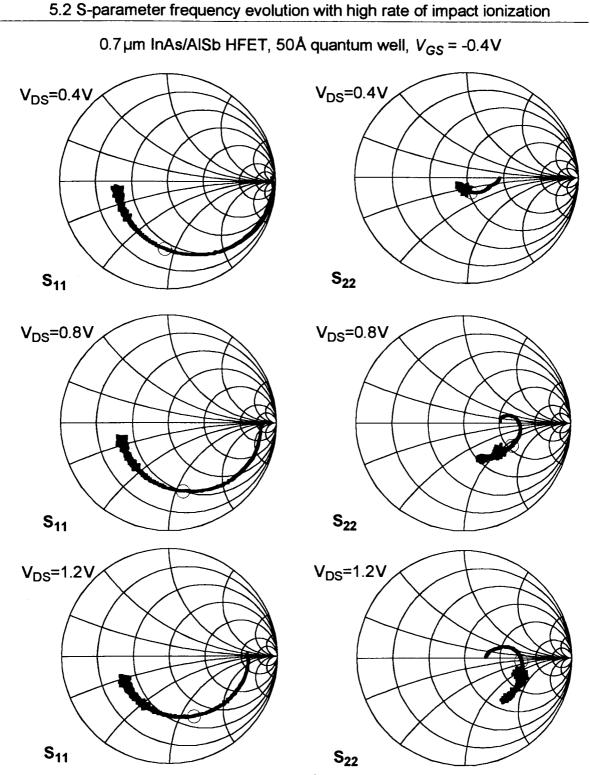

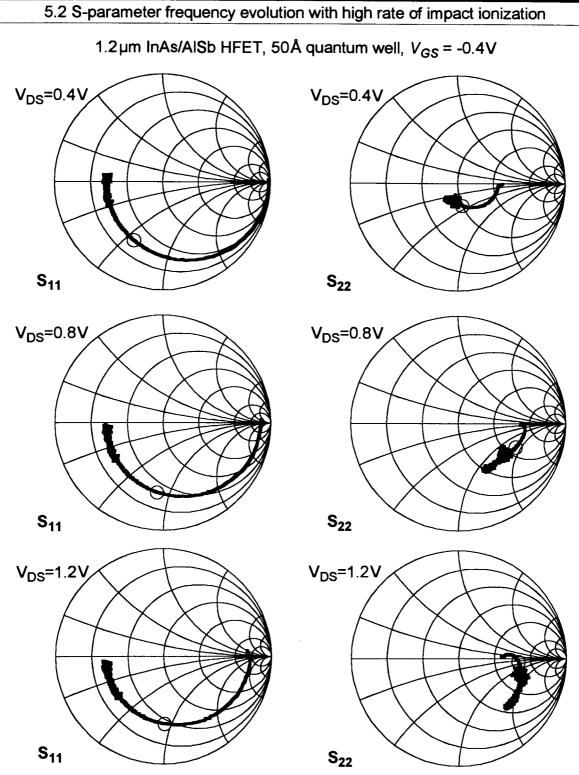

| Figure 5-6 : $S_{11}$ and $S_{22}$ of 0.7 $\mu$ m HFET (50 Å quantum well) at drain biases $V_{DS} = 0.4 V$ , 0.8 V, 1.2 V and gate bias of $V_{GS} = -0.4 V$ . Circular marker indicates 10 GHz 85                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 5-7 : $S_{11}$ and $S_{22}$ of 1.2 µm HFET (50Å quantum well) at drain biases $V_{DS} = 0.4 V$ , 0.8 V, 1.2 V, and gate bias of $V_{GS} = -0.4 V$ . Circular marker indicates 10GHz 86                                                                                                                                                                                                                                                                                                                                                                           |

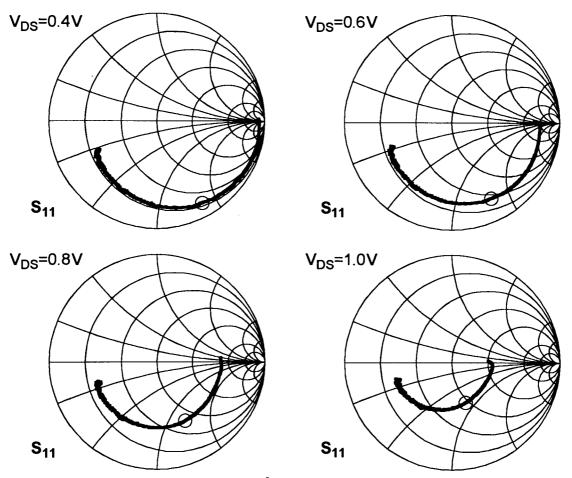

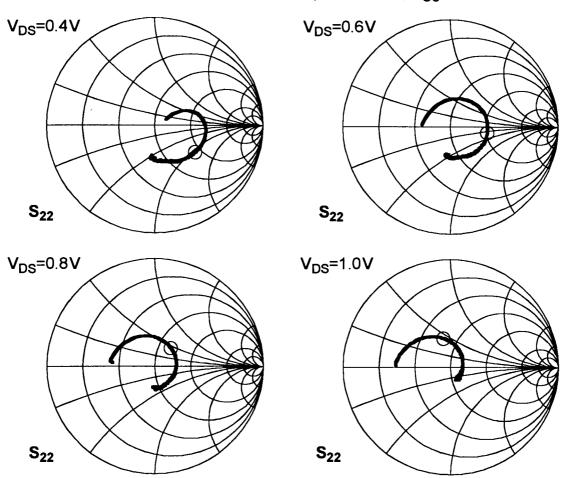

| Figure 5-8 : $S_{11}$ of 0.55 µm HFET (100Å quantum well) at drain biases $V_{DS} = 0.4 V, 0.6 V, 0.8 V, 1.0 V$ , and gate bias of $V_{GS} = -1.0 V$ . Circular marker indicates 10GHz. 87                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 5-9 : $S_{22}$ of 0.55 µm HFET at drain biases of $V_{DS} = 0.4V$ , 0.6V, 0.8V, 1.0V, and gate bias of $V_{GS} = -1.0V$ . Circular marker indicates 10GHz                                                                                                                                                                                                                                                                                                                                                                                                        |

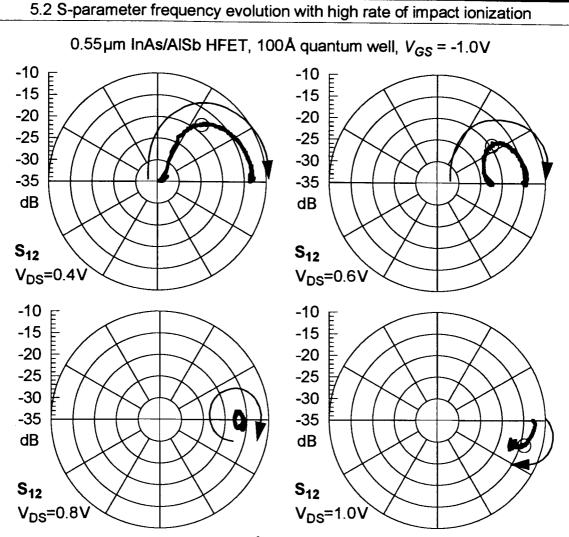

| Figure 5-10 : $S_{12}$ of 0.55 µm HFET (100 Å quantum well) at drain biases $V_{DS} = 0.4 V$ ,<br>0.6 V, 0.8 V, 1.0 V, and gate bias of $V_{GS} = -1.0 V$ . Circular marker indicates 10 GHz.<br>Arrow indicates direction of increasing frequency from 0 to 40 GHz                                                                                                                                                                                                                                                                                                     |

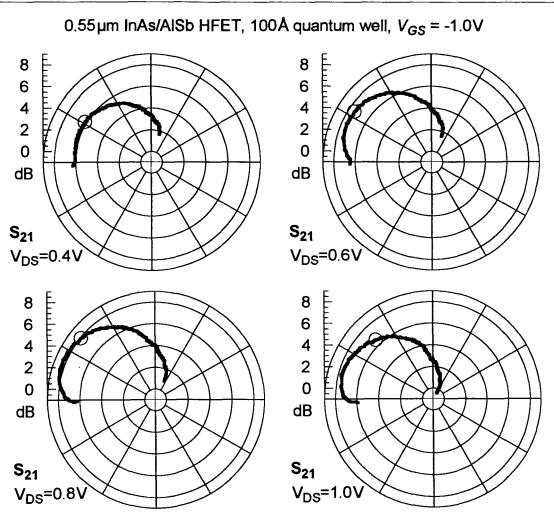

| Figure 5-11 : $S_{21}$ of 0.55 µm HFET (100 Å quantum well) at drain biases $V_{DS} = 0.4 V$ ,<br>0.6 V, 0.8 V, 1.0 V, and gate bias of $V_{GS} = -1.0 V$ . Circular marker indicates<br>10 GHz                                                                                                                                                                                                                                                                                                                                                                         |

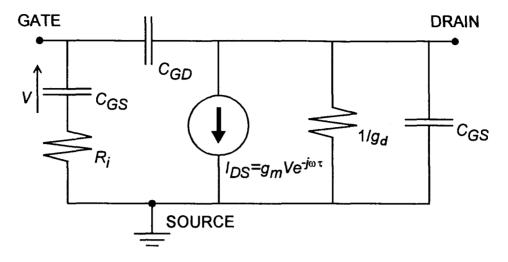

| Figure 5-12 : Conventional simplified small-signal intrinsic equivalent circuit for<br>MESFET/HFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

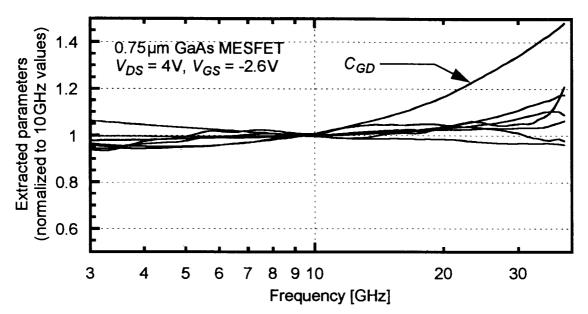

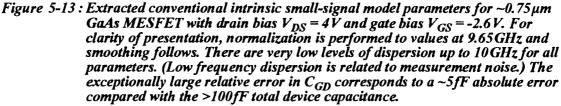

| Figure 5-13 : Extracted conventional intrinsic small-signal model parameters for ~0.75 $\mu$ m GaAs MESFET with drain bias $V_{DS} = 4V$ and gate bias $V_{GS} = -2.6V$ . For clarity of presentation, normalization is performed to values at 9.65 GHz and smoothing follows. There are very low levels of dispersion up to 10 GHz for all parameters. (Low frequency dispersion is related to measurement noise.) The exceptionally large relative error in C <sub>GD</sub> corresponds to a ~5 fF absolute error compared with the >100 fF total device capacitance. |

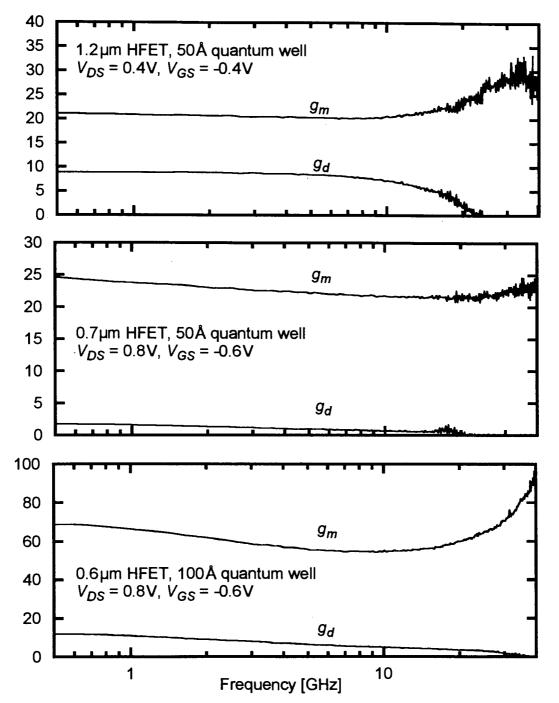

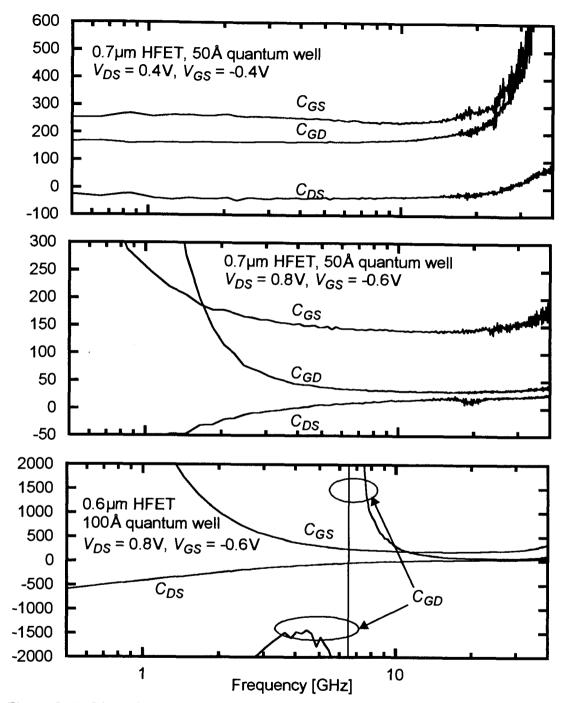

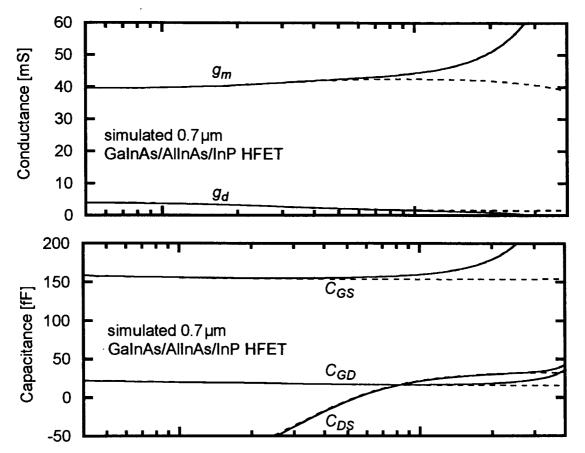

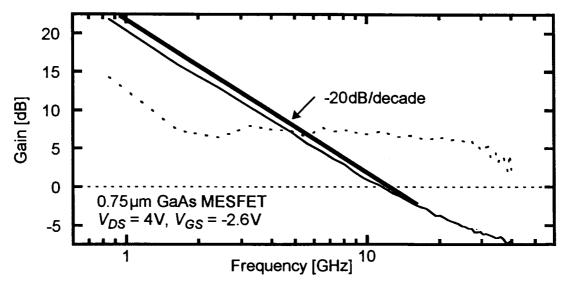

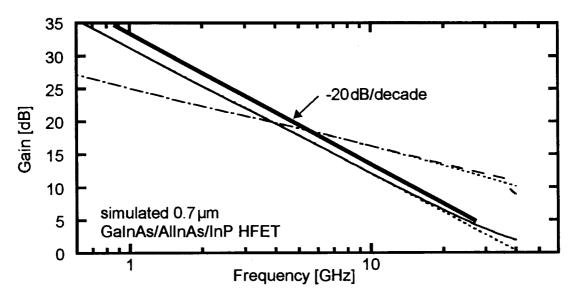

- Figure 5-17 : Dispersion curves calculated from fit parameters published for  $0.7 \mu m$  GaInAs/AlInAs/InP HFET in [58]. Solid lines represent the full model, while dashed lines have all parasitic inductances set to zero. The full dispersion curves resemble the dispersion curves of the  $V_{DS} = 0.4 V$ ,  $V_{GS} = -0.4 V 1.2 \mu m$  InAs/AlSb HFET, i.e. the measurement showing the least dispersion because of the low rate of impact ionization. Dispersion of  $C_{DS}$  at low frequencies is mostly due to the leakage conductance term.

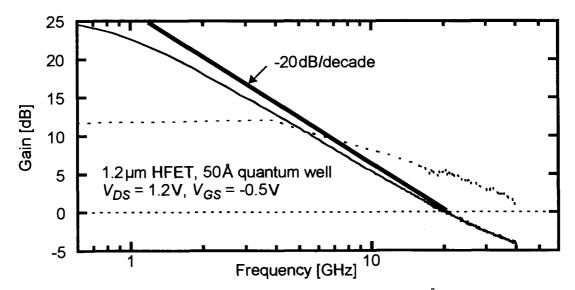

- Figure 5-20 : Peak microwave performance of 1.2 µm gatelength (50 Å quantum well) InAs/ A1Sb HFET.  $V_{GS} = -0.5 V$ ,  $V_{DS} = 1.2 V$ . Solid line:  $|H_{21}|^2$ ; dotted line: MSG/MAG. A -18 dB/decade roll-off from about 2 to 18 GHz dominates below the extrinsic  $f_T = 20 GHz$  ( $f_{MAX} = 45 GHz$ ). Unsmoothed measured data shown. . . . . . . 101

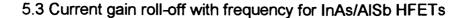

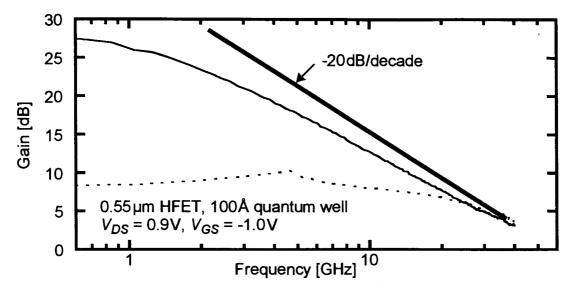

- Figure 5-21 : Peak microwave performance of 0.55  $\mu$ m (100Å quantum well) InAs/AlSb HFET.  $V_{GS} = -1.0 \text{ V}$ ,  $V_{DS} = 0.9 \text{ V}$ . Solid line:  $|H_{21}|^2$ ; dotted line: MSG/MAG. A -16dB/decade rolloff from about 4 to 40 GHz dominates, with no apparent conventional inductive effects on the current gain to 40 GHz. Measured  $f_T = 56 \text{ GHz}$ ,  $f_{MAX} = 58 \text{ GHz}$ , intrinsic  $f_T \sim 67 \text{ GHz}$ . Unsmoothed measured data shown.

| Figure 6-1 : Cross-section of proposed InAs/AISb HFET grown on CU substrate with      | th an |

|---------------------------------------------------------------------------------------|-------|

| LT-GaAs buffer layer (not to scale).                                                  | 108   |

| Figure A-1 : Demonstration of inconsistent resolution obtained at two different parts | s of  |

| same wafer when no edge bead removal is performed.                                    | 114   |

|                                                                                       |       |

# CHAPTER 1 Introduction

# Overview

In this introductory Chapter, we briefly review the basics of III-V compound semiconductor high-speed metal semiconductor field-effect transistors (MESFETs) and heterostructure field-effect transistors (HFETs). The concept of modulation efficiency developed by Foisy is introduced and used to explain the evolutionary trends in the development of high speed III-V field-effect transistors. Modulation efficiency provides a useful framework to demonstrate the potential advantages of the InAs/AlSb material system for low-power HFET applications. Previous works, and works performed concurrently by other groups on the InAs/AlSb system are then briefly reviewed. Finally, the scope of the present dissertation is summarized.

# 1.1 Compound semiconductor MESFETs & HFETs

The transistor can generally be described as a three-terminal electronic device in which the current between two terminals is controlled by the third terminal. In a field-effect transistor, the control electrode is the gate and current flows from the drain to the source in a conductive channel. The gate control is of a capacitive nature, through an insulator or a depletion region, and modulates the conductivity of the charge carrying

channel. Hence, the current through the drain is modulated by the potential applied to the gate.

By far the most widely used transistor technology in use today is the silicon MOSFET (metal-oxide-semiconductor FET). In a MOSFET, the conducting semiconductor channel is capped with an insulating silicon oxide film, and the gate is placed on top of the oxide to either induce or deplete a current-carrying channel between the source and drain electrodes.

Although there is no doubt of the continued dominance of MOSFETs for the vast majority of microelectronics applications, compound semiconductor MESFETs (metal semiconductor FETs, with a Schottky barrier in place of the oxide layer of MOS-FETs) and HFETs (heterostructure FETs, like a MESFET but with the channel defined by at least one heterointerface between two different semiconductors) have carved out a niche in two important markets: optoelectronics, and microwave and millimeter wave (i.e. very high speed) applications. The explanation for the former is that silicon is an indirect band-gap material characterized by a very low optical emission quantum efficiency: as such, it is unsuitable in the context of monolithically integrated light emitters and transistors. The high electron mobility and peak velocity of direct gap compound semiconductors makes them attractive for the fabrication of high speed electronic devices, with the added advantage of the possibility for band gap engineering. Once the relevant factors are considered, the InAs/AISb material system emerges as an excellent candidate for the realization of the ultimate high frequency transistor, if certain technological problems can be solved.

| Material | Energy<br>gap<br>(eV) | Transition type<br>and symmetry<br>points  | Mobility:<br>electrons | Mobility:<br>holes | Electron drift<br>velocity<br>(10 <sup>7</sup> cm/s) |

|----------|-----------------------|--------------------------------------------|------------------------|--------------------|------------------------------------------------------|

| Si       | 1.12                  | indirect: $\Gamma_{25'v} - \Delta_{1c}$    | 1,350                  | 480                | ~1 <sup>b</sup>                                      |

| Ge       | 0.66                  | indirect: Γ <sub>8ν</sub> –L <sub>6c</sub> | 3,600                  | 1,800              |                                                      |

| AlAs     | 2.15                  | indirect: $\Gamma_{15v} - X_{1c}$          | 280                    | ~200 <sup>c</sup>  |                                                      |

| AISb     | 1.58                  | indirect: $\Gamma_{15v} - \Delta_{1c}$     | 900                    | <400               |                                                      |

| GaP      | 2.26                  | indirect: $\Gamma_{15v} - \Delta_{1c}$     | 300                    | 150                |                                                      |

| GaAs     | 1.42                  | direct: Γ <sub>8ν</sub> –Γ <sub>6c</sub>   | 5,000-8,000            | 300                | 1.8 <sup>d</sup>                                     |

| GaSb     | 0.72                  | direct: Γ <sub>8ν</sub> –Γ <sub>6c</sub>   | 5,000                  | 1,000              |                                                      |

| InP      | 1.35                  | direct: Γ <sub>8ν</sub> –Γ <sub>6c</sub>   | 4,500                  | 100                | 2.4 <sup>d</sup>                                     |

| InAs     | 0.36                  | direct: Γ <sub>8ν</sub> –Γ <sub>6c</sub>   | 20-30,000              | 450                | 3.5 <sup>d</sup>                                     |

| InSb     | 0.17                  | direct: Γ <sub>8ν</sub> –Γ <sub>6c</sub>   | 80,000                 | 450                | 6.1 <sup>e</sup>                                     |

| Table 1-1 : Material | properties of selected semicon | ductors at 300 Ka |

|----------------------|--------------------------------|-------------------|

|                      |                                |                   |

a. From Sze [68] except where otherwise indicated

b. Saturated electron velocity [17]

c. From Madelung [44]

d. Peak electron velocity [17]

e. Saturated electron velocity [77]

Consideration of the bulk electronic properties such as the peak velocity and the low-field mobility of various semiconductors (see Table 1-1) leads one to anticipate that compound semiconductors should be suitable for the fabrication of high-speed field-effect transistors. Another advantage of compound semiconductors is that semi-insulating GaAs substrates are widely available, facilitating the integration of microwave circuit elements, such as low-loss spiral inductors and waveguides. Because of the unavailability of high-quality III-V compound semiconductor surface oxides, compound semiconductor FETs have instead relied on rectifying Schottky metal-semiconductor contacts to implement the control terminal. The geometry of a typical n-channel MESFET is given in Figure 1-1, and representative drain current-voltage characteristics for a GaAs MESFET fabricated by the author in the SFU Compound Semiconductor Device Laboratory (CSDL) are shown in Figure 1-2.

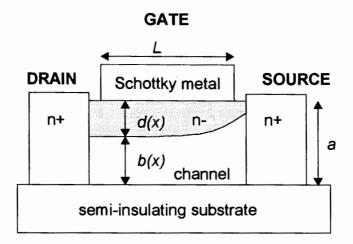

Figure 1-1: Schematic cross-section of a conventional MESFET.

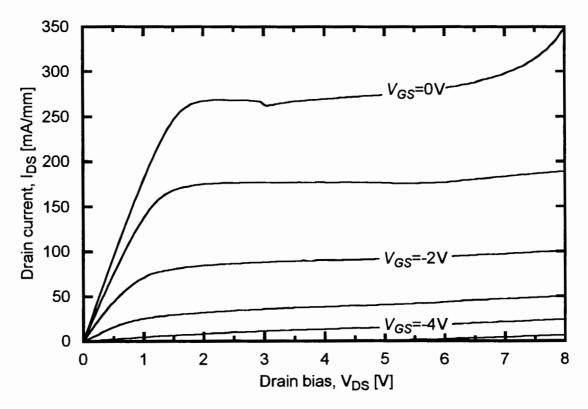

Figure 1-2: Representative I-V characteristics of a GaAs MESFET fabricated in the CSDL.

In an n-channel MESFET, an Ohmic contact at the source supplies the electrons to the conducting channel underneath the gate; conventional current flows from the drain to the source. Electrons are confined to the channel by Coulombic forces either by an insulating substrate, or by p-doping the buffer layers. Under bias, the Schottky contact at the surface results in a depletion region of varying thickness d(x) because of the varying gate-channel bias along the length of the channel, as shown in Figure 1-1. The gate bias therefore controls the cross-section of the channel, and the channel opening is shown to be [40]:

$$b(x) = a \left( 1 - \sqrt{\frac{V_{bi} - V_{GS} + V(x)}{V_P + V_{bi}}} \right)$$

(1-1)

Here  $V_P + V_{bi}$  represents the total reverse voltage required to close (or "*pinch off*") the channel completely. Increasing drain biases lead to channel pinch off at the drain side of the gate and result in a saturation of the drain current.

Another current saturation mechanism is possible in III-V FETs because of the high electron mobility. In a high mobility material, electrons are quickly accelerated according to

$$v_{drift} = \mu E \tag{1-2}$$

where  $\mu$  is the low-field mobility, and E is the electric field. For fields exceeding a given critical value  $E_{sat}$  the velocity saturates at  $v_{sat}$ . To a first approximation, the drift velocity dependence upon electric field can be represented by the piecewise linear relation:

$$v = \begin{cases} \mu E, E < E_{sat} \\ \text{or} \\ v_{sat} = \mu E_{sat}, E \ge E_{sat} \end{cases}$$

(1-3)

Because of current continuity (assuming to first order zero gate leakage current), the drain current per unit channel width is given by:

$$I_{DS} = qnb(x)v(x) \text{ [mA/mm]}$$

(1-4)

where v(x) is the electron velocity in the channel as a function of position, *n* is the charge density in the channel and *b* is the channel thickness at *x*. With current constant along the channel, and a peak electron velocity v(x) equal to the saturated electron velocity, the current through the channel can saturate before channel pinch off occurs at the drain end. A classical example of this behavior is seen in Figure 1-2: the drain current  $I_{DS}$  saturates at  $V_{DS} \sim 2V$  for  $V_{GS} = 0V$ , while the channel pinch-off voltage is  $V_{GS} \sim -4.5V$ .

Assuming that transport occurs under velocity saturation through the whole channel results in a uniform channel cross-section:

$$I_{DS} = qnbv_{sat} \tag{1-5}$$

The current drive capability of a FET is determined by its transconductance

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}} \tag{1-6}$$

Rewriting the drain current as [62]

$$I_{DS} = qnbv_{eff} \approx \frac{Q_G v_{eff}}{L}$$

(1-7)

where  $Q_G$  is the charge under the gate normalized to unit transistor width, the transconductance is found to be

$$g_m \approx \frac{\partial Q_G v_{eff}}{\partial V_G} \frac{v_{eff} C_G}{L} \approx \frac{v_{eff} C_G}{L} \approx \frac{v_{sal} C_G}{L}$$

(1-8)

Here  $C_G \approx C_{GD} + C_{GS}$  is the total gate capacitance, L is the gate length, and  $v_{eff}$  is the effective velocity of electrons in the channel. When velocity saturation prevails over most

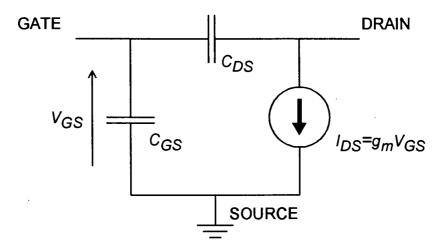

of the channel we can approximate  $v_{eff} = v_{sat}$ : this assumption is often made and justified on the basis of the high mobilities in direct gap III-V compound semiconductors. By examining the simplified *small-signal equivalent circuit* of the MESFET it becomes clear that for high-frequency performance the transconductance must be maximized to quickly charge device (and parasitic) capacitances (see Figure 1-3).

Figure 1-3: Simplified small-signal equivalent circuit of MESFET or HFET.

A quantity of particular interest is the unity current gain cutoff frequency  $f_T$  of the FET. It is defined as the frequency at which the magnitude of the input current equals the magnitude of the output current when the output is short-circuited to ground. It is easily shown to equal

$$f_T = \frac{g_m}{2\pi (C_{GS} + C_{GD})} \approx \frac{v_{sat}}{2\pi L}$$

(1-9)

From this equation, it would seem that improving the transport properties of electrons in the channel (i.e. increasing  $v_{eff} \sim v_{sat}$ ) and reducing the FET gate length L should proportionately increase the cutoff frequency. It should be emphasized that this is the maximum possible  $f_T$  of a FET. The saturated velocity is fixed by the choice of materi-

als through their band structure, while the gate length L is limited by technological considerations.

In practical devices, however, as the aspect ratio of gate length to channel thickness L/d is reduced with shrinking gate length, the device begins to suffer from non-idealities collectively known as "short-channel effects." effectively, the gate loses control of the channel current. For example, an abrupt increase in output conductance appears at higher drain voltages (the kink effect). These non-ideal effects are with few exceptions<sup>1</sup> deleterious to device performance and lead to such non-idealities as a shift of threshold voltage with gate length and increased output conductance in the saturation regime. Such short-channel effects can be reduced by scaling the channel with the gate length. Thinner channels, however, require proportionally higher doping densities to maintain the drain current density. Unfortunately, increased ionized impurity scattering reduces the low-field mobility and the effective electron velocity  $v_{eff}$  in the channel. Clearly, there are diminishing returns to be gained by thinning channels when bulk material properties are relied upon.

The demonstration of modulation doping in AlGaAs/GaAs heterojunctions by Dingle [24] permitted the realization of high mobility high concentration electron gases in narrow *undoped* semiconductor layers, thus allowing higher FET aspect ratios with heterostructures. The term "modulation doping" specifically refers to the spatial separation between parent dopant impurities and the resulting free carriers. This is accomplished as follows: Two semiconductors are placed in intimate contact across a high-quality interface. The material with the higher conduction band edge energy (and generally the wider bandgap) is doped with donors, and the narrower gap semiconductor remains undoped. As a result, electrons accumulate in the undoped material until the Coulombic interactions

<sup>1.</sup> one exception being deep-submicron FETs with ballistic and velocity overshoot effects, which can yield  $v_{eff} > v_{sat}$  because the peak velocity  $v_{peak}$  can be several times  $v_{sat}$

between the accumulated electrons and the ionized donors cause the net potential energy to be minimized. Because of the dynamic confinement of electrons in the direction perpendicular to the interface, a quasi-two dimensional electron gas (2DEG) is formed and is free to move in the interface plane.

With the high mobilities (>5000 cm<sup>2</sup>/Vs) and 2DEG conductivities possible with modulation doping, several groups designed FETs using modulation-doped layers as conducting channels [47][23]. For a number of years development proceeded under the assumption that higher mobilities alone would lead to improved FET performance (the assumption arose from large high frequency performance (cutoff frequency) improvements observed at cryogenic temperatures which coincided with mobility enhancements in GaAs/AlGaAs quantum wells). It was not until Foisy [30] introduced the concept of modulation efficiency that it was fully understood that the improvements to the low-field transport properties in the channel due to the modulation doping were only partly responsible for the improved high-frequency performance of FETs. For this reason, the term "HEMT" for "High electron mobility transistor" is somewhat misleading, and the more descriptive "HFET" for "Heterostructure FET" is preferred in this dissertation.

The increase in  $f_T$  achieved through the use of heterostructures in FETs can be understood by examining the concept of modulation efficiency [30]. Modulation efficiency is a simple technique of accounting for the difference between actual and measured device performance, by incorporating all non-idealities in a single coefficient  $\eta$ . Foisy's analysis was developed for HFETs, but the concept also helps explain the high-frequency performance behavior of MESFETs. The transconductance in equation (1-8) was calculated under the assumption of complete velocity saturation in the channel. Foisy showed that in practice it is important to consider the unsaturated regions of the channel as well: this can be done in a first order approximation by using the piecewise-linear saturated velocity model (1-3). The drain current can be shown to equal [56]:

$$I_{DS} = C_G v_{sal} (\sqrt{(E_{sal}L)^2 + (V_G - V(0) - V_{th})} - E_c L)$$

(1-10)

where the bias V(0) is the channel voltage at the source end of the gate,  $V_{th}$  is the threshold voltage and  $E_{sat}$  is the velocity saturation electric field. From this, using the definition for transconductance (1-6), we find

$$g_m = C_G v_{sat} \frac{V_G - V(0) - V_{th}}{\sqrt{(V_G - V(0) - V_{th}) + (E_{sat}L)^2}}.$$

(1-11)

If one expresses the independent parameter  $V_G$  in terms of the sheet concentration  $n_s$  in the linear approximation, using the definition  $qn_s = C_G(V_G - V(0) - V_{th})$ , and the difference  $n_c$  between the sheet densities at the drain and source ends of the gate:

$$n_c \sim n_s(0) - n_s(L) = E_{sal}C_G/q$$

(1-12)

then the transconductance becomes

$$g_m = C_G v_{sat} \frac{1}{\sqrt{1 + (n_c/n_s)^2}}$$

(1-13)

where the second term is the modulation efficiency:

$$\eta = \frac{1}{\sqrt{1 + (n_c/n_s)^2}}$$

(1-14)

For the sake of simplicity, the above model does not include another important nonideality in a FET: the modulation of parasitic low-mobility current component that can flow outside the quantum well. Foisy expressed the modulation efficiency as [30]:

$$\eta = \frac{\partial Q_{SVM}}{\partial (Q_{SVM} + Q_{\Delta GC} + Q_{SL})}$$

(1-15)

The charge  $Q_{SVM}$  represents the charge required to provide the measured drain current under the saturated velocity model:

$$Q_{SVM} = \frac{I_D L}{v_{sat}}$$

(1-16)

$Q_{\Delta GC}$  denotes the charge required to account for the non-constant velocity in the channel.  $Q_{SL}$  denotes additional parasitic charge present outside the conducting channel, but located in the electron supply layers which normally consist of very low mobility material which behaves as a parasitic MESFET layer.  $Q_{SL}$  must be determined by a self-consistent numerical solution to the Poisson and Schroedinger equations along the gate electrode. The current gain cutoff frequency  $f_T$  becomes:

$$f_T = \frac{v_{sat}}{2\pi L} \times \frac{\partial Q_{SVM}}{\partial (Q_{SVM} + Q_{\Delta GC} + Q_{SL})}$$

(1-17)

From (1-15) we see that modulation efficiency must be in the range  $0 \le \eta \le 1$ . In the best case, all charge that is modulated by the gate bias is in fact in the conducting channel and moving with velocity  $v_{sat}$ .

Let us now consider how to improve the modulation efficiency in HFETs. The fundamental principle to be taken away from (1-14) and (1-17) is that we must maximize the fraction of modulated charge that is actually in the conducting channel. Any charge that accumulates in low-mobility barrier layers reduces the modulation efficiency. For electrons, the conduction band discontinuity determines the maximum sheet concentration  $n_{sm}$  that can be confined before electrons begin to populate the barrier layers. Furthermore, when there is no parasitic charge modulation, the modulation efficiency is still reduced due to the presence of an unsaturated portion of the channel as indicated in (1-14).

To maximize the cutoff frequency of HFETs one therefore seeks a material combination that allows excellent transport properties (for both high low-field mobility and a high  $v_{sat}$ ), and a large conduction band discontinuity (for an excellent electron confinement, the highest maximum sheet charge concentration, and a good modulation efficiency). As seen below, these optimal conditions are met in the InAs/AlSb material

system. Historically, higher modulation efficiencies were achieved adding In to GaAs quantum wells to form strained AlGaAs/GaInAs quantum wells on GaAs substrates, and subsequently, by the development of lattice-matched ( $\Delta E_C = 0.52 \text{ eV}$ ) and strained GaInAs/AlInAs quantum wells on InP substrates.

# 1.2 InAs/AISb HFETs

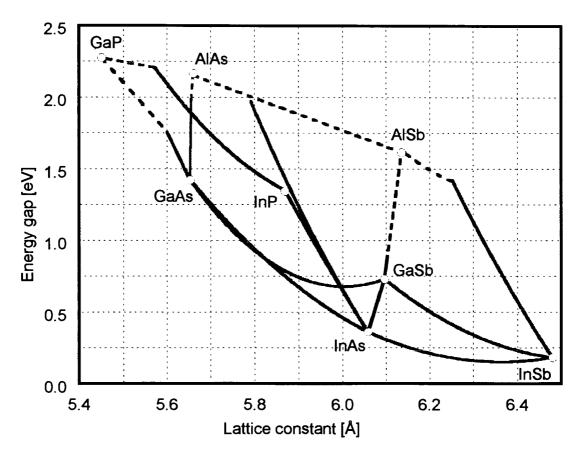

The accepted bulk band gaps and lattice constants of III-V compounds are shown in Figure 1-3. As highlighted in the Figure, the largest difference in band gaps among a single nearly lattice matched material family is within the 6.1Å family: AlSb/GaSb/InAs. What is of special interest, however, is the band lineup at interfaces

Figure 1-4 : Energy gap vs. lattice constant for III-V compound semiconductors of most interest. The 6.1Å family is blackened.

between two of these materials. From the valence band offset for the InAs/GaSb  $(E_{v,InAs/GaSb} \sim 0.5 \text{ eV})$  and AlSb/GaSb  $(E_{v,AlSb/GaSb} \sim 0.35-0.40 \text{ eV})$  interfaces and from the energy gaps of AlSb  $(E_{gap,AlSb} \sim 1.58 \text{ eV})$  and InAs  $(E_{gap,InAs} \sim 0.36 \text{ eV})$ , a slightly staggered band configuration  $E_{v,InAs/AlSb} = E_{v,InAs/GaSb} - E_{v,AlSb/GaSb} \sim 0.10-0.15 \text{ eV}$  and  $E_{c,InAs/AlSb} = E_{v,InAs/AlSb} + (E_{gap,AlSb} - E_{gap,InAs}) \sim 1.32-1.37 \text{ eV}$  is predicted by the transitivity postulate [50]. This has been confirmed experimentally by Nakagawa *et al.* [50] who measured a conduction band offset of  $\sim 1.35 \text{ eV}$ . Dandrea *et al.* [21] theoretically showed that the 1.6% lattice mismatch strain in InAs/AlSb heterojunctions results in a strain-induced narrowing of the InAs gap, leading to a valence band discontinuity of approximately  $\sim 0.04-0.10 \text{ eV}$ . The currently accepted band lineup used in this study is given in Figure 1-5.

Figure 1-5: Basic band structure of HFET active layers used in this study.

The very deep quantum well for electrons provided by this material system and the high mobility of InAs at room temperature present a favorable combination of material properties unmatched by any other III-V heterostructure system. As shown by Bolognesi [5], mobilities of 20,000-30,000 cm<sup>2</sup>/V·s are readily achievable for quantum wells of widths of 100-150 Å.

#### 1.2.1 Difficulties with InAs/AISb HFETs

There are certain difficulties inherent to the InAs/AlSb material system that must be addressed in any study of this type:

a) First and foremost is the abrupt increase in output conductance (the kink effect) in InAs/AlSb HFETs operated at drain biases higher than  $V_{DS} \sim 0.5$ V: see Figure 3-8 on page 48 for example. The appearance of the kink effect has been related to impact ionization in the channel and it has been suggested that traps in buffer layers may interact with the generated holes to amplify the kink effect [39]. The narrow bandgap of InAs coupled with the presumed high trap density in the AlSb barriers make the kink effect particularly noticeable in this material system. Deep levels, which are not completely understood in well-characterized systems, have not yet been identified for InAs/AlSb HFETs. Their effect on device performance also remains unclear. Major portions of the present dissertation address impact ionization and trapping phenomena in InAs/AlSb HFETs.

b) AlSb oxidizes readily in ambient air and is etched relatively easily by alkaline solutions compared to most semiconductors. Because standard photolithographic developers are alkaline, precautions are required to avoid unintended etching of AlSb. The use of InAs/GaSb bilayer caps and the introduction of small quantities of Ga into AlSb layers together can alleviate these problems.

c) This remains a new technology, compared with the InP and GaAs lattice matched material systems. The anticipated high-frequency performance advantage of InAs-based HFETs has yet to be fully reached.

#### 1.2.2 Other work on InAs/AISb HFETs

The fact that InAs/AlSb quantum well HFETs (Figure 1-5 on page 13) provide the deepest quantum wells and highest mobilities of any lattice-matched material sys-

- 14 -

tem has generated some interest from the research community [19]. The first report of InAs/AISb HFETs was made by the Santa Barbara group [71]. Because the growth and fabrication technology for devices using this material system was still in its infancy, that and another early work [84] should be considered as proof-of-concepts. At that time, the reasons for the successes and shortcomings of the devices were not understood.

The first breakthrough came with Tuttle's success in growing high mobility InAs/AlSb quantum wells [72][73]. His identification of the role of shutter sequencing at AlSb-InAs interfaces and the effects on the low-field electronic transport properties of the quantum wells paved the way for achieving the transport properties now available in InAs/AlSb quantum wells.

Several groups contributed to the "first generation" of InAs/AlSb HFETs. Still at Santa Barbara, Werking and Bolognesi continued building on the work of Tuttle. Werking *et al.* [78] demonstrated that Ar ion-implantation failed to provide adequate device isolation, and also investigated reactive ion etching schemes for the material system [79]. Yoh *et al.* [84] reported the first successful channel pinch-off in InAs/AlSb HFETs operating at room temperature. Their devices were plagued by a severe kink effect. Nearly kink-free devices were later reported by Wang's group at Columbia University [42], but no satisfactory explanation for the absence of the kink was provided. It was speculated that their undoped structure may have benefited from unintentional (and irreproducible) charge compensation from a high background Te contamination in their MBE chamber.

The breakthrough in the reliable fabrication of InAs/AlSb HFETs with improved DC and microwave characteristics came with the Ph.D. work of Bolognesi [5]. The growth of high mobility InAs/AlSb quantum wells (continuing the work of Tuttle [72]) was improved and made more reproducible, and a reliable process for the fabrication of InAs/AlSb HFETs was developed. Some of the HFET gate leakage current was shown

to arise from impact ionization in the channel, and the kink effect was tentatively explained as resulting from the accumulation of impact ionization generated holes in the buffer layers. This work was followed by Brar *et al.* [13] who furthered the understanding of the kink effect through the demonstration of the effect of back-gating on the kink. In his Ph.D. dissertation, he also presented evidence that the gate diode leakage current can be largely due to thermionic emission of holes generated at the InAs/AISb interface [12].

Among other groups currently active in this field, the group at Naval Research Laboratories has many published results for InAs/AlSb HFETs [6]-[11],[37],[38]. They have demonstrated the smallest gate geometries this material system, and have reported novel successful Ohmic contact schemes. The NRL group has claimed a 50 GHz·µm performance with 0.5µm HFETs, but has been unsuccessful in maintaining this performance in 0.1-0.2 µm HFETs. They have provided no explanation for this failure. The Columbia University group recently published results on an Ohmic contact study [85] which was not of the quality of [10]. Of great interest is the recent work by Miya et al. from the Asahi Chemical Industry Co. in Japan, who have applied expertise gained on InAs-based Hall effect sensors to the fabrication of InAs/AlGaAsSb HFETs, avoiding the problem of thick, low-quality AlSb buffer layers [49]. Other relevant InAs-based works include the strain compensated InAs inserted-channel HFETs on InP demonstrated by Xu et al. in Germany [83] and Chin et al. in Taiwan [20]. They have matched or exceeded the best microwave performance of InAs/AlSb HFETs: with a ~50 GHz·um frequency performance at longer gatelengths  $L > 0.5 \,\mu\text{m}$ , and  $\sim 35 \,\text{GHz} \cdot \mu\text{m}$  at shorter gatelengths, an  $f_T = 265 \text{ GHz}$  was reported for a 0.13 µm gatelength device [83]. The InAs inserted-channel HFET on InP is a direct challenge to the AlSb/InAs/AlSb deep quantum well HFET, because the approach takes advantage of the high mobility and saturated velocity of InAs while maintaining the technological benefits of better-known InP materials.

#### 1.3 Scope of dissertation

# 1.3 Scope of dissertation

The mandate of this research is, in broad terms, to advance the development and understanding of InAs/AISb HFETs. Attempts to minimize the kink effect were made by implementing dual-gate HFETs and by increasing the impact ionization threshold by using thinner InAs quantum wells. Because buffer layer traps have been known to influence the characteristics of conventional III-V MESFETs and HFETs, we have studied the effect of buffer layers (and deep levels within the buffer layers) through sidegating measurements which provided the first evidence of the effect of traps on InAs/AISb HFETs. Finally, we have studied the effects of impact ionization on the microwave properties of InAs/AISb HFETs.

Chapter 2 begins with an overview of the device technology that was developed at CSDL in order to reliably produce microwave testable sub-micron gatelength devices. The topics given consideration include: MBE growth of the device structures, fabrication sequence, gate lithography and Ohmic contact metallization.

Chapter 3 discusses impact ionization in InAs/AlSb HFETs. Impact ionization generated holes are responsible for the undesirable kink effect in these devices. In this Chapter, two approaches to reducing the kink are examined: the dual-gate HFET is proposed as a technique for preventing hole accumulation (and the resulting positive electrostatic charge) underneath the control gate; and an attempt is made to reduce the rate of impact ionization by increasing the effective channel energy gap through quantum well engineering.

Chapter 4 presents the first direct evidence for the existence of hole traps in the AISb buffer layer, through the effect of sidegating on the frequency and temperature dependence of current-voltage measurements on InAs/AISb HFETs. The observation of a new sidegating-induced negative differential resistance (SINDR) effect in InAs/AISb 1.3 Scope of dissertation

HFETs is explained by a model that calls for the transient population of hole traps in the buffer layer.

Chapter 5 discusses the measured DC and microwave performance of InAs/AISb HFETs. Comparisons between high mobility, wide quantum well devices and low mobility, narrow quantum well devices demonstrate that low-field mobility in addition to peak electron velocity is extremely important in the high frequency performance of HFETs. Anomalously conductive (inductive) measured input (output) reflection coefficients  $S_{11}$  ( $S_{22}$ ) are connected to high rates of impact ionization. We show that the effects of impact ionization in InAs/AISb HFETs can be so severe that the conventional microwave FET models do not adequately describe the measured device characteristics.

Chapter 6 concludes this dissertation with a summary of the work performed, and provides the scope for future research on InAs/AlSb HFETs. Finally, a list of references is given, and further processing details not mentioned in Chapter 2 are presented in the Appendix.

# **CHAPTER 2 Device Fabrication**

## **Overview**

To study the device physics and measure the microwave performance of InAs/AlSb HFETs, a fabrication process that reliably produces functional submicron gate HFETs is essential. This Chapter describes the implementation of a successful InAs/AlSb HFET fabrication sequence based on a sub-micron optical lithography process.

As discussed in Chapter 1, several groups have been pursuing the development of InAs/AlSb HFETs. The breakthrough came with the Ph.D. work of Bolognesi, who first engineered a reliable and high-yield process based on a combination of selective wet etches [5]. Because that work was confined to the use of photolithographic masks with a feature size  $\geq 1.5 \mu$ m, the process was not optimized for sub-micron geometries. The present work has refined the process to implement sub-micron gate devices by taking advantage of the facilities available at SFU Compound Semiconductor Device Laboratory (CSDL).