# MODELING AND SIMULATION OF SATURATING HOT ELECTRON DEGRADATION IN LDD NMOSFETs -FROM EARLY MODE TO LATE MODE

by

# Arya Raychaudhuri

B.E., Jadavpur University, Calcutta, India, 1981 M.E., Jadavpur University, Calcutta, India, 1983

÷.,

THESIS SUBMITTED IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY in the School of Engineering Science

© Arya Raychaudhuri, 1996

# SIMON FRASER UNIVERSITY

June 1996

All right reserved. This work may not be reproduced in whole or in part, by photocopy or other means, without permission of the author.

National Library of Canada

Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa: Ontario K1A 0N4 395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Volre référence

Our life Notre rélérence

The author has granted an irrevocable non-exclusive licence allowing the National Library of reproduce, Canada to loan. sell copies distribute or of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant la Bibliothèque à nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse la disposition des à personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-17071-3

# Canadä

#### **PARTIAL COPYRIGHT LICENSE**

I hereby grant to Simon Fraser University the right to lend my thesis, project or extended essay (the title of which is shown below) to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its usrs. I further agree that permission for multiple copying of this work for scholarly purposes may be granted by me or the Dean of Graduate Studies. It is understood that copying or publication of this work for financial gain shall not be allowed without my written permission.

#### Title of Thesis/Project/Extended Essay

# <u>"Modeling and Simulation of Saturating Hot Electron Degradation In</u> LDD NMOSFETs - From Early Mode To Late Mode"

Author:

(signature)

Aray Kaychaudhuri (name)

July 10, 1996 (date)

#### APPROVAL

| Name:            | Arya Raychaudhuri                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------|

| Degree:          | Doctor of Philosophy (Engineering Science)                                                                         |

| Title of Thesis: | MODELING AND SIMULATION OF SATURATING<br>HOT ELECTRON DEGRADATION IN LDD<br>NMOSFETs -FROM EARLY MODE TO LATE MODE |

#### **Examining Committee:**

Chair: Dr. S.P. Stapleton Associate Professor School of Engineering Science Simon Fraser University

Dr. M. J. Deen Senior Supervisor, Professor School of Engineering Science Simon Fraser University

Dr. Albert Leung Supervisor, Professor School of Engineering Science Simon Fraser University Dr. R. F. Frindt Supervisor, Professor Department of Physics Simon Fraser University

Dr. E. A. Gutierrez D. Internal Examiner, Visiting Professor School of Engineering Science Simon Fraser University

Dr. K. miewski External Examiner PMC-Sierra, Burnaby British Columbia

Date Approved: June 17, 1996

# ABSTRACT

In this thesis, we report an extensive investigation on the saturating hot-electron degradation effects in sub-micron lightly-doped-drain (LDD) n-channel metal oxide semiconductor field effect transistor (NMOSFET) devices. We have developed a new phenomenological device degradation model based on propagation of hot-electron defects from the sub-spacer silicon-silicon dioxide interface region to the sub-gate interface region. The main implication of this model is that the defects do not accumulate at one point in the device structure, as previously thought, but the defects profile extends into the device with increasing hot-electron stress.

Based on various experimental features of these devices under hot-electron degradation, we have used both analytical modeling and 2-D device simulation within an in-house developed virtual factory environment to delineate the special features of the hot-electron degradation in LDD devices. These features include a sharp rate of early mode degradation, followed by a much lower rate of late mode degradation. The initial degradation is shown to increase the parasitic drain series resistance in the gate-edge subspacer LDD region, thus making the device asymmetric. We therefore developed a simple and general method to extract the asymmetric parasitic source and drain resistances using a single MOSFET and its small signal transconductance and drain conductance data.

Using the floating gate measurement technique, we extracted an interesting evolution in the hot-electron gate currents in the early phase of the degradation which correlated very well with the corresponding evolution in drain parasitic resistances. These evolutions, coupled with corresponding evolutions in substrate currents, linear and saturation drain currents lead to a 2-D simulation framework involving negative trapped charges in the gate-edge interface region in the earlymode degradation situation. Further experiments of the various MOSFET currents during the late mode degradation situation are seen to match very well with simulation results after placement of trapped charges above the sub-gate LDD region. These correlations help us develop an analytical phenomenological model for defects propagation length versus stress time. It is seen that the propagation length saturates with increasing stress time. We then couple this model with defects propagation simulation to actually demonstrate the two-stage transconductance degradation observed in practice.

Finally, we report a simple technique based on evolving saturation drain currents in a progressively stressed MOSFET, to estimate the evolutions in three main parameters of the device, namely, mobility, series resistance, and threshold voltage. This simple technique can be used to update the circuit simulation model parameters for circuit reliability simulations. We expect that the results of this thesis will be useful for developing new hot-electron lifetime prediction methods, better device design, and parametric esimation algorithm.

# DEDICATION

To my parents, my wife Debasree, and my daughter Nirokhi

•

# **ACKNOWLEDGEMENTS**

It is my pleasure to acknowledge the thoughtful guidance provided by Dr. M. J. Deen, my senior supervisor, during the course of this thesis. Without his valuable suggestions, recommendations, and comments, the thesis would not be completed. Special thanks are due to him for getting me in touch with our industrial partners Northern Telecom.

I am specially indebted to Mr. Michael King, Mr. Jaan Kolk, Mr. John Ilowski, Mr. Tom MacElwee, and Dr. Iain Calder among others of the Silicon Components Group at Northern Telecom, Ottawa. I received a great deal of direct assistance and advice form them on various aspects of device measurement, device modeling, and simulation.

I wish to thank Dr. R. F. Frindt and Dr. A. Leung for being on my supervisory committee and providing useful comments and suggestions that helped shape the scope of the thesis. I will also thank Dr. S. Stapleton for chairing my thesis examining committee, Dr. E. A. Gutierrez D. for being the internal examiner, Dr. K. Iniewski for being the external examiner, and Dr. M. Parameswaran for sitting in my examining committee in place of Dr. Leung.

I wish to thank Dr. C. Rey and Mr. R. Marchetto of Glenayre R&D, my present employer for being understanding and encouraging, so that I could use some extra hours to complete this thesis.

Thanks are due to my colleagues, present and past, in the Microelectronic Device Research Laboratory of Simon Fraser University for their direct and indirect assistance during the course of this thesis. Particular mention should be made of W.S. Kwan, Z. X. Yan, C. L. F. Ma, P. Kolev, J. Liang, M. Margarit, A. Ng, T. Hardy, and X. J. Zhao. I owe a special debt to Ms. Brigitte Rabbold, our graduate secretary for being particularly supportive and helpful. Also, my special thanks to Mr. Chao Cheng, our computer system administrator.

I wish to acknowledge the Canadian Commonwealth Scholarship Scheme for providing me with a Commonwealth Scholarship. I also wish to acknowledge the financial support provided by NSERC of Canada and Micronet - a Federal Network Center for Excellence in Microelectronics, as well as Northern Telecom, Ottawa. Also, I thankfully acknowledge the generous financial support provided by both my senior supervisor Dr. M. J. Deen and the Center for Systems Science at Simon Fraser University for presenting parts of this work at various conferences in Canada, U.S., and Europe.

Finally, I wish to thank all the members of the School of Engineering Science at Simon Fraser University for being patient with me. Thanks everybody!

# TABLE OF CONTENTS

| APPROVAL       |                                           | i        |

|----------------|-------------------------------------------|----------|

| ABSTRACT       |                                           | ü        |

| DEDICATION     |                                           | iv       |

| ACKNOWLEDG     | EMENTS                                    | v        |

| TABLE OF CON   | rents                                     | vii      |

| LIST OF TABLES | 5                                         | x        |

| LIST OF FIGURE | S                                         | xi       |

| LIST OF SYMBO  | DLS                                       | xvii     |

|                |                                           |          |

| Chapter 1      | Introduction                              | 1        |

|                | 1.1 Introduction                          | 1        |

|                | <b>1.2</b> Aim of this thesis             | 2        |

|                | <b>1.3</b> Organization of this thesis    | 4        |

|                | References                                | 7        |

| Chapter 2      | Background                                | 10       |

|                | 2.1 Introduction                          | 10       |

|                | 2.2 The MOSFET structure and operation    | 11       |

|                | 2.3 Hot carrier generation                | 15       |

|                | 2.4 Effects of hot carrier generation     | 20       |

|                | 2.5 Modeling of hot carrier               |          |

|                | currents and degradation                  | 23       |

|                | 2.6 The LDD structure and                 |          |

|                | the associated problem                    | 27       |

|                | 2.7 Conclusion                            | 30       |

|                | References                                | 31       |

| Chapter 3      | Finding the asymmetric parasitic source   |          |

|                | and drain resistances from the            |          |

|                | small-signal conductances of              |          |

|                | a single MOS transistor                   | 35       |

|                | 3.1 Introduction                          | 35       |

|                | <b>3.2</b> Derivation for $g_m$ and $g_d$ | 36       |

|                | 3.3 Methodology of extraction:            | 50       |

|                | $R_D$ - $R_S$ from saturation             | 39       |

|                | 3.4 Methodology of extraction:            | 57       |

|                | $R_D + R_S$ from linear region            | 45       |

|                | 3.5 Discussion of accuracy                | 43<br>48 |

|                |                                           | -+0      |

•

|           | 3.5.1 Derivation for $\Delta R_{S1}$<br>3.5.2 Derivation for $\Delta R_{S2}$<br>3.6 Conclusion                              | 48<br>50<br>54 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|----------------|

|           | References                                                                                                                  | 55             |

| Chapter 4 | Experimental features of the early-mode                                                                                     |                |

|           | hot-carrier degradation in                                                                                                  |                |

|           | LDD NMOSFETs                                                                                                                | 57             |

|           | 4.1 Introduction                                                                                                            | 57             |

|           | 4.2 Device details and measurement                                                                                          |                |

|           | instrumentation                                                                                                             | 58             |

|           | 4.3 Degradation measurements                                                                                                | 59             |

|           | 4.4 Experimental Techniques                                                                                                 | 60             |

|           | 4.4.1 Floating gate measurement                                                                                             | 60             |

|           | 4.4.2 Transconductance technique                                                                                            | 66             |

|           | 4.4.3 Charge pumping technique                                                                                              | 70             |

|           | 4.5 Conclusion                                                                                                              | 77             |

|           | References                                                                                                                  | 78             |

| Chapter 5 | <b>Location</b> and quantification of defects<br>using 2-D device simulation and<br>dynamics of defects propagation         | 81             |

|           | 5.1 Introduction                                                                                                            | 81             |

|           | 5.2 Device and simulation details                                                                                           | 82             |

|           | 5.3 The simulation framework                                                                                                | 83             |

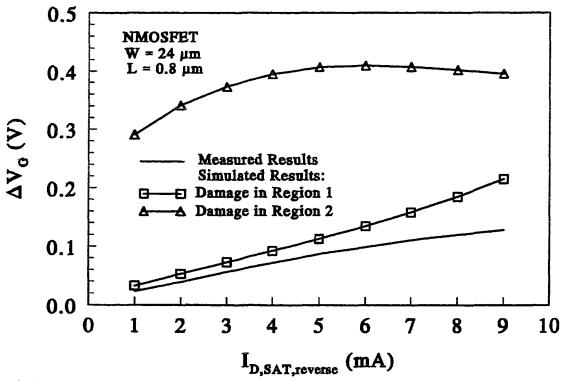

|           | 5.4 Region 1 versus Region 2                                                                                                | 87             |

|           | 5.4.1 Substrate currents                                                                                                    | 87             |

|           | 5.4.2 Linear currents                                                                                                       | 89             |

|           | 5.4.3 Saturation currents                                                                                                   | 90             |

|           | 5.4.4 R <sub>S</sub> increase?                                                                                              | 93             |

|           | 5.4.5 Behavior of substrate currents                                                                                        | 94             |

|           | 5.5 Defects growth model                                                                                                    | 96             |

|           | 5.6 Defects growth simulations                                                                                              | 101            |

|           | 5.7 Conclusion                                                                                                              | 106            |

|           | References                                                                                                                  | 107            |

| Chapter 6 | <b>Extraction of degradation parameters,</b> $\Delta \mu$ , $\Delta V_T$ , and $\Delta R_D$ from a degraded NMOS transistor | 110            |

-

|             | 6.1 Introduction                                          | 110        |

|-------------|-----------------------------------------------------------|------------|

|             | 6.2 Device, stressing, and parameter<br>extractor details | 111        |

|             | 6.3 Method of extraction from                             | 111        |

|             | saturation currents                                       | 112        |

|             | 6.4 Match with experimental curves                        | 117        |

|             | 6.5 Match with extraction from                            | 120        |

|             | linear region<br>6.6 Conclusion                           | 120<br>123 |

|             | References                                                | 124        |

| Chapter 7   | <b>Conclusions and recommendations</b>                    | 125        |

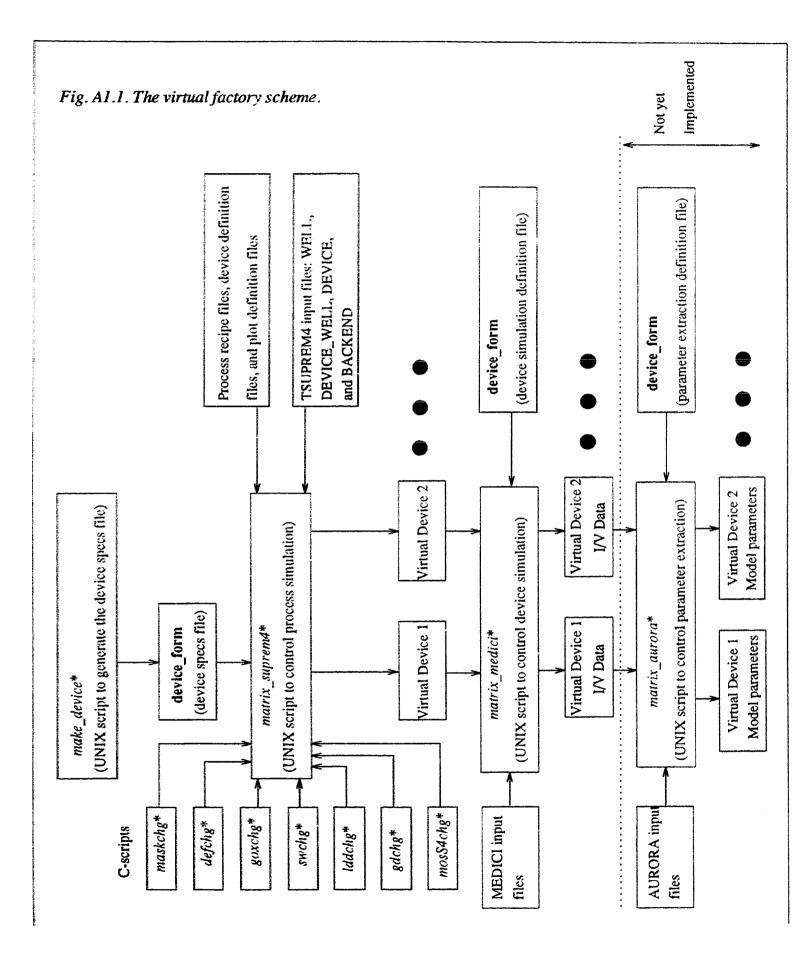

| Appendix 1: | The Virtual Factory Scheme                                | 129        |

|             | I. Introduction                                           | 129        |

|             | <b>II.</b> The Principle of Matrix Process Simulation     | 131        |

|             | <b>III.</b> The Software Framework                        | 131        |

|             | IV. Changes to Original Process Recipes                   | 138        |

|             | V. Matrix Device Simulation                               | 140        |

|             | VI. Matrix Parameter Extraction                           | 141        |

|             | Reference                                                 | 142        |

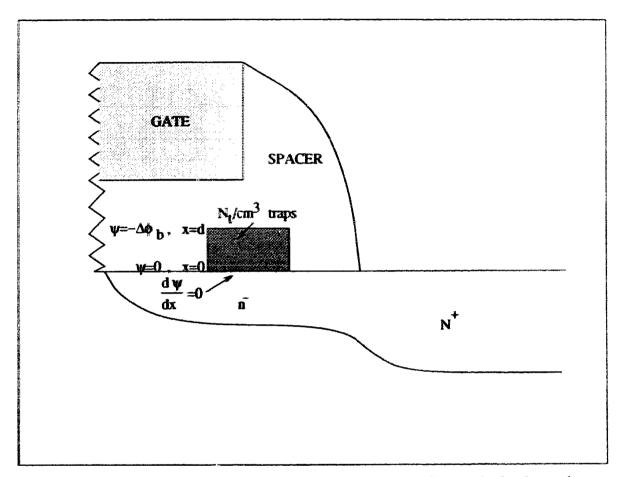

| Appendix 2: | Models for 2-D Simulation                                 | 143        |

|             | I. The basic equations                                    | 143        |

|             | II. The generation recombination process                  | 144        |

|             | III. Bandgap narrowing                                    | 145        |

|             | IV. The mobility models                                   | 146        |

|             | V. Substrate current                                      | 148        |

|             | VI. Gate current                                          | 149<br>152 |

|             | VII. The energy balance equations                         | 152        |

|             | References                                                | 154        |

| Appendix 3: | <b>Derivation of eqns. (5.1) &amp; (5.2)</b>              | 156        |

| Appendix 3: | Publications arising out                                  |            |

|             | of this thesis                                            | 159        |

# LIST OF TABLES

| Table 6.1  | SPICE level 3 parameters for virgin device. | 117 |

|------------|---------------------------------------------|-----|

| Table A1.1 | Parameters for doping dependent lifetimes.  | 145 |

# LIST OF FIGURES

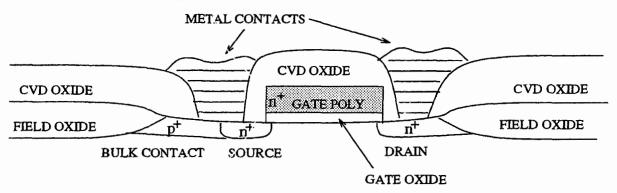

| Fig. 2.1. | (a) The structure of a typical conventional NMOSFET. (b) The corresponding schematic diagram. In general, V <sub>BS</sub> can be at a potential other than ground.<br>12                                                                                                                                                                                                                                                                                      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

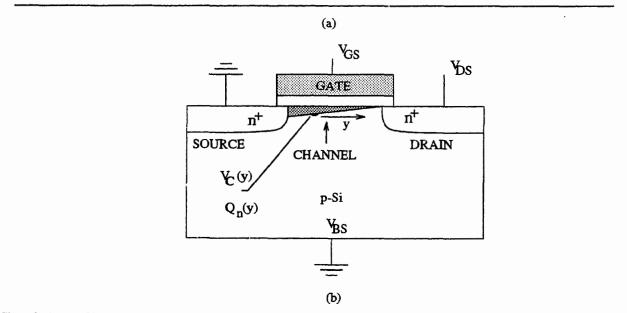

| Fig. 2.2. | Channel potential $V_C(y)$ versus distance y from source for two cases, linear operation of the MOSFET ( $I_{DS}$ =0.4 mA), and near saturation operation ( $I_{DS}$ =1.9 mA) 16                                                                                                                                                                                                                                                                              |

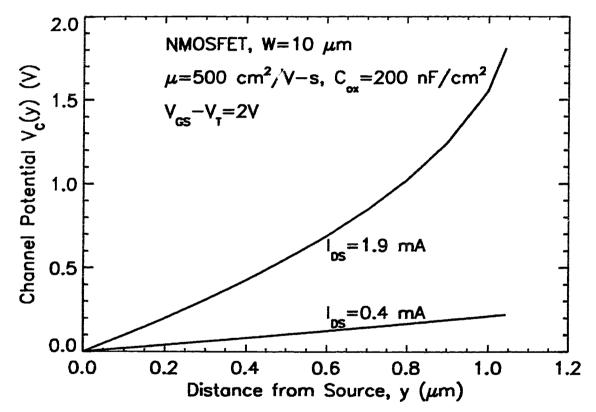

| Fig. 2.3. | Schematic showing energy loss in optical phonon scattering,<br>and redirection by acoustic phonon scattering of electrons<br>moving in the channel of an NMOSFET in two situations<br>hown earlier in fig. 12, (a) linear operation of the MOSFET,<br>and (b) near-saturation operation. Obviously, energy gain of the<br>electron in the second case is higher due to curvature of the<br>bands. These high-energy electrons are termed hot electrons.<br>17 |

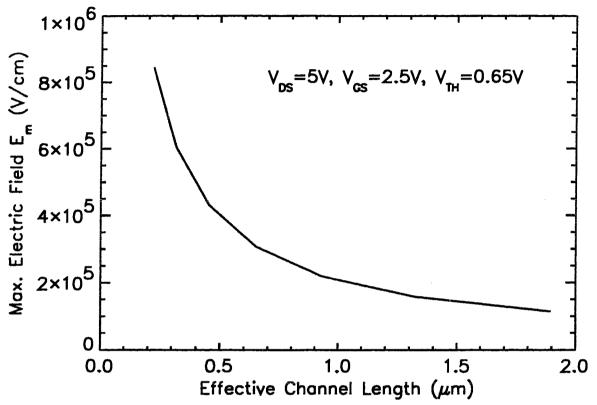

| Fig. 2.4. | Impact of constant-voltage scaling on the maximum channel<br>electric field E <sub>m</sub><br>20                                                                                                                                                                                                                                                                                                                                                              |

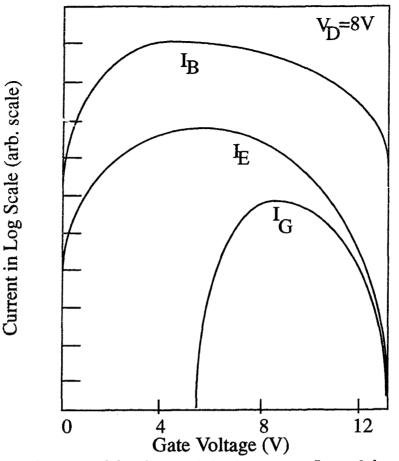

| Fig. 2.5. | 20<br>Schematic diagram of the electron injection current $I_E$ ,<br>and the actual gate current $I_G$ .<br>22                                                                                                                                                                                                                                                                                                                                                |

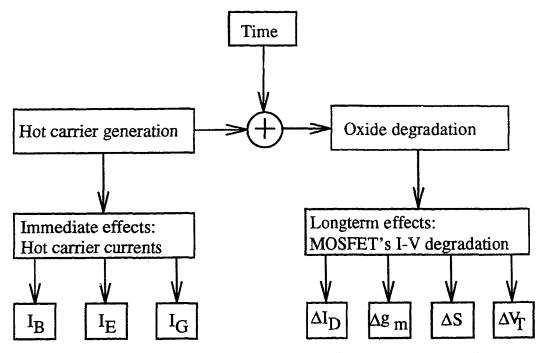

| Fig. 2.6. | Schematic diagram of the effects of hot carrier generation.<br>23                                                                                                                                                                                                                                                                                                                                                                                             |

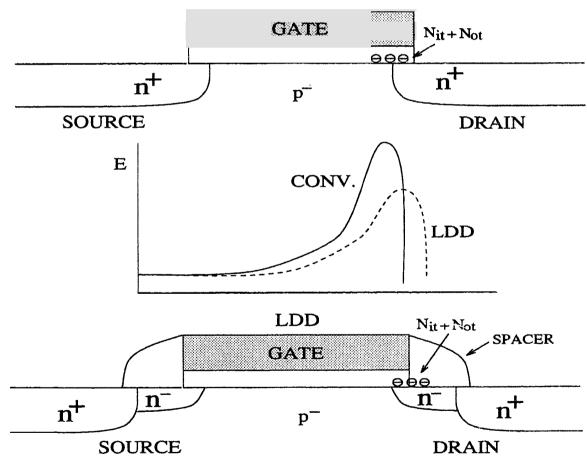

| Fig. 2.7. | Comparison between the conventional and the LDD structures, corresponding lateral electric fields, and degradation modes.<br>27                                                                                                                                                                                                                                                                                                                               |

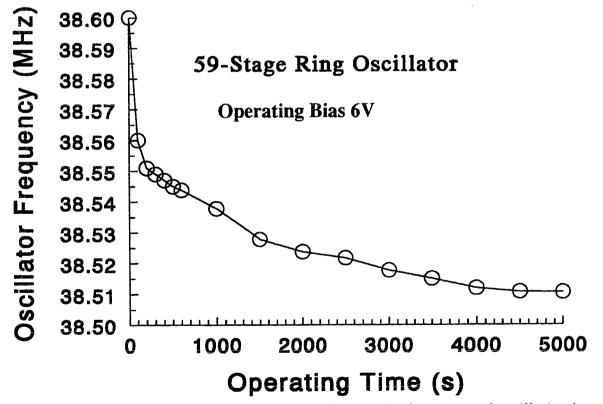

| Fig. 2.8. | Early mode hot-carrier degradation affecting the frequency of oscillation in a 59-stage ring oscillator built with 0.8 mm LDD NMOSFETs.                                                                                                                                                                                                                                                                                                                       |

|           | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

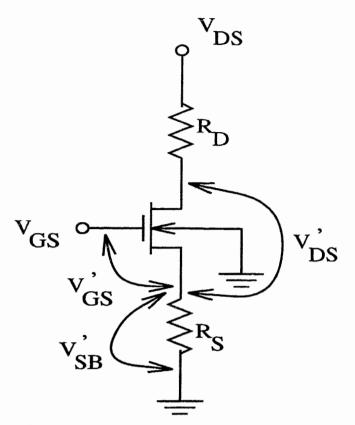

| Fig. 3.1. | The MOSFET (n-channel) with source ( $R_S$ ) and drain ( $R_D$ ) series resistances. The applied voltages ( $V_{GS}$ and $V_{DS}$ ) and the intrinsic voltage drops ( $V_{GS}$ ', $V_{DS}$ ', and $V_{SB}$ ') are also indicated.                                                                                                                                                                                                                             |

|           | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

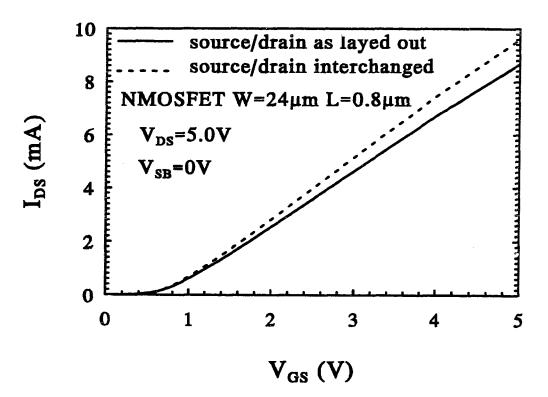

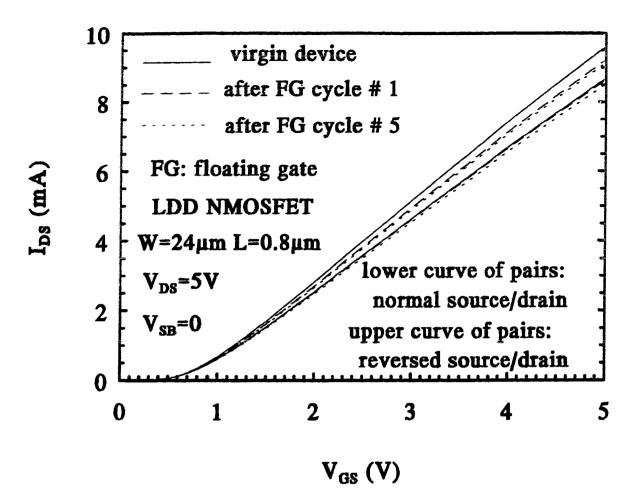

| Fig. 3.2. | Saturation transconductance characteristics of the $V_{DS}$ =5V. The asymmetry in $R_S$ and $R_D$ translates a characteristics with source/drain as laid out and a In this case $R_S$ is greater than $R_D$ .                                | lirectly into these                              |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

|           | 3 8 <i>D</i>                                                                                                                                                                                                                                 | 40                                               |

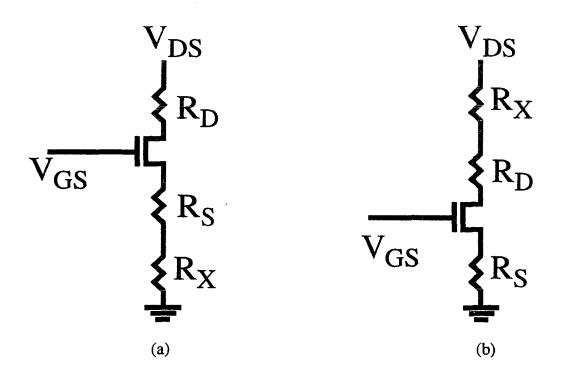

| Fig. 3.3. | (a) Add $R_X$ to Source, measure $g_m$ , call it $g_{mS}$ . (b) measure $g_m$ , call it $g_{mD}$ . Both $g_{mS}$ and $g_{mD}$ are me forward mode at constant $I_{DS}$ .                                                                     |                                                  |

|           |                                                                                                                                                                                                                                              | 41                                               |

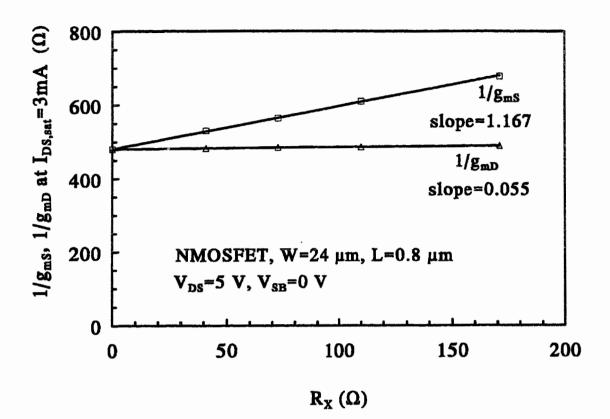

| Fig. 3.4. | $1/g_{mS}$ and $1/g_{mD}$ measured at saturation $I_{DS}$ of 3m straight lines through the points are least-squares measured with $R_X$ on source side and $g_{mD}$ is $g_m$ m on drain side.                                                | fitted. $g_{mS}$ is $g_m$<br>reasured with $R_X$ |

|           |                                                                                                                                                                                                                                              | 43                                               |

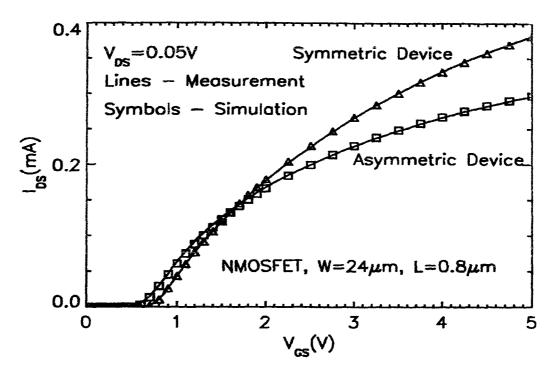

| Fig. 3.5. | Measurement vs. MEDICI simulation of linear cha<br>asymmetric device was simulated with 39 W in ser<br>source of the symmetric MEDICI device. Note that<br>for the asymmetric device.                                                        | ies with the                                     |

|           | jor me usymmetrie device.                                                                                                                                                                                                                    | 45                                               |

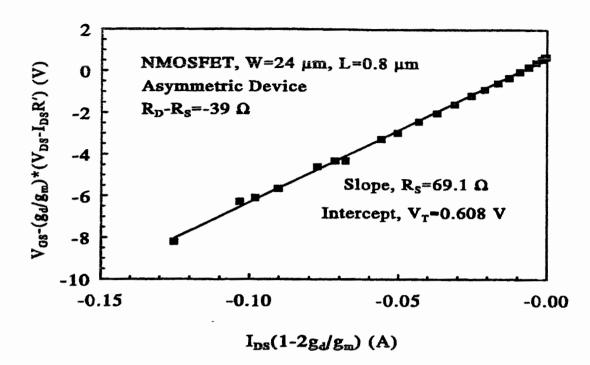

| Fig. 3.6. | $V_{GS}$ - $g_d/g_m(V_{DS}$ - $I_{DS}R')$ versus $I_{DS}(1-2g_d/g_m)$ for outransistor with $R_S > R_D$ . $R'$ is $R_D$ - $R_S$ . $g_d$ and $g_m$ we at 22 equispaced bias points between 0.8 and 5 V. gives $R_S$ and the intercept $V_T$ . | re measured                                      |

| 74 0 4    |                                                                                                                                                                                                                                              |                                                  |

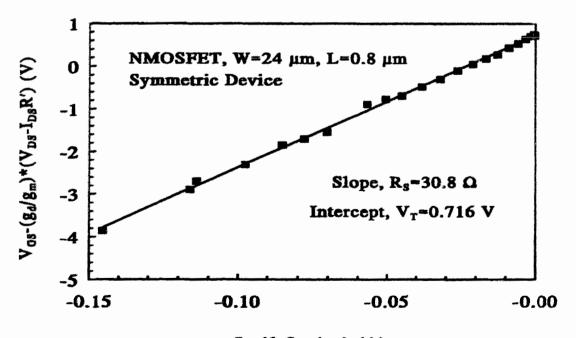

| Fig. 3.7. | The method of fig. 4.6 repeated for a symmetric de                                                                                                                                                                                           | wice.<br>47                                      |

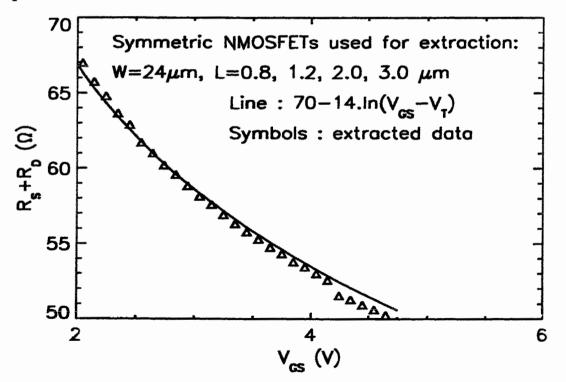

| Fig. 3.8. | The match between the empirical relation for $R_S$ +, extracted values versus $V_{GS}$ .                                                                                                                                                     | 2                                                |

|           |                                                                                                                                                                                                                                              | 52                                               |

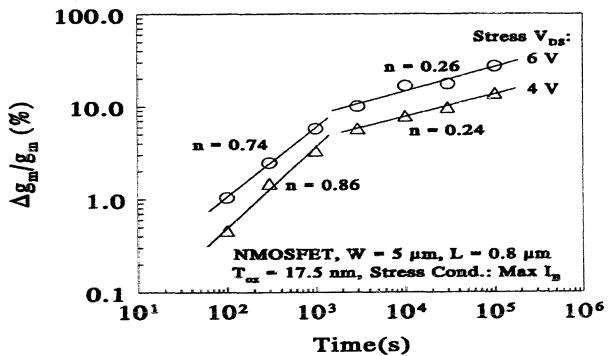

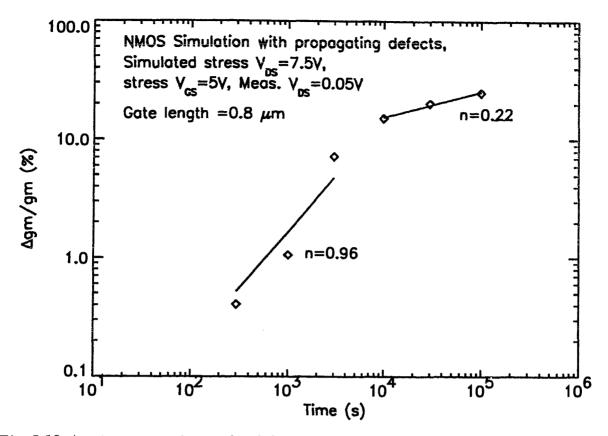

| Fig. 4.1. | Evidence of two-stage hot-carrier degradation in a LDD NMOSFET characterized by a sharp rate () degradation, and a much slower rate (low n) after                                                                                            | high n) of initial                               |

|           |                                                                                                                                                                                                                                              | 59                                               |

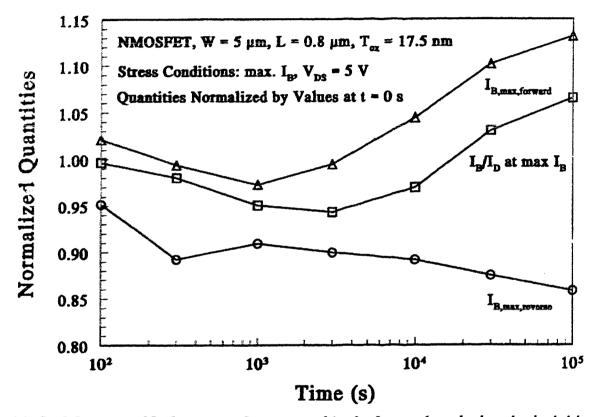

| Fig. 4.2. | Both $I_{B,max}$ and $I_B/I_D$ at max. $I_B$ measured in the form drop in the initial phase. In the reverse mode, $I_{B,m}$ way as in conventional degradation.                                                                              |                                                  |

|           |                                                                                                                                                                                                                                              | 60                                               |

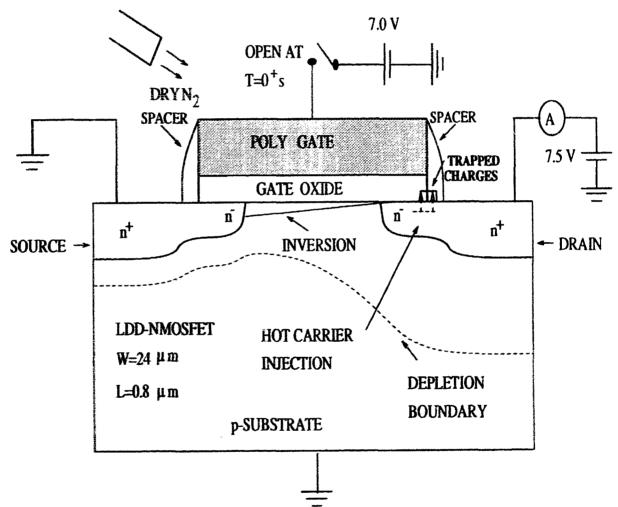

| Fig. 4.3.  | The schematic diagram for the floating gate measure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <i>ement</i> .<br>61 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

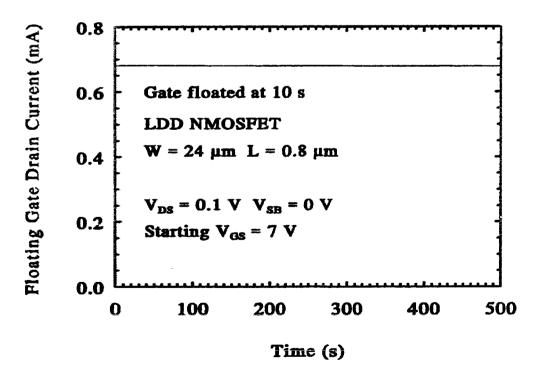

| Fig. 4.4.  | Floating gate measurement with the MOSFET biase<br>linear region to check for leakages from gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | d in th?<br>62       |

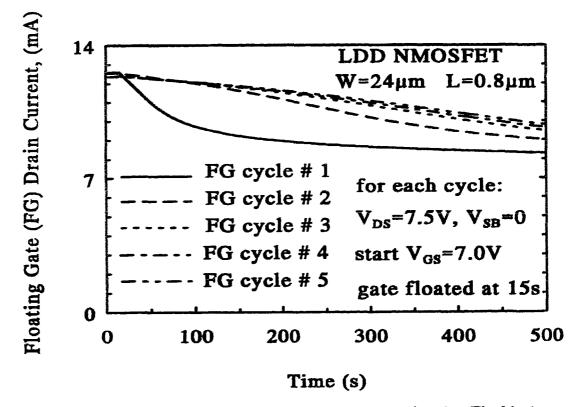

| Fig. 4.5.  | Evolution of floating gate drain current over several<br>The biasing configuration maximizes hot-electron go                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                    |

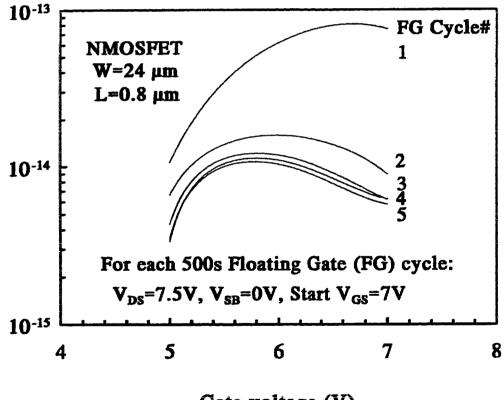

| Fig. 4.6.  | Gate currents extracted from the floating gate cycles<br>The shift in the peaks of the gate currents to lower go<br>is remarkable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 64                   |

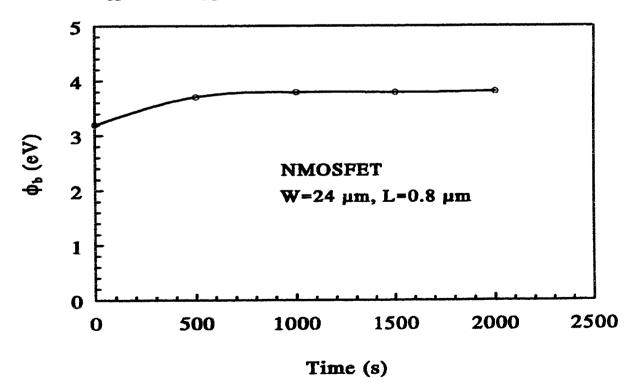

| Fig. 4.7.  | Evolution of the barrier height $\phi_b$ to gate current inj during the early mode degradation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ection               |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 65                   |

| Fig. 4.8.  | Reverse and forward saturation $I_{DS}$ vs. $V_{GS}$ characted MOSFET during the floating gate cycles shown in figure 1.5 to 2.5 to 2. |                      |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68                   |

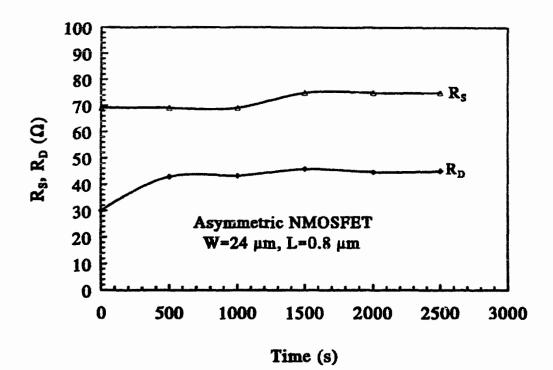

| Fig. 4.9.  | Evolution of $R_D$ and $R_S$ during the early mode degra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | dation.<br>69        |

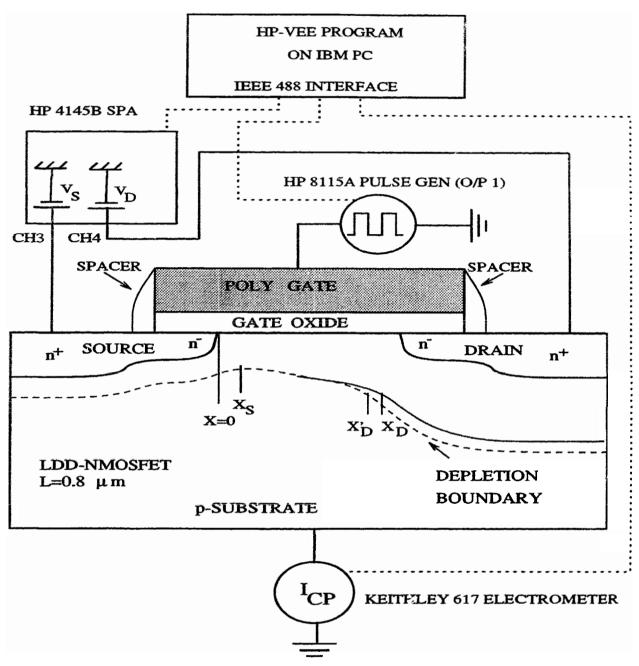

| Fig. 4.10. | Spatial profiling charge pumping set up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 07                   |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71                   |

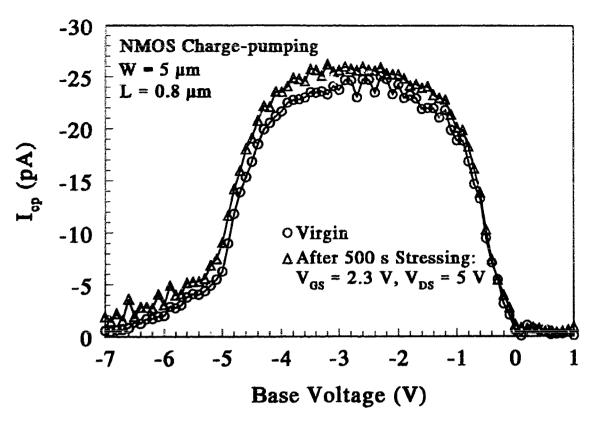

| Fig. 4.11. | Charge pumping currents with 1 MHz square wave p<br>5V amplitude before and after early mode degradation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 74                   |

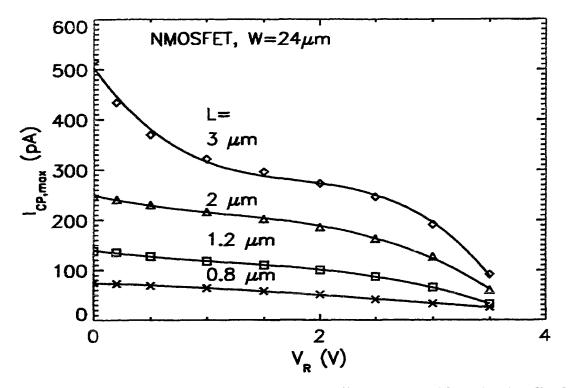

| Fig. 4.12. | Charge pumping current versus $V_R$ for different char lengths. Amplitude of square wave pulses applied to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |

|            | gate was 5 V, with $V_S = V_D = V_R$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 75                   |

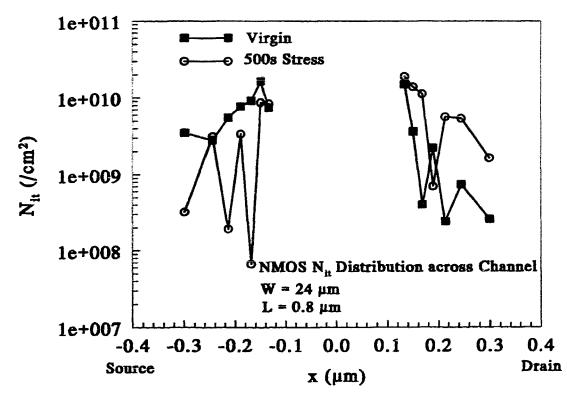

| Fig. 4.13. | N <sub>it</sub> distributions near source and drain extracted by profiling charge pumping.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | spatial              |

|            | I J G G F T F G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76                   |

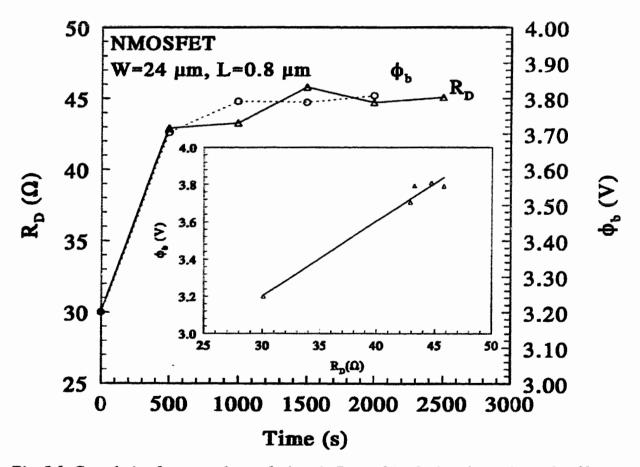

| Fig. 5.1.  | Correlation between the evolutions in $R_D$ and $\phi_b$ dur early mode of hot-carrier degradation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ing the              |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83                   |

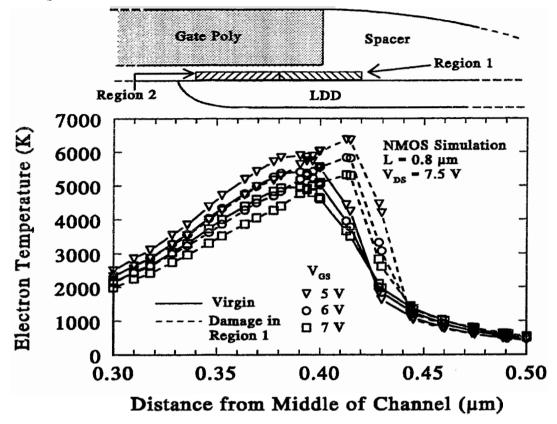

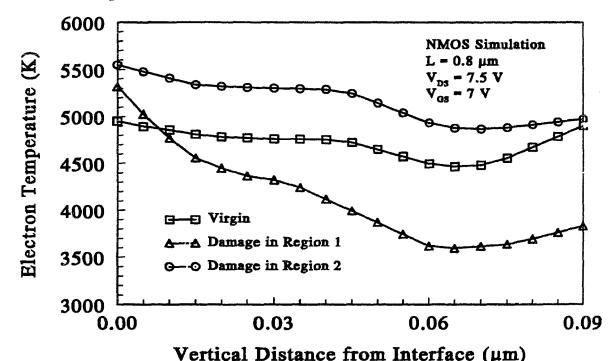

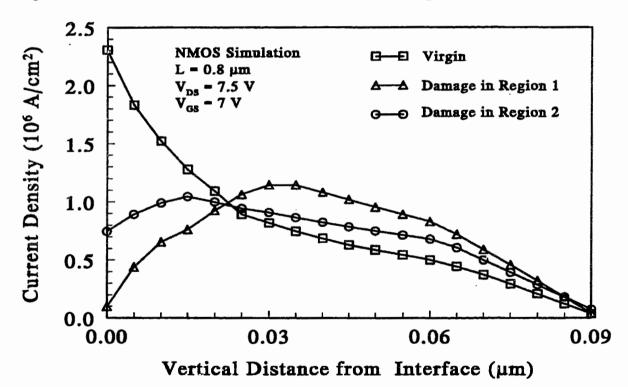

| Fig. 5.2.  | Lateral electron temperature profiles for virgin and a device (with damage in Region 1).                                                                                                                             | lamaged                       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

|            |                                                                                                                                                                                                                      | 85                            |

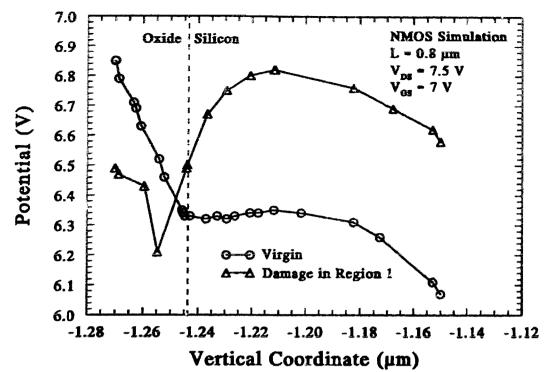

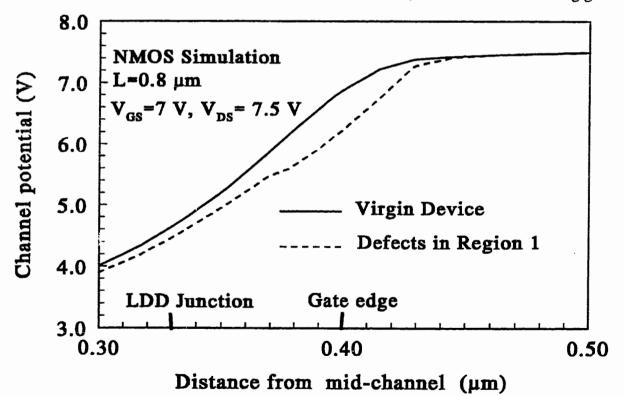

| Fig. 5.3.  | Simulation of the vertical potential profiles at the per<br>lateral electron temperature profiles (see fig. 5.2).                                                                                                    | ak of                         |

|            |                                                                                                                                                                                                                      | 86                            |

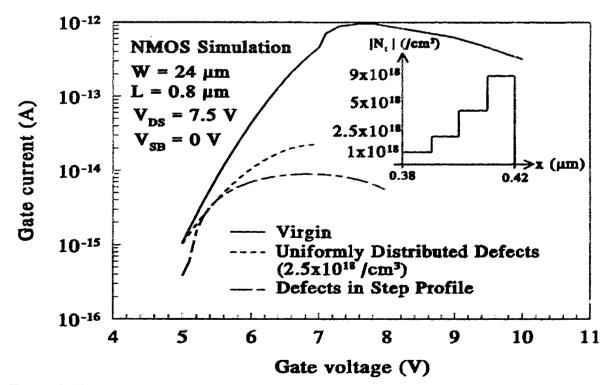

| Fig. 5.4.  | Gate currents simulated for the virgin device as well device with defects in Region 1 of fig. 5.2. Inset show profile of defects used.                                                                               | •                             |

|            |                                                                                                                                                                                                                      | 86                            |

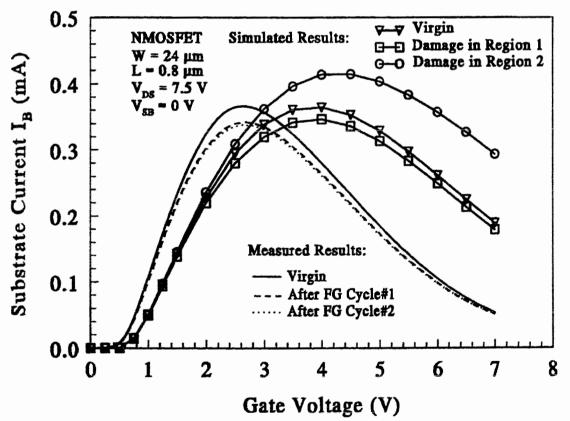

| Fig. 5.5.  | Decrease of measured $I_B$ with the FG cycles. The curchange much after the FG cycle #2. Simulated $I_B$ for damaged (both Regions 1 & 2 of fig. 5.2) devices sugprobable location of damage is Region 1 (gate edge) | virgin and<br>ggests that the |

|            | F                                                                                                                                                                                                                    | 88                            |

| Fig. 5.6.  | Measured linear current degradation vs. gate bias or 5 FG cycles matches better with the simulated values in Region 1.                                                                                               |                               |

|            |                                                                                                                                                                                                                      | 89                            |

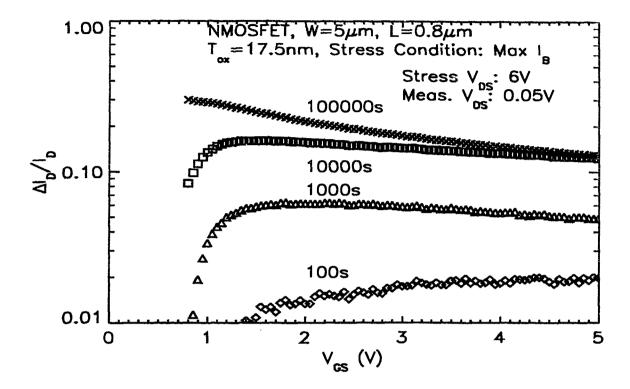

| Fig. 5.7.  | Linear current degradation versus measurement gate<br>various stress times. Measurement was done in the fo                                                                                                           |                               |

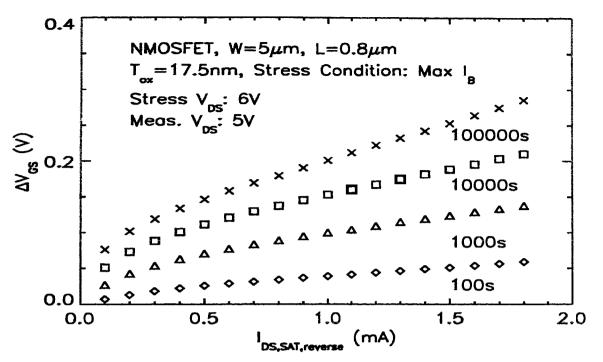

| Fig. 5.8.  | Measured voltage shift in the reverse $I_{D,sat}$ vs. $V_{GS}$ c $V_{DS}=5$ V over the 5 FG cycles matches better with the simulated values for damage in Region 1 (see fig. 5.2)                                    | he                            |

|            |                                                                                                                                                                                                                      | 91                            |

| Fig. 5.9.  | Measured voltage shift in the reverse $I_{D,sat}$ vs. $V_{GS}$ chot-carrier stress experiment.                                                                                                                       | eurve over                    |

|            |                                                                                                                                                                                                                      | 92                            |

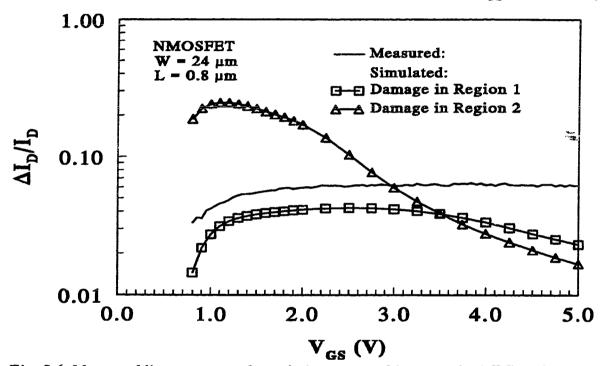

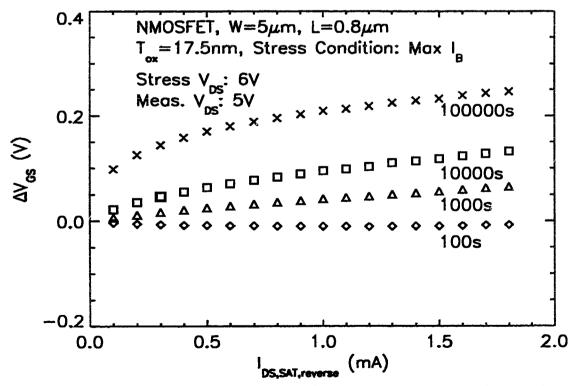

| Fig. 5.10. | Measured voltage shift in the forward $I_{D,sat}$ vs. $V_{GS}$ hot-carrier stress experiment.                                                                                                                        | curve over                    |

|            |                                                                                                                                                                                                                      | 92                            |

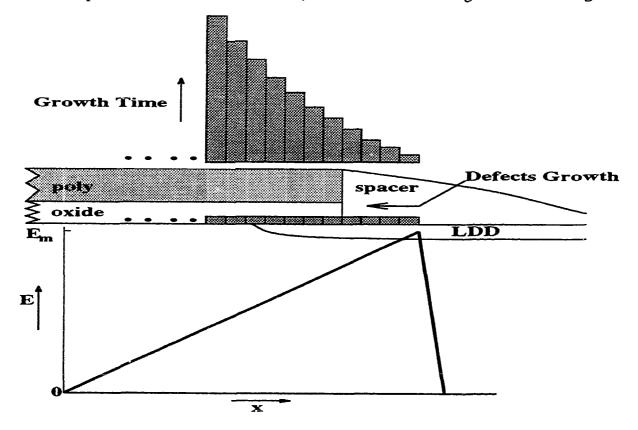

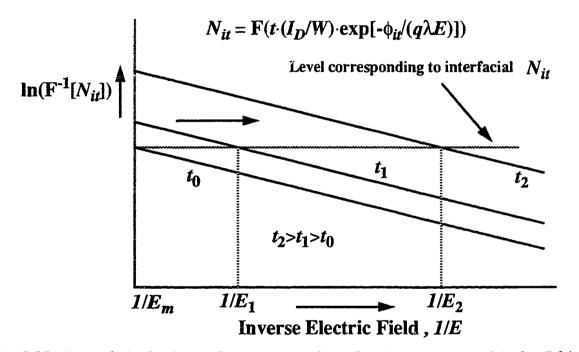

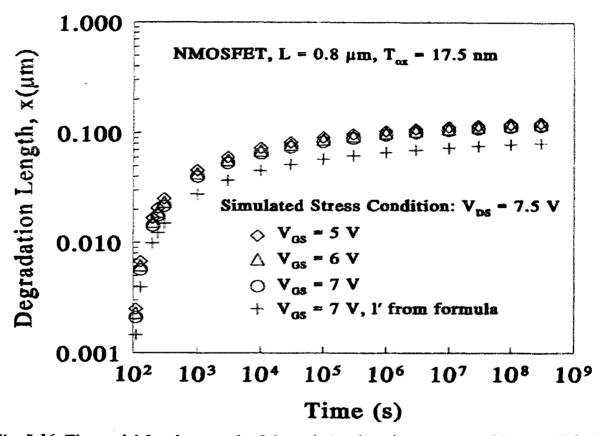

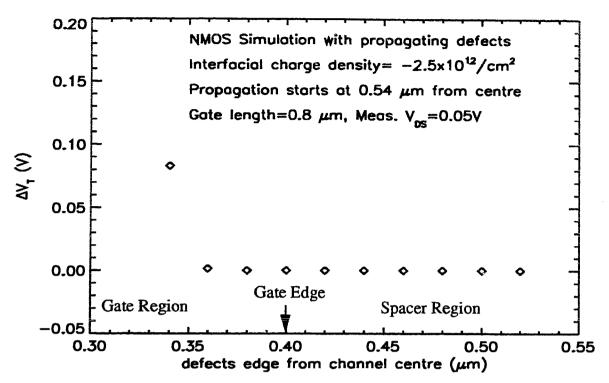

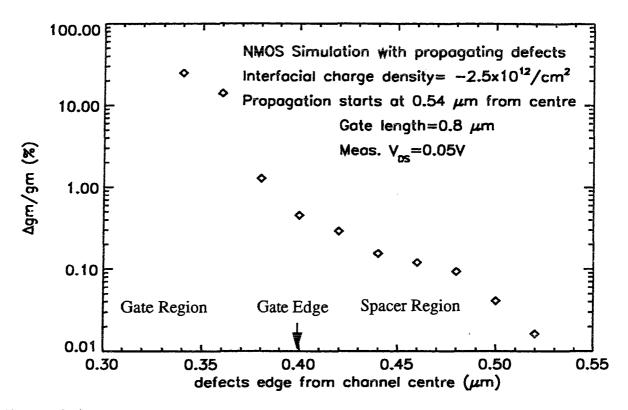

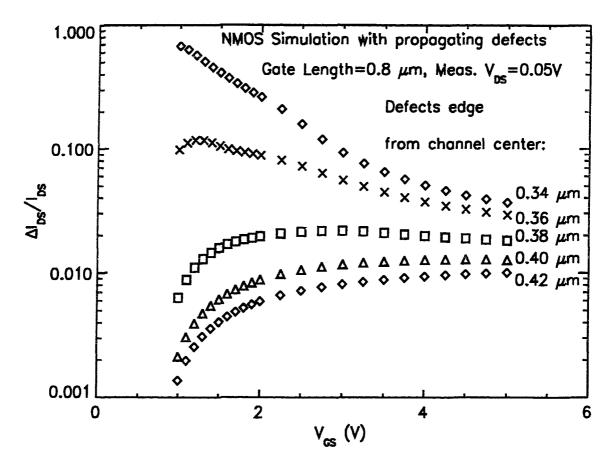

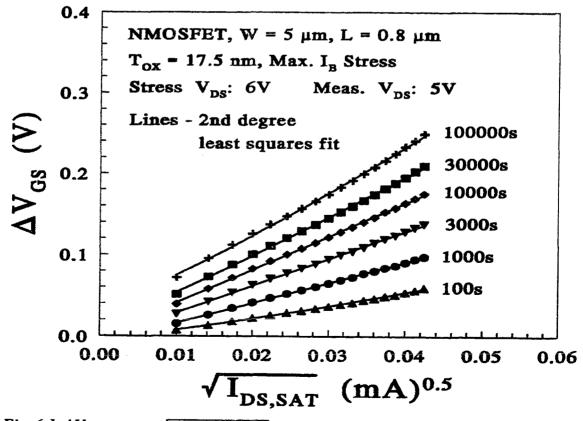

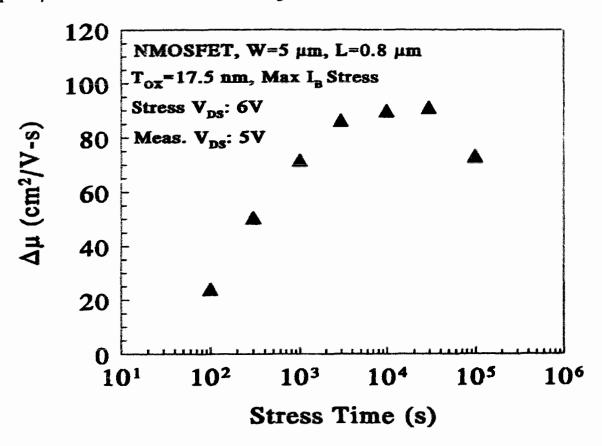

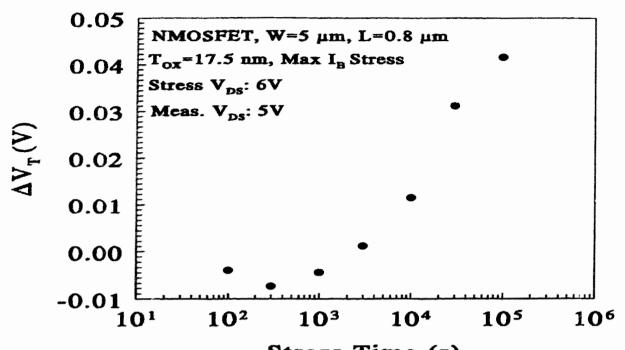

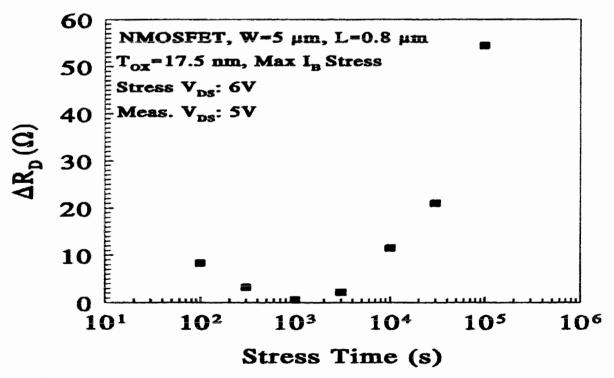

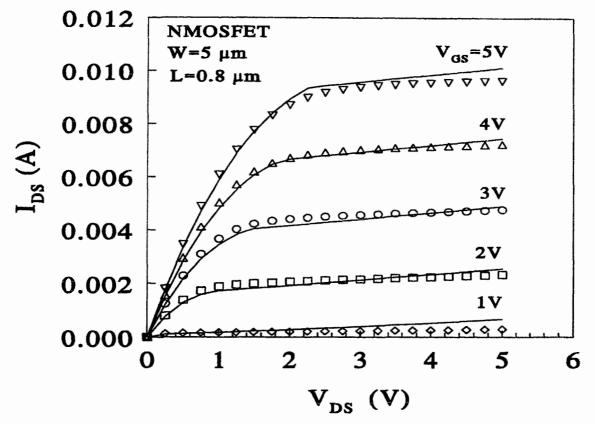

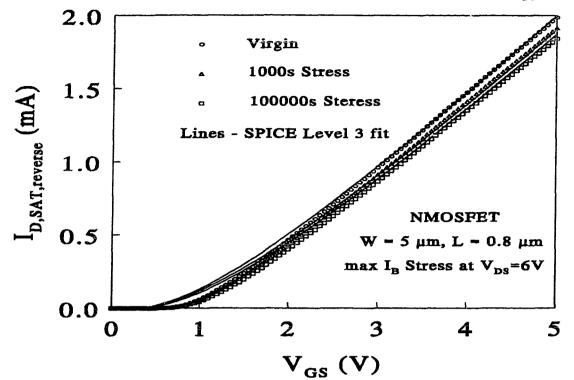

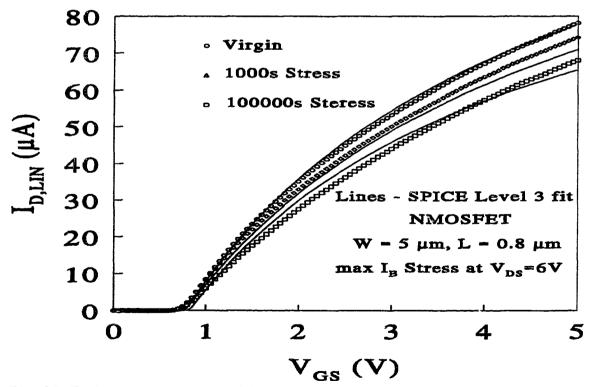

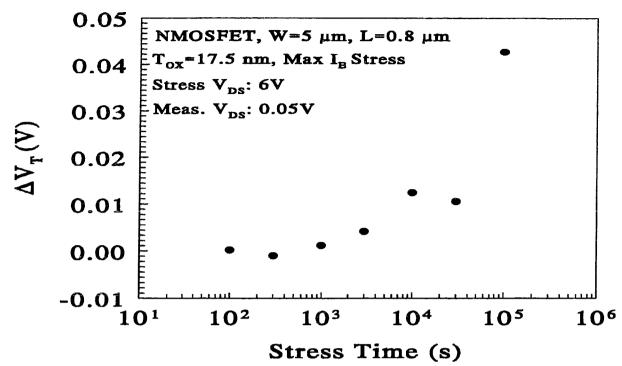

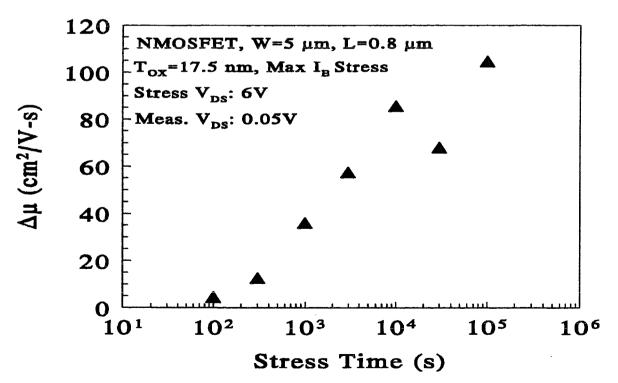

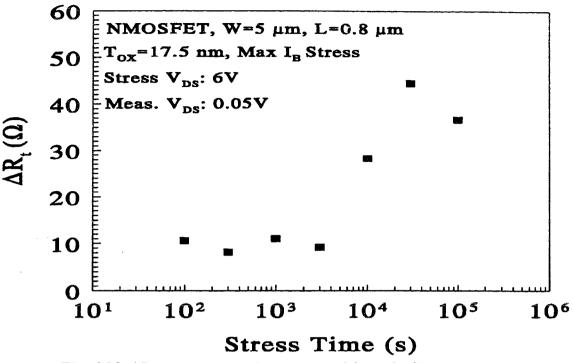

| Fig. 5.11. | The simulated channel potential profiles near drain,<br>virgin device, and the device with defects in Region 2                                                                                                       | -                             |