## **DESIGN AND IMPLEMENTATION**

### OF

# AN EMBEDDED MULTIPROCESSOR SYSTEM, SAM-II

by Rodoslav Dervishev

THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE in the School of Computing Science

> © Rodoslav S. Dervishev 1995 SIMON FRASER UNIVERSITY October 1995

All rights reserved. This work may not be reproduced in whole or in part, by photocopy or other means, without permission of the author.

# **|** + ||

National Library of Canada

Acquisitions and Bibliographic Services Branch

395 Wellington Street Ottawa, Ontario K1A 0N4 Biblicthèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A 0N4

Your file Votre rélérence

Our file Notre référence

The author granted has an irrevocable non-exclusive licence allowing the National Library of reproduce, Canada to loan. distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette disposition thèse à la des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission.

na

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-16858-1

# Approval

| Name:            | Rodoslav S. Dervishev                                                     |

|------------------|---------------------------------------------------------------------------|

| Degree:          | Master of Science                                                         |

| Title of Thesis: | Design and Implementation of An Embedded<br>Multiprocessor System, SAM-II |

**Examining Committee:**

Dr. F. David Fracchia Chair

Dr. Rick Hobson Senior Supervisor

Dr. Slavomir Pilarski Supervisor

Dr. Glenn Chapman Examiner

Date Approved:

October 11, 1995

ii

#### SIMON FRASER UNIVERSITY

## PARTIAL COPYRIGHT LICENSE

I hereby grant to Simon Fraser University the right to lend my thesis, project or extended essay (the title of which is shown below) to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its users. I further agree that permission for multiple copying of this work for scholarly purposes may be granted by me or the Dean of Graduate Studies. It is understood that copying or publication of this work for financial gain shall not be allowed without my written permission.

Title of Thesis/Project/Extended Essay

# Design and Implementation of An Embedded

Multiprocessor System, SAM-II.

Author:

(signature)

Rodoslav S. Dervishev

(name)

October 20, 1995

(date)

To my parents

### Acknowledgments

I thank Dr. Rick Hobson for his supportive supervision and help. Without his ideas and comments, this thesis would not have been possible. I also thank Rick for supporting me financially for the duration of the project, allowing me to concentrate on the actual research.

I also thank Dr. Slawek Pilarski and Dr. Gleun Chapman for their careful reading of my thesis and their comments that helped improve it.

Thanks go to my friends and affiliates from the VLSI Lab Dr. Slawek Pilarski, P.S. Wong, Don Smith, George Vodarek and Alicja Pierzynska for making the lab such an exciting place to be at and to the people from Hardware Support Group Peter Corps, Frank Manuel and Steve Nix for helping with equipment in times of need.

Finally, I would like to thank Simon Fraser University and the School of Computing Science for providing financial support for four semesters and thank all faculty members, administrative personnel and students in the department, who made my time at SFU such a rewarding and unforgettable experience.

v

## Abstract

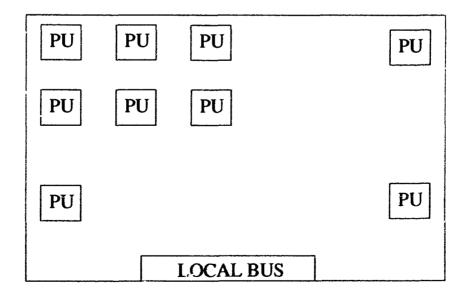

The Structured Architecture Machine (SAM-II) board-level hardware and system software design and implementation concepts are discussed. SAM-II is An Embedded Multiprocessor Vector-Oriented Computer System based on a custom 32 bit RISC chip set designed at the VLSI and Computer Design Laboratory and intended for low-cost array processing and computationally intensive applications.

The prototype is designed to accommodate up to five processing units connected to a DS80C320 microcontroller based mother-board bus. FPGA based logic is designed to implement bus control and processing units control interface functions and also to realize selection, deselection and broadcasting interfacing capabilities, allowing efficient access to the multiprocessor environment within a single DS80C320 machine cycle. The use of the SJCP custom data/control interface incorporating interfacing and boundary-scan testing capabilities is also discussed in the context of system hardware concepts, testing, and processing unit resource access.

The custom use of The Small Computer System Interface (SCSI) Protocol for efficient program, data, and control information transfer is discussed in detail. Menu-driven front-end software provides multiprocessor system configuration, system management, and program debugging capabilities. It also allows flexible real-time access to and use of the system resources. Low-level system resource management is realized by the mother-board monitor program built around a SCSI interface driver communicating with the host in a way similar to the concepts of the remote procedure call.

Discussion about the next generation system and alternative use and applications of the system is also included.

# **Table of Contents**

| Approval                                                                                                                                                                                   | . <b> ii</b> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Dedication                                                                                                                                                                                 | <i>.</i> iii |

| Acknowledgments                                                                                                                                                                            | iv           |

| Abstract                                                                                                                                                                                   |              |

| Table of Contents                                                                                                                                                                          |              |

| List of Figures                                                                                                                                                                            |              |

| List of Tables                                                                                                                                                                             |              |

| Chapter 1: Introduction                                                                                                                                                                    |              |

| 1.1. Embedded Systems                                                                                                                                                                      |              |

| 1.1.1. Architectural Concepts         1.1.2. Embedded Systems Interfacing         1.1.3. Embedded Systems Debugging and Trouble-Shooting         1.1.4. SAM-II Embedded System             | 1<br>2<br>3  |

| 1.2. Test Methods                                                                                                                                                                          | 6            |

| 1.2.1. General Concepts1.2.2. Boundary-Scan Testing1.2.3. Scan Paths Implementations                                                                                                       | 8            |

| 1.3. Debugging Tools and Concepts                                                                                                                                                          | 10           |

| <ul> <li>1.3.1. General Features</li> <li>1.3.2. Debugger System Interfacing</li> <li>1.3.3. Simulators vs. Target System Debugging</li> <li>1.3.4. Debugging Parallel Programs</li> </ul> | 12           |

| 1.4. Objectives                                                                                                                                                                            |              |

| Chapter 2: Hardware Design                                                                                                                                                                 | 17           |

| 2.1. SAM-II Architecture                                                                                                                                                                   |              |

| 3.1.2.2.2. SAM II SCSI-Bus Driver Architecture          | . 52 |

|---------------------------------------------------------|------|

| 3.2. System Software                                    | . 55 |

| 3.2.1. Host Control Interface                           |      |

| 3.2.2. Microcontroller Monitor Program                  |      |

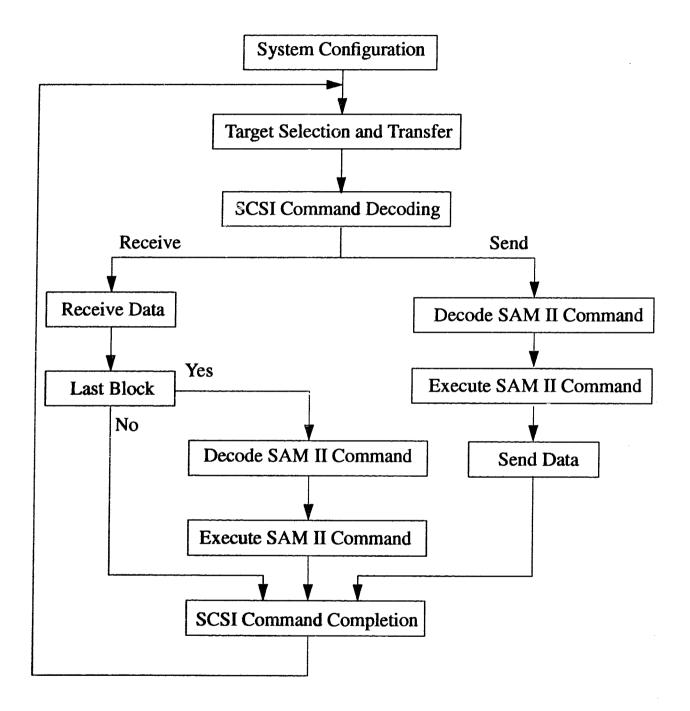

| 3.2.2.1. Architecture                                   | . 59 |

| 3.2.2.2. An Example of SAM II Command Execution         | . 62 |

| 3.2.3. Software Development Tools and Program Debugging | . 64 |

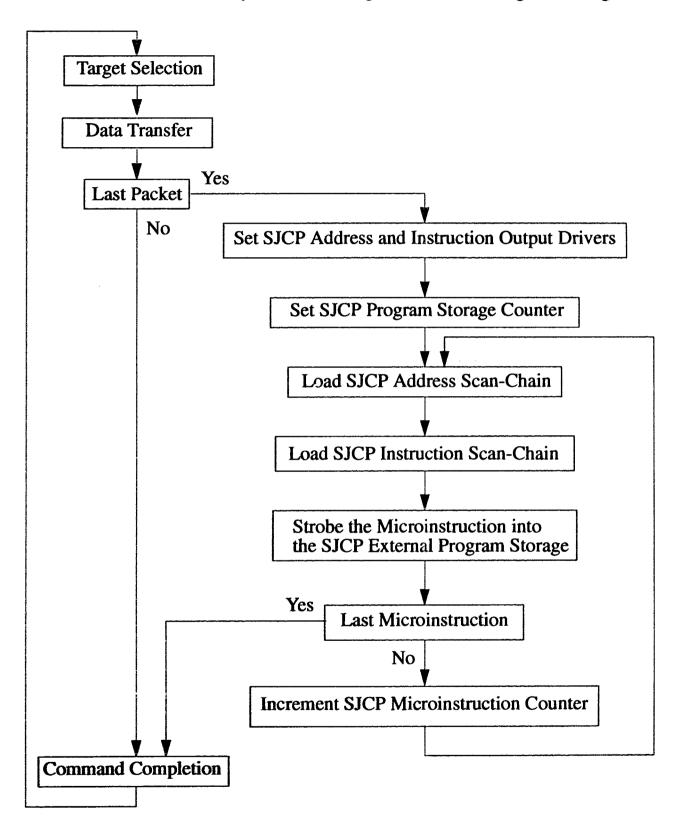

| 3.2.3.1. SAM II Program Management                      |      |

| 3.2.3.1.1. SAM II Executable Loading                    |      |

| 3.2.3.1.2. SAM-II Executable Verification               |      |

| 3.2.3.1.3. SAM II Program Initialization                |      |

| 3.2.3.1.4. SAM II Program Termination                   |      |

| 3.2.3.2. SAM II Debugger Concepts                       |      |

| 3.2.3.2.1. Step-by-Step Execution                       |      |

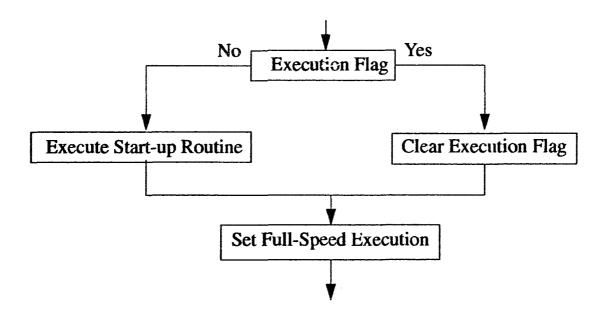

| 3.2.3.2.2. Full-Speed Execution                         |      |

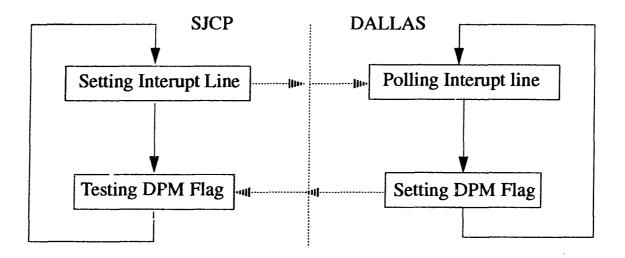

| 3.2.3.2.3. Dual-Port Memory Monitoring                  |      |

| 3.2.3.2.4. Breakpointing                                |      |

| 3.2.3.2.5. Instruction Disassembling                    |      |

| 3.2.3.2.6. Parallel Execution and Debugging             |      |

| 3.3. Test Software                                      | . 74 |

| 3.3.1. Testing The Microcontroller                      | .74  |

| 3.3.1.1. Testing the Serial Interface                   | . 75 |

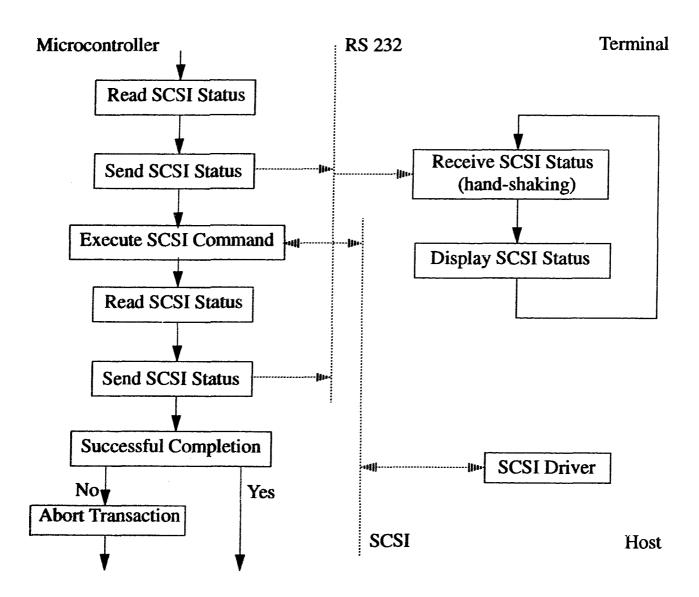

| 3.3.1.2. Testing the SCSI Interface                     | .75  |

| 3.3.1.3. Testing Microcontroller - SJ board Interface   | . 77 |

| 3.3.2. Testing SJ boards                                |      |

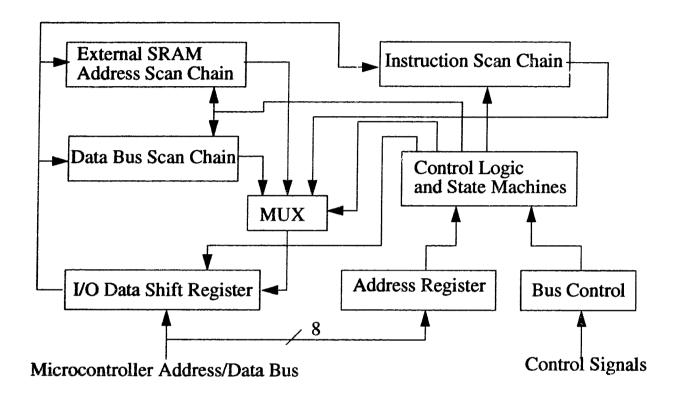

| 3.3.2.1. SAM-II Boundary Scan Testing Concept           | . 78 |

| 3.3.2.2. Testing the Dual-Port Memory                   | . 79 |

| 3.3.2.3. Testing the Event Interface                    | . 80 |

| 3.3.2.4. Testing the SJCP External Program SRAM         | . 80 |

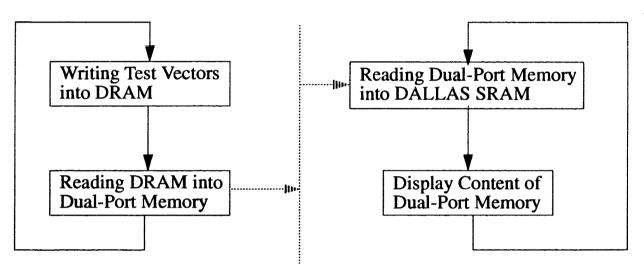

| 3.3.2.5. Testing External DRAM                          | . 81 |

| 3.4. Summary                                            | . 82 |

| Chapter 4: General Discussion                           | . 83 |

| 4.1 Architectural Issues                                |      |

| 4.1.1. Next Generation                                  | . 83 |

| 4.1.2. System Interfacing                               |      |

| 4.2. Software Issues                                    |      |

| 4.2.1. Alternative System Applications                  |      |

| <b>4.2.1.</b> Alternauve System Applications            | . 05 |

| 4.2.2 Program and Data Management                        | . 86 |

|----------------------------------------------------------|------|

| 4.2.3. Parallel Debugging                                |      |

| 4.2.3.1. Debugger-Operating System Relationship          |      |

| 4.2.3.2. State- and Event-Driven Debuggers               |      |

| 4.2.3.3. SAM-II Debugging Concepts                       |      |

| 4.3. Performance Issues                                  | . 91 |

| 4.3.1. Technology                                        |      |

| 4.3.2. Component Integration                             |      |

| 4.3.3. System interface                                  |      |

| <b>4.3.</b> Conclusion                                   |      |

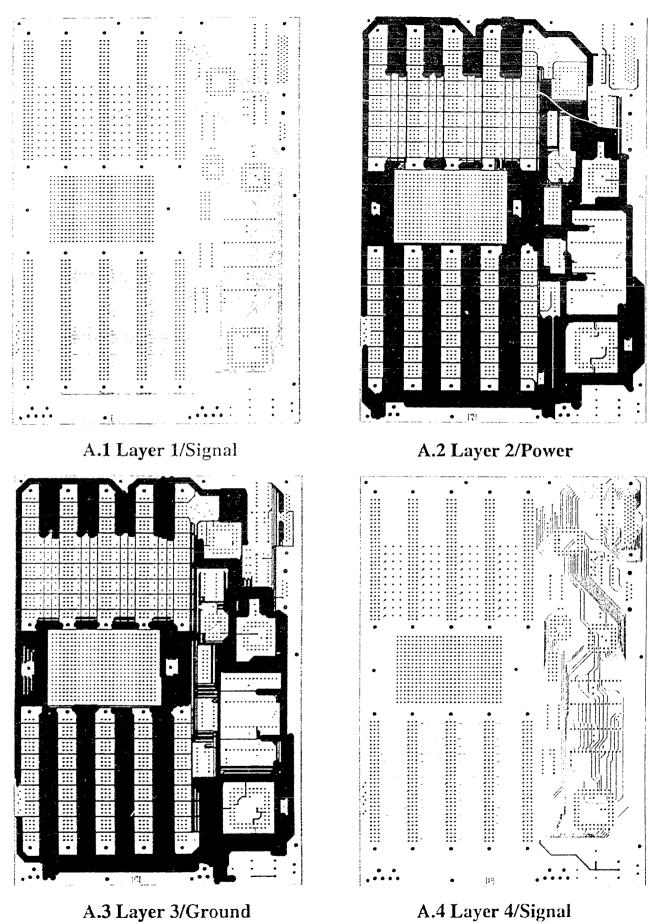

| Appendix A: Microcontroller Printed Circuit Board        | . 95 |

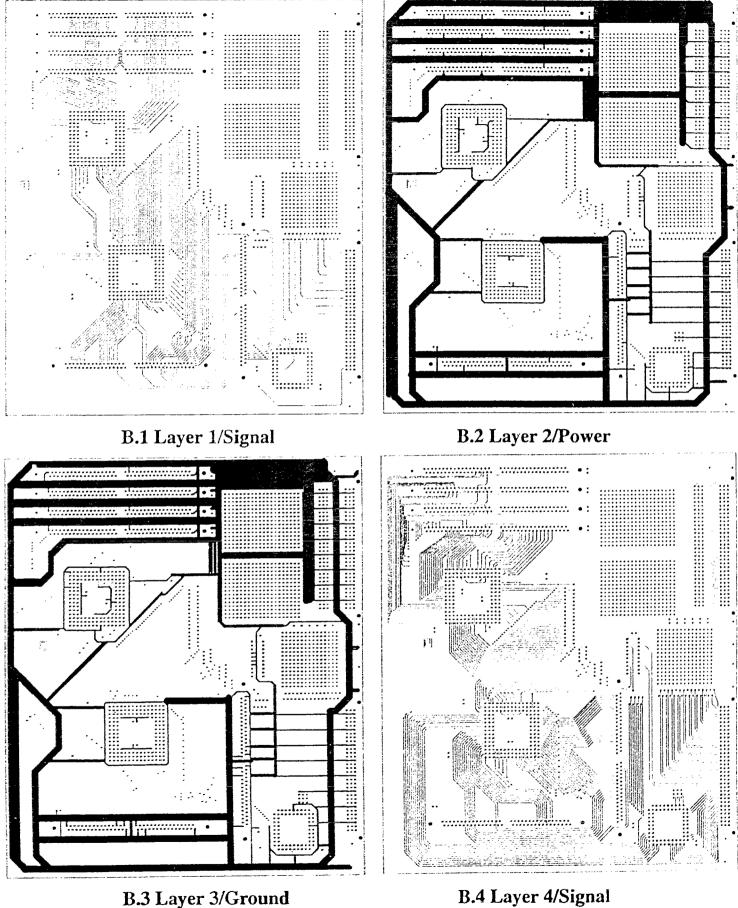

| Appendix B: SJ Processing Unit Printed Circuit Board     | . 97 |

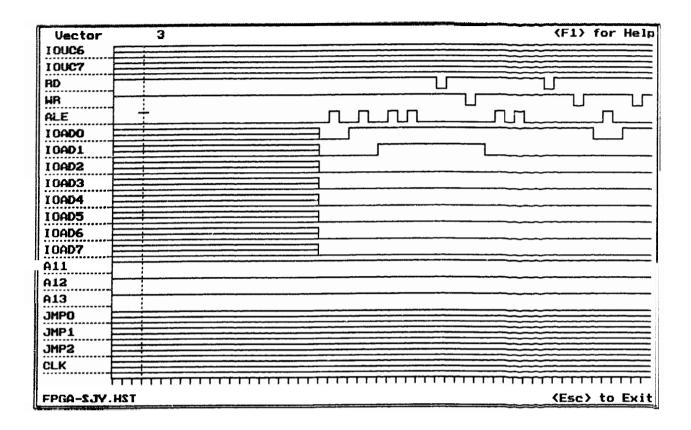

| Appendix C: Microcontroller FPGA Design Files            | . 99 |

| Appendix C.1.1: PDS Design File/Version I                | 100  |

| Appendix C.1.2: PDS Design File/Version I: Simulations   | 104  |

| Appendix C.2.1: PDS Design File/Version II               | 106  |

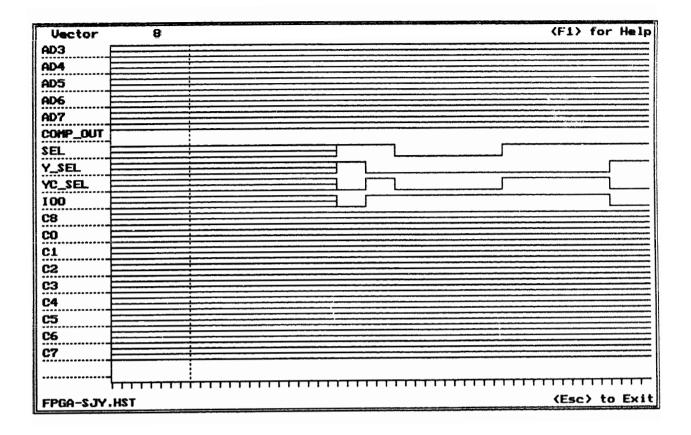

| Appendix C.2.2: PDS Design File/Version II: Simulations  |      |

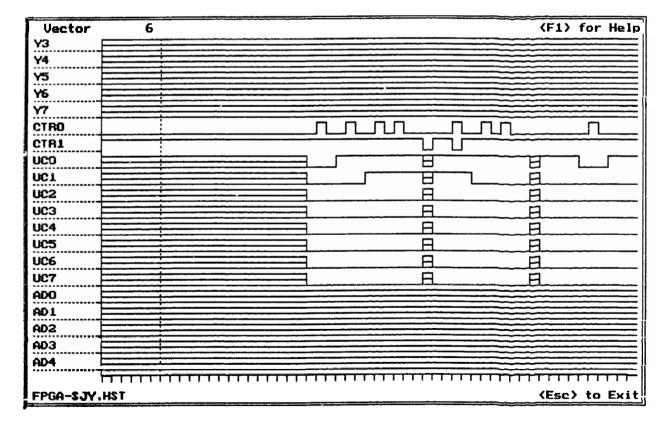

| Appendix D: SAM Junior Processing Unit FPGA Design Files | 112  |

| Appendix D.1.1: PDS Design File/Version I                | 113  |

| Appendix D.1.2: PDS Design File/Version I: Simulations   |      |

| Appendix D.2.1: PDS Design File/Version II               |      |

| Appendix D.2.2: PDS Design File/Version II: Simulations  |      |

| Appendix E: Memory Map of SJCP special function memory   |      |

| Glossary                                                 | 126  |

| Bibliography                                             |      |

-

# **List of Figures**

| Figure 1.1: Embedded System General Architecture                  | 1  |

|-------------------------------------------------------------------|----|

| Figure 1.2: Host - Embedded System Configuration                  | 2  |

| Figure 1.3: Embedded System Trouble-Shooting Configuration        | 5  |

| Figure 1.4: SAM-II Embedded System Architecture                   | 6  |

| Figure 1.5: Single-Chip Boundary-Scan Architecture                | 8  |

| Figure 2.1: SAM-II Architecture                                   | 18 |

| Figure 2.2: SAM-II Prototype                                      | 19 |

| Figure 2.3: Microcontroller Block-Diagram                         | 21 |

| Figure 2.4: Microcontroller Board Layout                          | 26 |

| Figure 2.5: SJ-board Block Diagram                                | 29 |

| Figure 2.6: SJ-board Layout                                       | 31 |

| Figure 2.7: Physical Datapath                                     | 33 |

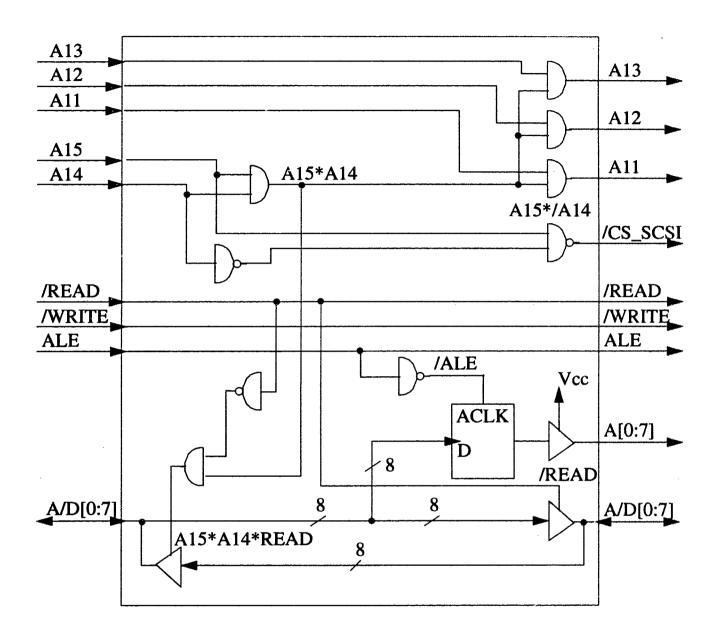

| Figure 2.8. Microcontroller FPGA-M Version-1 Logic Design         | 35 |

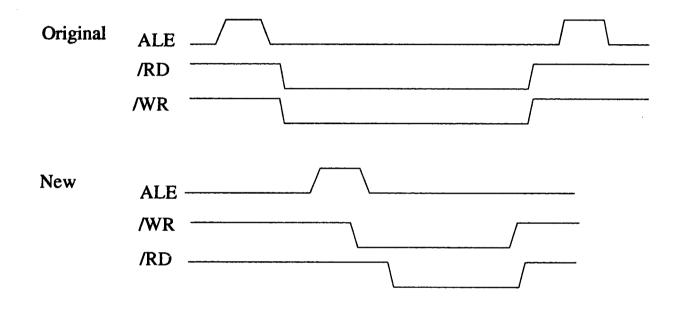

| Figure 2.9: Bus Control Signals Timing                            | 36 |

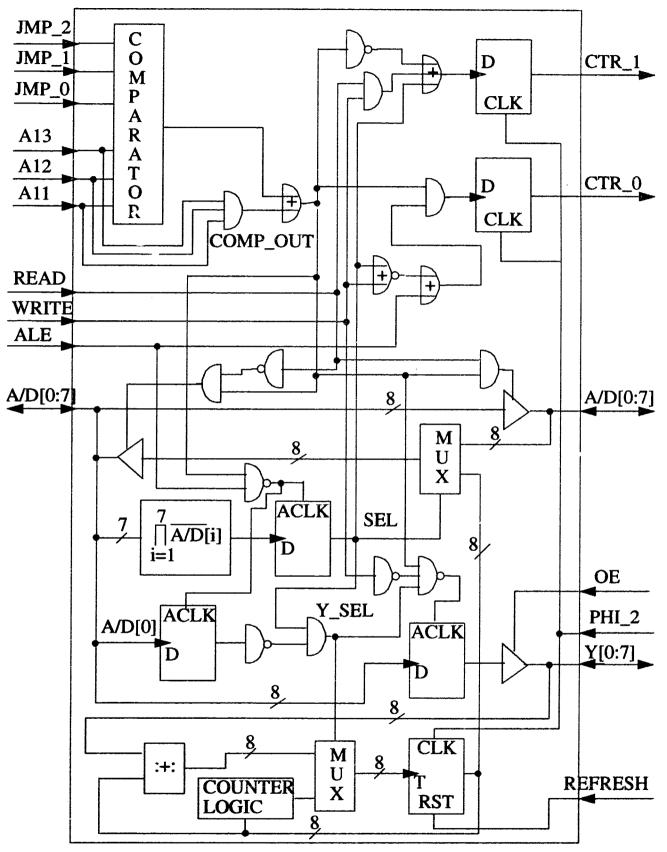

| Figure 2.10: FPGA-SJ Logic Diagram                                | 39 |

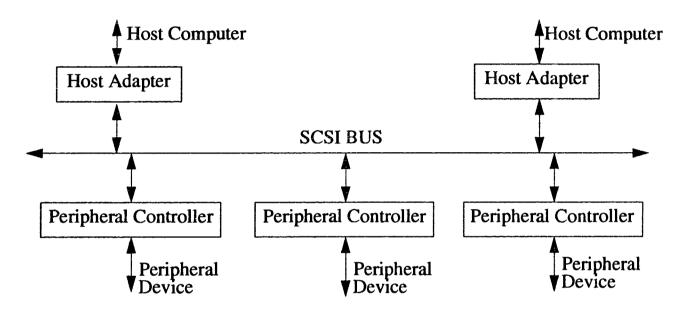

| Figure 3.1: SCSI Bus Configuration                                | 43 |

| Figure 3.2. SCSI transaction phase sequence                       | 44 |

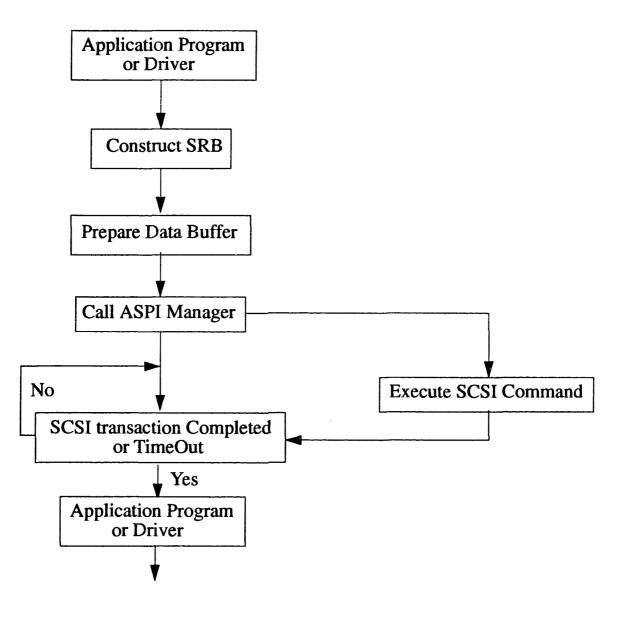

| Figure 3.3: Calling ASPI Manager                                  | 49 |

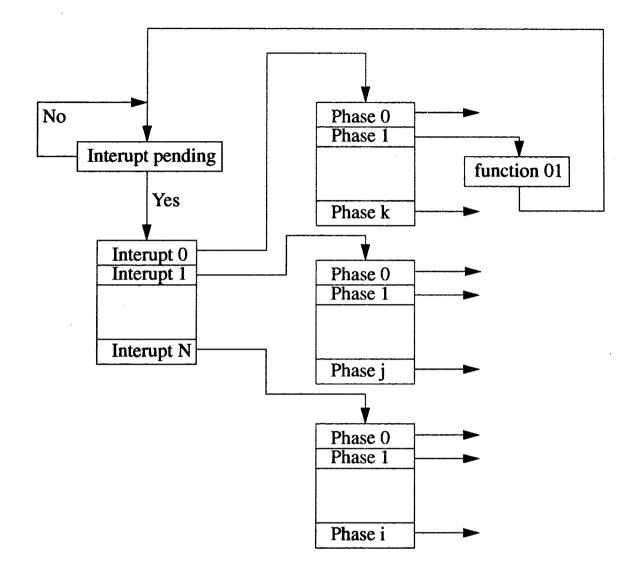

| Figure 3.4: Interupt Driven SCSI Bus Driver                       | 51 |

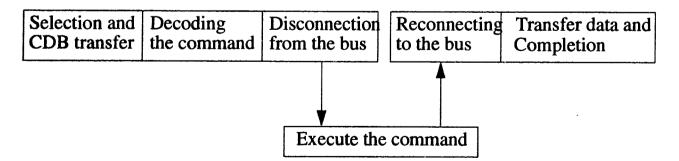

| Figure 3.5: SCSI Command Execution Through Disconnection          | 52 |

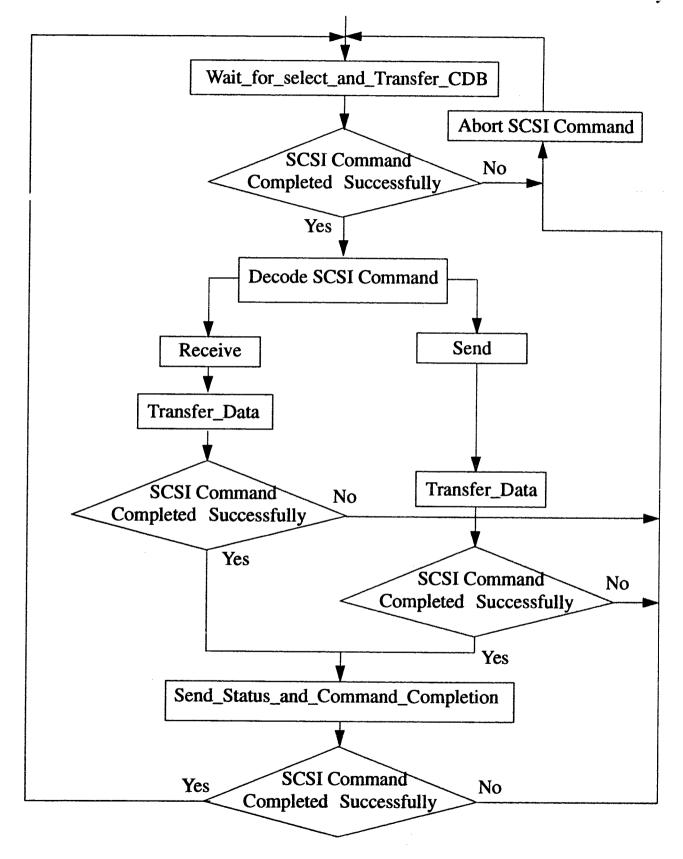

| Figure 3.6: SAM II SCSI Driver Architecture                       | 53 |

| Figure 3.7: Main Command Execution Loop                           | 55 |

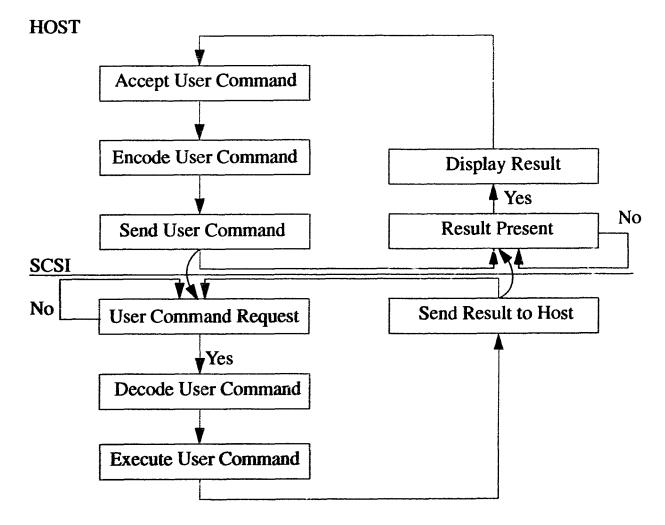

| Figure 3.8: Host Control Interface Main Loop                      | 56 |

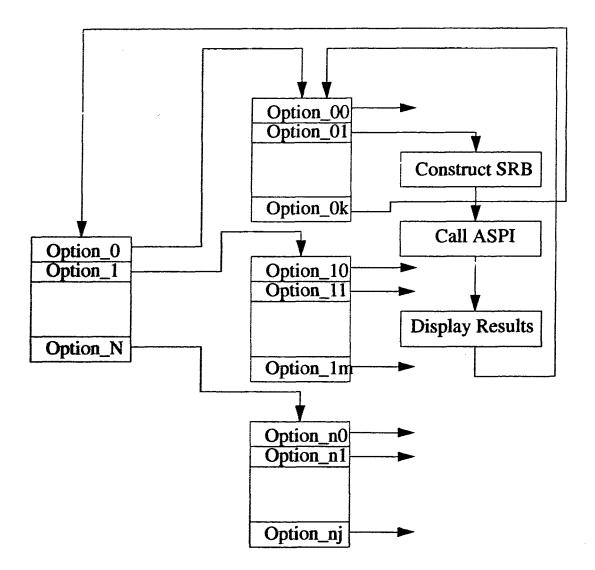

| Figure 3.9: Microcontroller Monitor Architecture                  | 60 |

| Figure 3.10: Loading Executable Image into the SJCP External SRAM | 63 |

| Figure 3.11: SJCP Program Storage Interface                       | 66 |

x

| Figure 3.12: Program Initialization Routine                 | 67 |

|-------------------------------------------------------------|----|

| Figure 3.13: SJCP Program Termination Routine               | 68 |

| Figure 3.14: Step Execution Command Algorithm               | 70 |

| Figure 3.15: Setting Full-Speed Execution Mode              | 71 |

| Figure 3.16: SCSI Bus Single Phase Test Algorithm           | 76 |

| Figure 3.17: SJCP Boundary Scan-Chain Architecture          | 78 |

| Figure 3.18: Testing the Event Interface       8            | 80 |

| Figure 3.19: DRAM Testing Algorithm                         | 81 |

| Figure 4.1: SAM-III Architecture                            | 83 |

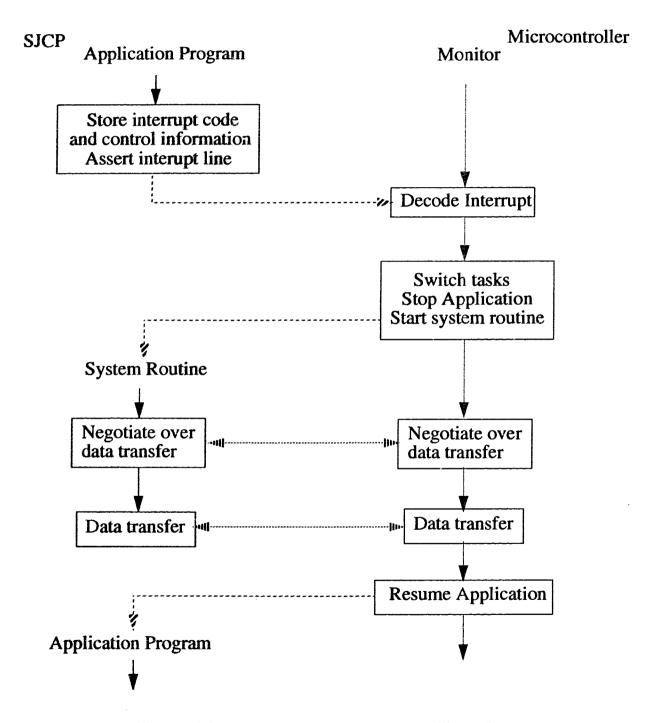

| Figure 4.2: Task-Switching and Data Transfer                | 87 |

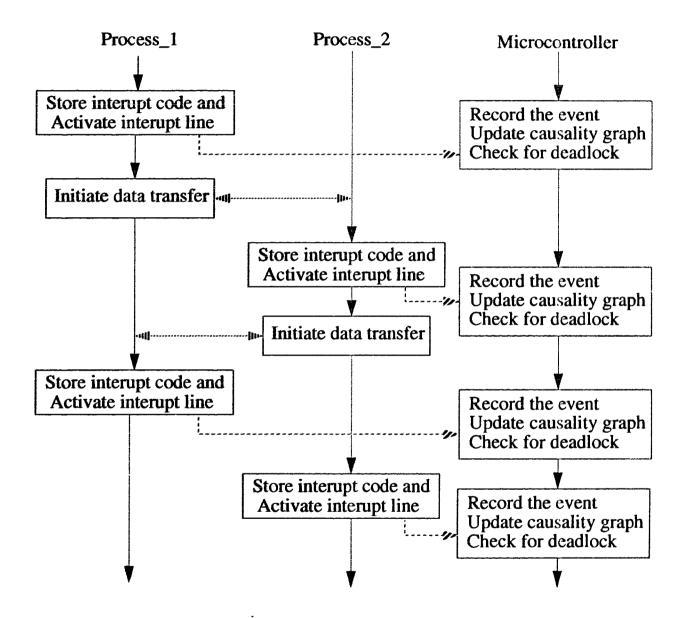

| Figure 4.3: Deadlock and Race Conditions Detector Algorithm | 90 |

# **List of Tables**

| Table 1: Microcontroller Address Decoding Scheme | 22 |

|--------------------------------------------------|----|

| Table 2: SJ board Identification - Version 1     | 23 |

| Table 3: SJ board identification - Version 2     | 24 |

| Table 4: System Clocks Configuration             | 25 |

| Table 5: System Configuration Jumpers            | 27 |

| Table 6: Control Signals Decoding                | 30 |

| Table 7: SAM II Bus Signals                      | 37 |

| Table 8: CDB format for SEND                     | 45 |

| Table 9: SCSI I/O Request SRB                    | 47 |

| Table 10: ASPI Command Codes                     | 48 |

| Table 11: Load Executable CDB Format             | 57 |

| Table 12: Option Codes Description               | 58 |

|                                                  |    |

## **Chapter 1: Introduction**

#### 1.1. Embedded Systems

#### **1.1.1. Architectural Concepts**

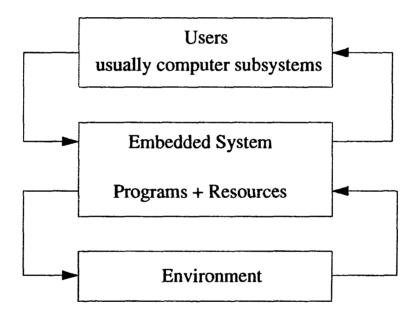

Embedded Systems (Figure 1.1) represent a subclass of Computer Systems with well-defined features [16, 17, 18].

- Fixed Resources - The system resources, hardware and firmware, are fixed and predefined. They do not increase or decrease during system operation. The way the embedded system interacts with the surrounding environment is predetermined.

#### Figure 1.1: Embedded System General Architecture

- Programs - The programs and the coded algorithms do not change and remain the same through the time of operation. In some cases though, part of the code could be downloaded dynamically. For example in multiprocessor configurations, where some of the processors are used as specialized coprocessor units, different code could be loaded dynamically depending on the particular request to the embedded system. In any case though, the code related to the global system resource management and interfacing is fixed and does not change.

- User - The users, which in general are subsystems of more complex

equipment are known and predefined along with the communication protocols. The operator, if any, is getting access to the resources of the embedded system through a directly accessible terminal or an interface unit.

- Environment - The environment where the embedded system performs some control or data processing functions is predefined and finite. This is important to guarantee stable system behavior.

- Data - The data going through the embedded system is the only thing that changes during operation time.

These are the characteristics of a typical embedded system. Of course each application would require features which would make the system unique but in one form or another the general characteristics will be present.

If we have a look at a general purpose desktop computer, every subsystem except the main CPU motherboard computational system represents an embedded system with respect to the user. The hard disk controller for example is a typical representative. The environment, the disk modules, is finite and predictable, the resources are fixed, the firmware is unchangeable, performing predefined disk control functions and servicing the host communication protocol.

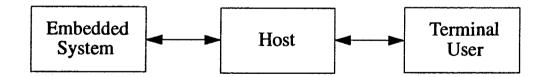

#### 1.1.2. Embedded Systems Interfacing

A general characteristic of an embedded system is that the user does not have direct access to its resources. The interface is realized through the host standard or custom built interfaces, Figure 1.2.

#### Figure 1.2: Host - Embedded System Configuration

Depending on the timing requirements and architectural concepts the embedded system could be connected to the host through standard external interfaces like RS 232, parallel ports or the Small Computer System Interface (SCSI), or it could be plugged directly on the main CPU local bus. In case an external interface is used, the data transfer complies to the corresponding interface communication protocol. In some cases though it might be necessary to build a higher-level communication protocol on the top of the standard interface protocol suitable for the particular application.

When an embedded system is attached to a host bus, it could be directly memory mapped using shared memory to communicate with the host, or some more complex protocol could be implemented. In any case shared memory is used to communicate and transfer control information and data in both directions.

In general, we could have several levels of interfacing. Let's consider the case of a multiprocessor embedded system where one of the processors is dedicated to serve the host interface and the rest of the processors are engaged in data processing activities. In this scenario, the first interface level is between the host computer and the embedded system interface processor and the second interface level is between the embedded system interface processor and the data processing processors. The ultimate goal here is to be able to transfer data between the host and the data processing processors. Sometimes a more complex interfacing concept is applied, particularly when the number of processors in the embedded system increases.

Sometimes one needs to access the embedded system directly, particularly during debugging. This is done usually by building local interfaces allowing direct access to the embedded system resources. An interesting concept has been realized in the Power PC 603 microprocessor [43] where dedicated pins in the microprocessor package allow an external processor to get access to 603's resources and monitor the system performance.

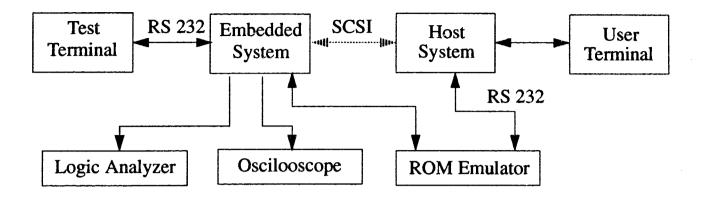

#### **1.1.3. Embedded Systems Debugging and Trouble-Shooting**

Obviously, with respect to the host computer an embedded system represents a a part of its computational resources regardless of the way it is interfaced. On power-up the system resources are tested including all the embedded systems. The embedded systems initialization procedures should perform local system test and respond in a predefined way providing information about the extent and accessibility and functionality of its local resources. The local testing routines might involve combinations of different board-level testing techniques and Built In Self Tests (BIST) at the chip level. The purpose of a power-up self-test is to determine what part(s) of a presumably working subsystem are available.

A more interesting question is how to test and debug an embedded system in

the process of integrating and building the prototype. The interesting part is that the embedded system, not accessible directly, should be tested at board-level through its interfaces which are also under test and development.

Usually during trouble-shooting the designers are using a combination of different debugging tools and mechanisms [45] in order to get the full picture of the problem. One of the least expensive mechanism is ROM monitoring. The ROM monitor allows to set break-points, control program execution, and access memory and registers. A very popular tool is also the ROM emulator. It provides a low-level debug control and is very flexible to use. We used the PROMICE ROM emulator to emulate the microcontroller program storage during debugging.

Probably one of the most favorite tools is the In-Circuit Emulators (ICEs). The ICE provides full execution control and sometimes bus monitoring and performance analysis functions. The problem with the ICEs is that they could be pretty expensive and difficult to build particularly for chips with high complexity and high clock rates.

A fairly new approach which is getting more and more popular is to incorporate an on-chip debugging hardware which could be a Background Debugging Mode (BDM) or scan path implementation allowing program execution control and registers and memory access. The IBM's 403GA Power PC JTAG scan path [45] provides a serial link to the on-chip debugging hardware allowing to set breakpoints, control execution and read and modify registers, memory and cache. A very interesting concept has been realized in the Advanced Micro Devices' 29040 microprocessor. The 29040's on-chip debugger uses scan paths to access registers and memory, and the hardware has been designed in such a way so that two 29040s could work in tandem in a master-slave relationship. The master CPU is executing the code normally. The trace CPU mirrors the master CPU's access addresses on its address bus and they can be picked up by an external hardware and put into a trace buffer.

Of course, we have to mention the traditional tools used during debugging: probes, oscilloscopes, and logic analyzers. In the last years Hewlett-Packard and Tektronix released logic analyzers with disassembling features.

In order to simplify the building and trouble-shooting process, one wants to have a direct access to the resources of the embedded system. The performance of the interface through which the embedded system would be accessed in this case is not of importance since a limited amount of control information is to be transferred.

The important point is for this interface to be simple, reliable, and easy to build.

#### **Figure 1.3: Embedded System Trouble-Shooting Configuration**

The strategy accepted during SAM-II prototype development is shown in Figure 1.3. Our 8-bit microcontroller, the Dallas DS80C320, has two on-chip serial interfaces and requires very few external resources to build an RS 232 compatible interface to connect the system to a standard ASCII terminal. From this point, we just need to hook up the ROM emulator to get a minimal configuration of a working system. The serial interface provides reliable and simple communication which is vital during the trouble-shooting process. Using the serial communication link, we started adding and troubleshooting the rest of the subsystems like the SCSI interface, the interfacing logic etc.

A typical application of this concept was the trouble-shooting of the SCSI interface. The SCSI interface was dying during system operation sometimes causing total communication failure without being able to continue to figure out what the reason was. Using the direct serial communication we were able to monitor directly the activities on the SCSI bus and in the system as a whole and solve the problem.

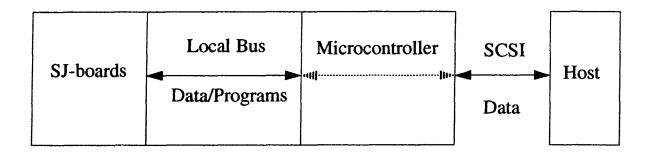

#### 1.1.4. SAM-II Embedded System

Even though SAM-II can be classified as an embedded system it has features which are relevant to servers and stand-alone computers. The overall system configuration has five basic components, Figure 1.4. A host computer, PC or workstation, used as a front-end interface, a high-performance SCSI bus connecting the host with SAM-II, a DS80C320 based microcontroller, a microcontroller local bus used to connect the SAM Junior (SJ) processing units, and the SJ processing units. With respect to the host the microcontroller is a typical embedded system. Its resources, the program and hardware are fixed, the host is defined and finite, the environment, the SJ-boards, is finite and predictable. The information transferred through the SCSI is a mixture of data and commands to the microcontroller.

#### Figure 1.4: SAM-II Embedded System Architecture

The uniqueness is coming from the presence and status of the SJ-boards which are active microprocessor subsystems. The SJ-boards are embedded with respect to the microcontroller. The data transferred through the SCSI to the microcontroller now can be interpreted as data or executable code. In this sense the SJ computing environment could be considered as a remote vector arithmetic server. By replacing the SCSI with an Ethernet or ATM interface, SAM-II can be connected to a network and used as a remote server by remote hosts running array processing applications.

#### 1.2. Test Methods

#### **1.2.1. General Concepts**

During the process of system development and later during system operation we have several levels of testing which naturally form a hierarchy of testing procedures: chip or component level test, board-level test and system level test.

At the lowest level we have chip-level test. The chip tests are conducted in two stages. First the chips are tested after manufacturing on special analyzing equipment and after that they are tested as a part of a real system. From a system development point of view we are interested in chip-level test where the chips are a part of functional system. Different chips are tested in different ways, for example the CPUs are tested differently from the memories, but the general method is to supply an input test sequence and check the response. Unfortunately, this might not be good enough since the chip is a part of a system and its output might be influenced by the other components. Also, with advances in the microelectronic technology it became possible to accommodate a number of fairly independent functional units, sometimes with a high-level of complexity like memories register files, ALUs, interface systems etc. on a single chip. In this case we want to have a better understanding of what is going on in the chip particularly when we are building a prototype. This imposes the necessity of special on-chip hardware for performing or providing the means to test chip functionality.

Embedded BIST circuitries are becoming very popular. Special on-chip circuitry is designed to perform complete chip functionality test. The BIST circuit is interfaced to provide some control if necessary and to check the result of the test. The BISTs are fast, very convenient when there are many chips to be tested, and they save main CPU time during the testing routine. Sometimes it is not possible or not necessary to design complete BIST circuits and other approaches should be used. A new technique called Boundary-Scan allows access to control points inside the chip and chip boundaries [25] and it simplifies the integration of different test mechanisms at chip- and board-level. A variation of Boundary-Scan is used in SAM-II [23] and we will discuss it in the following sections.

Board-level tests use the results from chip-level tests to verify chip functionality and they have more to do with intercomponent interactions, signal propagation, power distribution, and timing problems. They are testing the way the components interact and how their interaction affects overall board functionality. Board-level testing is not a trivial problem and a lot of interesting points could be discussed here. One of the problems we encountered during SAM-II prototype development was connected with the power distribution. The signals on the SCSI bus, for example, turned out to be very sensitive towards the board power distribution and power serge at one place even on different board due to invalid operation happened to affect them causing SCSI communication failure.

The system-level tests are testing the overall system functionality. They are usually a set of testing routines providing the system test control algorithm and checking system resources availability and access. Sometimes the results from the system tests are used by the operating systems, monitor programs and device drivers during system operation.

#### **1.2.2. Boundary-Scan Testing Principles**

One approach, which seems to be responding pretty well to the requirements of the new technologies and getting an wide acceptance is the Boundary-Scan. It requires little hardware resources, allows easy integration of chip-, board- and system-level tests and it also can be combined with BIST techniques for automated testing.

The idea of the Boundary Scan test is to connect all I/O pads under test, usually the pads at the boundaries of the chips, in a scan chain [IEEE-1149.1, 24, 25, 28]. It allows access to each individual chip but at the same time certain pads could be bypassed during testing to shorten the scan path. The technique could be used successfully at chip- board- and system-level and it also allows sample testing making possible to test control points on the board at a certain instant of time. Boundary Scan can be used to test points inside the chip as well as to conduct external tests on points between different chips' I/O pads.

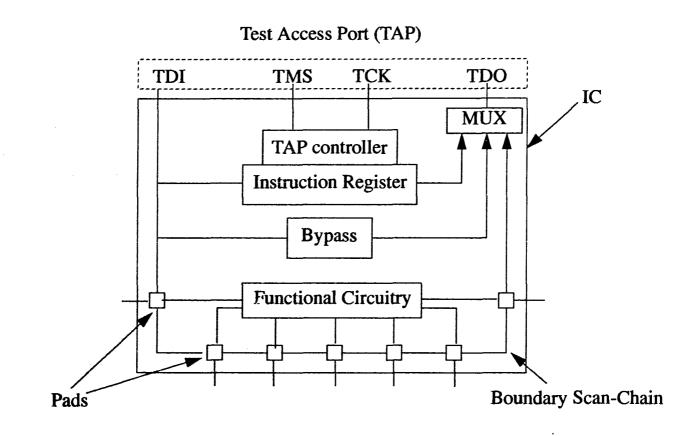

#### Figure 1.5: Single-Chip Boundary-Scan Architecture

The single-chip Boundary-Scan Architecture submitted by JTAG to IEEE in 1988 for a standard review is shown in Figure 1.5. Four additional pins are

necessary to configure the chip in a standard testing mode and for interfacing purposes - Test Data Input (TDI), Test Data Output (TDO), Test Mode Select (TMS) and Test Clock (TCK). TDI and TDO pins allow the chip to receive and send data from/to other chips. TMS and TCK are used to configure the chip for testing. These four pins constitute the Test Access Port (TAP).

The Instruction Register is used to store the test mode to be used and to select one of the possible data paths from the Boundary Scan-Chain, Bypass Register and user defined registers. The Boundary Scan-Chain can be used for internal as well as external tests.

#### **1.2.3. Scan Paths Implementations**

The Boundary-Scan testing concept undergoes continuous development and different variations are coming out sometimes in combination with other approaches. Texas Instruments has released a chip set compatible with the IEEE-1149.1 standard [28] allowing long chains to be broken into several shorter ones, easier to manage. There are several methods which integrate the Boundary Scan concept with BIST techniques for automated board-level testing [24, 26]. Also an interesting design [27] has been implemented using Boundary Scan to test for interconnection and power supply problems using on-chip amplifiers.

A standard JTAG/IEEE-1149.1 boundary scan interface has been incorporated into the Power PC 602 and 603 microprocessors to facilitate board-level testing [43]. Besides for testing purposes the standard JTAG port can be used to access a special interface that allows an external processor to read or write memory or any of the 603's internal registers.

The AMD's 29040 microprocessor has a JTAG scan-path based debugging hardware allowing to modify registers, memory and cache [45]. The microprocessor does not have dedicated pins to access the scan chains but rather the hardware has been designed in such a way so that two microprocessors could run in tandem in master-trace relationship.

ARM's ARM-7 microprocessor's JTAG scan-chain based debugger [45] allows to modify registers and memory, set hardware breakpoints and also the JTAG port can be used for ROMless boot-up and as an output serial port to drive an external device.

Intel's Pentium and P6 microprocessors also have on-chip JTAG scan-path

debuggers.

A variation of Boundary Scan has been realized in the SAM-Junior Control Processor (SJCP) and used in implementing SAM-II testing strategy. The scan chains provide the means to integrate chip- and board-level testing and also they are used for interfacing purposes as well, allowing access to the SJCP internal resources.

#### **1.3. Debugging Tools and Concepts**

Development of a program debugging system is an essential part of the system development process. In case of building a prototype the debugger serves two major purposes. First it is essential to be able to write correct programs and second in our case when the software development tools are not completely debugged we want to be able to verify syntactical and logical correctness of the programs used in the system testing procedures. Also, the debugger can be used for low-level resource manipulation by initializing memory blocks or performing some hardware configuration tasks.

#### **1.3.1. General Features**

A conventional debugging system [29, 31] performs tasks in two main areas program management and program environment management. Also it can perform some real time source code manipulation. In the program management area the debugger controls the overall program execution and some of the following or similar options are generally available:

- Stepping - it allows to step through the program a specified number of instructions one or more at a time. One might also be able to initialize the program counter.

- Breakpointing - it is used to suspend program execution at specified location and observe the program status. Usually one is able to edit the breakpoint table in real time. Some debuggers have a breakpoint counter associated with each breakpoint showing how many times a certain breakpoint has been encountered. An interesting feature is the so called programmable breakpoint. There is an expression associated with each breakpoint and a particular breakpoint is valid if the expression is true at this particular point of execution.

- Run - it allows the program to run full-speed and stop at any moment.

- Tracing - It allows information about all procedures and data structures or statements to be reported as the program executes.

- Continue - it starts program execution or resumes it after a breakpoint or a step.

- GoTo - it moves the execution pointer to a certain statement.

- Return - it moves the execution point to the exit point of the current procedure.

The above options provide the user with the necessary means to control the execution program flow. Beside that one needs tools to manage the program environment, to handle variables, data structures, procedure arguments etc. which directly affects the control flow.

- Environment Control Options - these are used to initialize the environment before or during a program execution. It provides scope to the debugger for identifying variables and statements.

- Stack - it allows to manipulate the stack, printing the current status of the stack or a traceback of certain number of stack frames.

- Symbolic Access Options - these options allow to refer to variables, tables or elements of arrays.

- Arguments - gives access to the arguments of an active procedure.

- Evaluate - it allows to evaluate a certain expression from the program.

- Assign - it assigns a value of expression to a name.

- Return - allows to set a return value from a procedure and moves the execution pointer to the exit point of the procedure.

Some debuggers also have the tools to examine the source code or the history of the program execution.

- Find - locates a line in the source file.

- Whe - reports a specified location or the current point of execution.

- Point - locates a line number within the debug listing file.

A debugger could have some or all of these features or even some specialized debuggers could have features specific to the particular application. For example debuggers running on parallel computers need to be able to handle concurrently running processes. This is relevant to the SAM-II architecture and is discussed in the following sections.

#### 1.3.2. Debugger System Interfacing

Initially the debugger systems were accessed through not very flexible and most of the time non-interactive command-line interfaces. The corresponding commands were typed at the system prompt in a way similar to typing commands at DOS or UNIX system prompts. In some cases also, the programmers had to write some kind of batch files or even to modify the source code to control the debugging process.

Modern debugging systems are highly interactive windowed tools employing advanced Integrated Development Environments (IDEs). The IDEs allow developers to edit, compile, link, load, execute programs in different modes, manipulate the environment in real time etc. They are proving to be the favorites of the program developers and the tendency is that they will stay on the market.

IDEs have one shortcoming [45], they are not real-time systems. Usually, the embedded software is meant to run on a real-time kernel or monitor reacting to external events in real time. Most of the IDEs do not provide real-time features during debugging. But recently, some companies released debugging systems which incorporate the so called OS-awareness. The debugger has features which let the developers obtain information about the OS status. There is an ongoing research in this direction and debugging systems are getting more responsive to real-time events.

#### 1.3.3. Simulators vs. Target System Debugging

The traditional approach is to debug the software on the target system. This approach seems to be the natural one. The software is debugged on the system it is supposed to execute on and all the tune-ups and fixes can be done during debugging. The developers are using conventional tools like ROM emulators and ICEs and most probably some form of IDE. Developing the software on the target system looks to be the straightforward way to go but, sometimes it might not be the most efficient one, particularly when we are talking about embedded system software development. In the last years simulators are becoming more and more popular. They provide a stable environment for program developers and basically full control over all the aspects of program development and debugging process. A special simulation tool, Basic RISC Architecture Timer (BRAT) [43], was designed to serve the purposes of Power PC microprocessors based software development and performance estimation. BRAT has been used for performance modeling of a number of Power PC microprocessors, it provides what-if analysis capabilities and sufficient accuracy during simulation. As far as debugging is concerned it allows to watch the state of the system cycle by cycle, to run certain number of cycles, backtrack certain number of cycles, run to certain address or instruction etc. BRAT provides both command line and windowed user interface.

#### **1.3.4. Debugging Parallel Programs**

Debugging parallel programs involves aspects of a new range of problems relevant to distributed and parallel computation The problems have to do with data consistency when the parallel processes are running in a shared memory or there is an active interprocess data exchange and also, with the so called race and deadlock conditions between processes running in parallel. There are several ways to guarantee process synchronization. One way is to use timestamps where a timestamp is associated with every shared data item. Another way is to use semaphores controlling the access to specific data items.

Using process synchronization techniques or not, debugging a parallel program could represent a challenge and requires additional attention and tools. A common approach is to replay the program execution. But, the program might have been written nondeterministicly or to have race conditions in which case we might get different results for different runs. One way to handle this is to trace the program execution by recording all the access to the shared data and use the trace later to reproduce the program execution. Many debuggers are recording all the traces but it could be a problem sometimes, the trace could be in order of tens of Mbytes. There are algorithms presented [32] which can decrease the trace length by 2 - 4 orders of magnitude recording only certain critical data.

Also, the debugger might incorporate race condition detectors. These detectors work in different ways depending on the data consistency protocols used. They might keep track of the timestamps of the shared data or the state of the programs or semaphores.

It is very difficult to create a universal algorithm because data consistency in general is not just a software problem. Data consistency protocols reflect the architecture of the machine, for example if we have a cache at each processor or not. If we have a shared memory and no cache, there is only one copy of the data in the memory and the consistency protocol would have to take care only of the memory. If we have a cache at each processor and distributed memory then things are getting more complicated because we have several copies of the same data in the memory and in the cache.

A very optimistic example would be considering a multiprocessor system with relatively independent processing units. In this case, we only need to be able to address the different units dynamically and debug every single executable image as in case of uniprocessor system.

#### 1.4. Objectives

In the attempts of researchers and engineers to build more and more powerful systems there are two fundamental approaches: distributed computation where more autonomous computer systems usually connected in a network are used to work in parallel on a certain application, and multiprocessor systems where the processing units are connected with high-speed buses or specialized interface networks. A multiprocessor system could be interfaced as a specialized server connected to a network, it might provide its own front-end interface or some more complex interface mechanism might be used. Usually the multiprocessor data processing environment is accessed by the user through a specialized interface controller(s) handling the interface protocol and managing the multiprocessor environment, the hardware and software interfacing concept, the system software etc. depends on the target application of the system, performance requirements, selected chip set and most probably on the price requirements if it is intended for the market.

The main objective of our research is the implementation of a multiprocessor computer system, SAM-II, based on a custom 32-bit vector-oriented RISC chip set intended for low-cost array processing applications. The system is not meant to compete at this point with the commercially available supercomputers, rather we are looking for solutions to certain architectural, interfacing and system software questions, which would let us in the future build a competitive product. Considering the chip-set and system architecture potentially large space requirements, it would not be possible to attach the system to an existing host's local bus and it should be accessed through an external interface as an embedded system. Also our intention is to make the system accessible by different platforms regardless of the vendor and operating system, which would not restrict the user with respect what kind of host computer to use. Considering these factors and the system performance requirements, we chose to use the SCSI interface which provides a good performance, it is available on most commercial workstations, and would allow the system to be interfaced as a conventional SCSI device.

Right now there is no off-the-shelf controller which would handle the SCSI bus data transfer and provide the access to the multiprocessor environment and we need to build a specialized interface controller (a motherboard) which would handle the SCSI bus protocol and manage the multiprocessor environment. We also need to design an on-board interface logic generating the proper processing unit interface control signals.

The processing units are based on a custom 32-bit chip set. Two of the system components, the control processor and memory manager, just came from the foundry and have not been fully tested yet. The chips have been tested independently under ideal conditions on a specialized testing equipment but the question is how they will behave as a part of a real system. The system will also serve as a test-bed for testing and verifying the functionality of the system components working independently and together as a vector-arithmetic processor. The processing unit board will also need an on-board interface logic allowing the processing unit to be attached to the motherboard and to be interfaced independently and in combination with other processing units.

The SCSI was originally designed to interface hard-disk drive systems and the protocol reflects hard-disk data transfer requirements. A major research point in the project is how to design and use the SCSI to interface a custom built embedded system efficiently. This might involve the design of our own protocol on top of the SCSI protocol.

The system software will consist of two major parts: a front-end system interface software running on the host computer and an embedded system monitor software running on the motherboard and probably partially on the processing units. The host software will provide the user interface and will handle the SCSI bus data transfers. The embedded system monitor will be handling the SCSI bus operations too and it will also perform the multiprocessor environment resource management.

An essential part of the system development process will be the implementation of a debugging system. The debugger would provide a low-level system resource management, the ability to load programs and data and to execute programs in different modes. It will also allow us to verify the accuracy of the current compiler software which has not been tested completely yet.

Here is the summary of our objectives in the project:

\* Design and development of a DS80C320 based motherboard

\* Design and development of an SJ-chip-set-based processing unit board

\* Verifying that SJCP and SJMI can work together

\* Design of a FPGA-based motherboard-parallel processing units interface logic

\* Embedded system SCSI interface hardware and firmware development

\* System and test software development

\* Embedded system debugger development

## **Chapter 2: Hardware Design**

#### 2.1. SAM-II Architecture

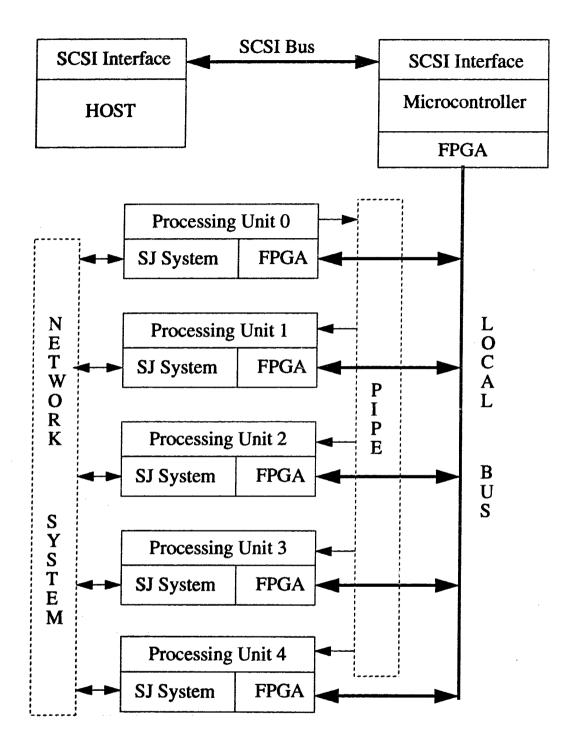

SAM-II (Structured Architecture Machine - II) is an embedded multiprocessor vector-oriented computer system intended for low-cost array processing applications. It develops further the concepts and the ideas in the first implementation of the Structured Architecture Machine, SAM-I [46] and is a stepping stone towards the development of a massively parallel computer system.

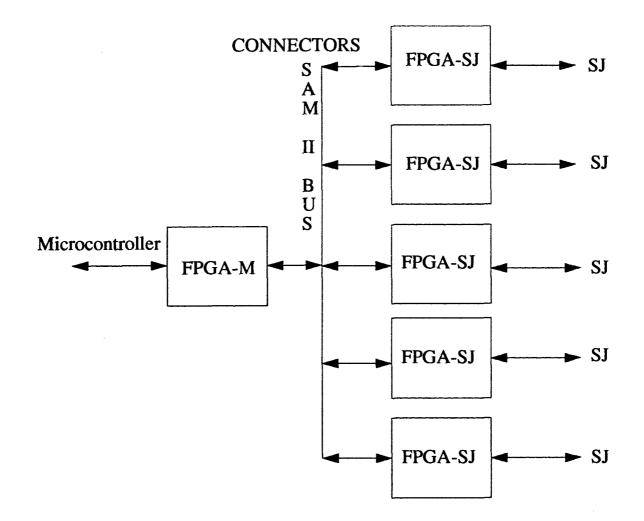

The prototype (Figure 2.1, Figure 2.2) is designed to accommodate up to five processing units based on a custom 32-bit vector oriented RISC chip set. Each processing unit could have up to 64 Mbytes of four-stage interleaved system DRAM and 64 kwords of high-level 64-bit-wide microcode SRAM used as the CPU external program storage. The microcode is loaded dynamically, which gives some flexibility to the system.

The system could be configured to work as an MIMD (Multiple Instruction Multiple Data) machine in which case the processing units execute independent code or as an SIMD (Single Instruction Multiple Data) computer where one of the processing units plays the role of a program manager broadcasting instructions to the other four data management units through a specialized instruction-pipe interface. The pipe interface has not been implemented yet and right now the processing units program execution is controlled directly by the microcontroller.

The processing units are attached to a motherboard (microcontroller) and each one maps to 256 locations of the motherboard CPU directly accessible memory and can be accessed in a single microcontroller stretched machine cycle. FPGA based logic is designed to perform the necessary bus control and control interface signals generation. Without the pipe interface, the microcontroller plays the role of a program manager and all five units can be used to process data.

Usually in multiprocessing applications there is an intensive data transfer among the processing units during a program execution. A special software and/or hardware support is necessary to guarantee real-time data consistency in case of shared data applications. A special network system will be designed to interconnect directly the processing units data memory systems to handle data exchange and data consistency.

Figure 2.1: SAM-II Architecture

The embedded system is interfaced with the host computer through a fast SCSI interface. From the host's point of view, SAM-II is a conventional SCSI device hooked on the SCSI bus and all data transfers between the host and the embedded

system use the SCSI bus protocol. In this relationship the microcontroller serves two main purposes. First it is a dedicated SCSI driver handling the data exchange on the SCSI bus and second it performs the necessary SAM-II system management functions including system configuration, program management, and data management.

Figure 2.2: SAM-II Prototype

The host and the embedded system interact through a request-driven communication. The host sends a request to the embedded system which could be anything from performing a test to executing a program and the embedded system serves the request and sends the result back. The requests and results are transferred by means of SCSI transactions. The requests are classified in four areas - system test, system configuration, program management, and data management. With respect to the application program SAM-II could be seen as a vector-arithmetic coprocessor accessed through the operating system using conventional system calls.

#### 2.2. Microcontroller

The embedded state of SAM-II multiprocessor imposes the necessity of a specialized microcontroller to service the embedded system-host interface and to control certain activities on the SJ-boards. From the host's point of view, SAM-II is a conventional SCSI device hooked-up to the SCSI bus and this determines pretty much a client-server relationship, the host sends the request, the microcontroller serves it and sends the result back, if any.

With respect to the host, the microcontroller should be able to serve requests in the following areas:

- System test - this would involve testing different system memories like the external microcode storage, external DRAM and on-chip memory and register files, testing separate functional units and inter-system-component interfaces.

- Program/Data loading and Verification - one of the major functions the microcontroller should perform is loading and verifying executables and data into the SJ boards.

- Program management - the microcontroller should be able to control the program execution full-speed, step-by-step, stop execution etc.

Microcontroller also has some monitoring functions concerning the overall system performance. In general, we might have several executables residing in the microcode storage at the same time, some of them system programs, some of them user applications. The monitor should be able to load executables at the proper locations, to start/stop one or another module and to be able to recognize when a certain module has finished. In other words, all the basic functions a conventional operating system would have.

The custom SJ chip set, designed at SFU's VLSI and Computer Design Laboratory, provides excellent hardware support for the implementation of the above functions. Some of these features are hardware-supported boundary-scan testing capabilities and quite straight-forward control interface. The SJ-boards are part of the microcontroller address space and a certain function on a certain board (Processing Unit) is triggered by addressing a specific location. The list of the functions is given in the Appendix.

#### 2.2.1. System Design

The microcontroller is based on Dallas DS80C320 microprocessor, which is an enhanced version of Intel's 8051, capable of running at higher speeds with an

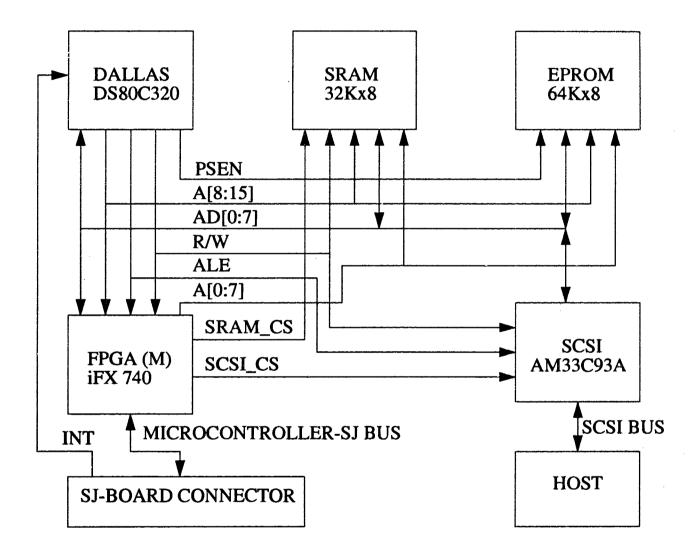

additional serial port, data pointer, and timer. This makes it very suitable for building embedded systems since, we have on-chip serial interface and we need few external resources to build a minimal-configuration working system. This is important when it comes to building prototypes, one needs a reliable connection to the external world to be able to monitor the state of the system in the process of development. The block diagram of the microcontroller is shown in Figure 2.1.

#### Figure 2.3: Microcontroller Block-Diagram

#### 2.2.1.1. Address Space

The microcontroller has separate program and data address spaces. This is typical for many computer systems but as our research showed it could be a reason for some undesired effects to take place. Addressing separate spaces generally results in changing high-order bits of the address when switching from one space to another, particularly bits which are used in decoding different components of the system. This could cause glitches on the decoding lines and respective malfunctioning. By changing the program location, one could get different system behavior. These kind of problems are very difficult to figure out since, they might appear only in combination with other events taking place on the boards.

Jumper-configurable, we could have 32k or 64k of program memory. The jumper turns on/off the A15 address line. We have been using PROMICE firmware development tool to emulate our program storage. The PROMICE ROM emulator could be connected to a PC through the standard serial or parallel interfaces and accessed and controlled through a command-line interface. Several PROMICE devices, each emulating 8-bit-wide memory, could be connected in parallel to emulate wider ROM storage of up to 512 kwords deep.

The data address space is divided among the system data SRAM, the SCSI protocol controller, and the SJ boards. The prototype could accommodate up to five SJ boards each corresponding to 256 bytes of addressable memory. The decoding scheme is shown in Table 1.

| A15 | A14 | System Components        |

|-----|-----|--------------------------|

| 0   | X   | 32k of system SRAM       |

| 1   | 0   | SCSI protocol controller |

| 1   | 1   | SJ boards                |

**Table 1: Microcontroller Address Decoding Scheme**

Partial decoding is used. For our purposes 32k of SRAM is enough although, considering maximum-size SJ executable of 512k would complicate the loading protocol. But in any case we couldn't have more than 64k.

#### 2.2.1.2. SCSI protocol controller

We are using the AMD Enhanced SCSI-Bus Interface Controller Am33C93A. It has 32 addressable registers and it is located directly on the CPU bus. The chip is configured to take advantage of the multiplexed address/data bus. The register address is latched internally at the falling edge of ALE and if the chip is selected a

read or write operation takes place.

DMA and interrupt handling are disabled and data transfer takes place by polling the status bits. This approach was adopted primarily because during building the prototype we wanted the software to run predictably and reliably. Even when something goes wrong it should keep running to report the state of the system. The choice also fits very well with the request-driven initiator-target relationship between the microcontroller and the host imposed by the SCSI bus protocol. In this way the system components' priorities are determined entirely by the software which is preferable during the trouble-shooting procedure.

Of course other solutions are possible. An interrupt handling approach would require a different software architecture. The request-driven communication still could be preserved but in general we will need interprocess communication mechanism between the different subroutines working on the completion of a single request. The software details are discussed in later sections.

# 2.2.1.3. SJ Boards

The prototype is designed to accommodate up to five boards. Each board has a unique 3-bit ID which is jumper-configurable.

In the first decoding scheme implementation, the address lines A11, A12 and A13 were used as SJ board ID bits, Table 2. They were passing directly to the SJ boards to be compared with the ID jumpers. The selection of a particular board was taking place dynamically within the timing of the current instruction. There are two special combinations, one selects all boards which means that the following activity read/write will take place on all boards and the other prohibits any activities on any of the boards. Sometimes though at procedure calls or during changing address spaces, we observed glitches on some of the lines. Usually the glitches were small but there was a possibility that sometimes they might get big enough to cause a trouble.

| A13/D2 | A12/D1 | A11/D0 | Function                 |

|--------|--------|--------|--------------------------|

| 0      | 0      | 0      | No one board is selected |

| X      | X      | X      | Unique SJ board ID       |

| 1      | 1      | 1      | All boards are selected  |

Table 2: SJ board Identification - Version 1

In the second implementation the access to a particular board is divided in two parts. First the board is selected and after that its space is accessed in subsequent instructions. The board address is passed over the data bus using D0, D1, and D2 data lines. The result of the comparison with the ID jumpers is latched and used to enable the board for subsequent operations until the board is deselected. Once selected the board is accessible as a conventional memory location. The A13, A12 and A11 address lines are used to choose different selection options, Table 3. This scheme avoids eventual glitching problems, since the actual board access is separate in time from the board selection. Note the broadcast feature, which permits special subsets of the boards to be selected.

| A13 | A12 | A11 | Selection Function                              |

|-----|-----|-----|-------------------------------------------------|

| 1   | 1   | 1   | Select all unit; data bus ignored               |

| 1   | 1   | 0   | Select upper half units; data bus ignored       |

| 1   | 0   | 1   | Select lower half units; data bus ignored       |

| 1   | 0   | 0   | Select single unit; D2, D1, D0 have the unit ID |

| 0   | 0   | 1   | Select FPGA location                            |

| 0   | 0   | 0   | NOP; A7-A0 have a selected-board location       |

Table 3: SJ board identification - Version 2

Each SJ board is mapped to 256 addressable locations of DS80C320 data memory. The first 128 addresses are used to access the SJCP scan chains and for control purposes. A complete list of the available functions is given in the Appendix. The second 128 addresses are used to access an SJCP internal SRAM block. The access to any location takes place within the timing of a single stretched data memory access instruction.

All SJ boards have a common reset line controlled by the system reset. Each SJ board has a dedicated interrupt line which is connected directly to one of the interrupt inputs of Dallas microprocessor. The interrupts are currently disabled and the handling is done by polling.

The physical interface between each board and the microcontroller is realized through pairs of FPGAs which perform decoding and bus control functions. The details are discussed in the following sections.

### 2.2.1.4. System Clocks

Clock generation is critical for proper system performance. We are using a Cypress CY7B992 Programmable Skew Clock Buffer (PSCB) to generate the necessary clock sequences. PSCB is capable of generating four clock sequences with possible relative shift of +/-180 degrees. One is used as clock input for DS80C320 and SCSI chips and two others are providing PHI1 and PHI2 clock sequences for the SJ boards. The skews are jumper-configurable, Table 4.

As we found out the relative timing between PHI1, PHI2 and the microcontroller clock is decisive for the proper system performance. PHI1 and PHI2 should be shifted at 90 degrees. This provides four equal time intervals timing different activities in the SJCP machine cycle. In reality though the situation is different, the time intervals could differ by as much as 40% with respect to the reference clock. The reasons for this are the PSCB resolution, ringing on the clock lines, propagation delays and different rising and falling times.

| Jumpers  | Function                                                                    |

|----------|-----------------------------------------------------------------------------|

| 1F0, 1F1 | Jumpers fixed (Open) Reference Clock                                        |

| 2F0, 2F1 | DALLAS System Clock, respectively<br>controlling ALE, READ and WRITE timing |

| 3F0, 3F1 | SJ System Clock, PHI1                                                       |

| 4F0, 4F1 | SJ System Clock, PHI2                                                       |

#### Table 4: System Clocks Configuration

At the same time PHI1 and PH2 should be synchronized with the DS80C320 bus control signals like READ, WRITE and particularly ALE. ALE triggers a finite state machine in SJCP which is going through 16 states (8 states for internal DPM access). Everything should be timed precisely in order for the data transfer to complete correctly.

The tuning of the system clocks goes through two stages. First, we tune the skew between PHI1 and PHI2 to be as close to 90 degrees as possible. Second, we tune ALE by shifting appropriately the microcontroller system clock.

The microcontroller system clock has no effect on the functionality of the SCSI interface.

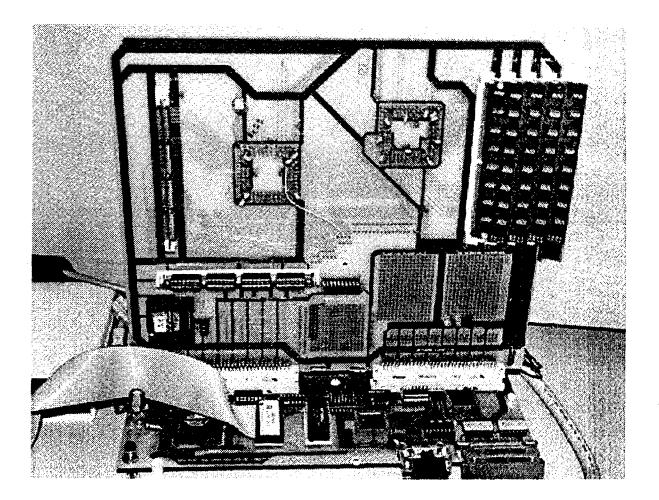

# 2.2.2. Board Design

We are using four layer Printed Circuit Boards. The first and forth layers are signal layers while the second and third layers are power and ground layers respectively. The microcontroller board is shown in Figure 2.2. Table5 shows the function of each jumper.

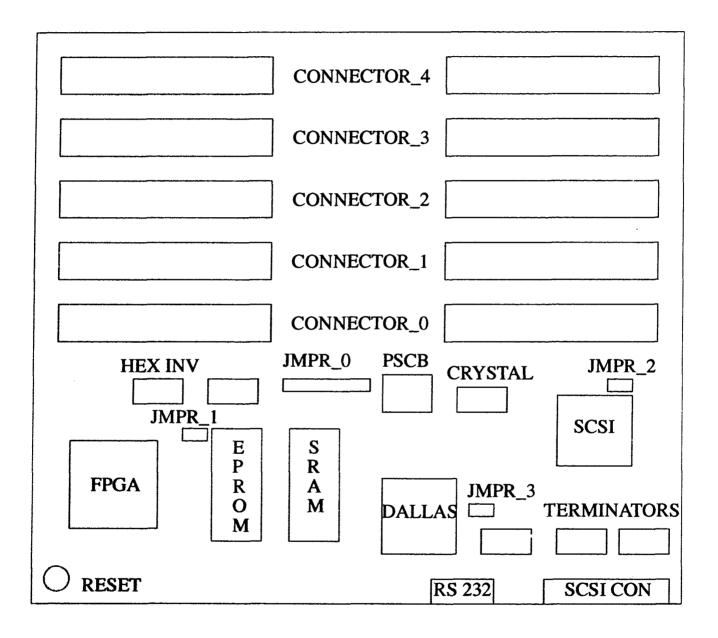

# Figure 2.4: Microcontroller Board Layout

Dedicated POWER and GROUND layers help to reduce noise, crosstalk, and short circuit effects on the board. Also, it seems that one of the problems we encounter is associated with power distribution. That's why it is very important to supply as much independent power to each component as possible.

| Jumper | Function                                                                                           |

|--------|----------------------------------------------------------------------------------------------------|

| JMPR_0 | Clock Configuration Jumpers. See Table 3.                                                          |

| JMPR_1 | Program Storage Configuration Jumper. OFF - 32k, ON - 64k                                          |

| JMPR_2 | SCSI Reset Line Configuration Jumper.<br>OFF - reset from the SCSI bus, ON - system reset          |

| JMPR_3 | SCSI Interrupt Configuration Jumper.<br>OFF - SCSI interrupt disabled, ON - SCSI interrupt enabled |

**Table 5: System Configuration Jumpers**

The SCSI terminators are powered by the HOST, in our case by the PC through the cable. According to the SCSI specification, terminators should be powered by the SCSI bus but if necessary, local power could be supplied through a jumper.

The SJ boards attach to the microcontroller mother-board through pairs of 96pin connectors. On the prototype we have five pairs of connectors. Each pair has a separate interrupt line. Since the interrupts are disabled, all boards have the same priority or the priority is determined by the order of polling. If the interrupts are enabled CONNECTOR\_0 has the highest priority, this is where the Program Management Unit (PMU) will be plugged, and CONNECTOR\_4 has the lowest priority.

## 2.3. SJ Processing Unit Board

SAM II Processing Unit (PU) is based on a custom 32 bit vector-oriented chipset designed at SFU. The chip-set consists of:

- SJCP - 32-bit one-stage pipelined vector-oriented microprocessor employing 64-bit-wide high-level microcode. It is capable of executing up to 4 microoperations per clock cycle at peak performance.

- SJMI - 32-bit four-stage interleaved memory management unit. It can handle up to 64 Mbytes of interleaved memory organized in four banks.

- SJNI - 32-bit network controller, it is intended to handle direct data transfer between the Processing Units for efficient array manipulation.

- SJFP - Floating-Point Unit.

- SJIVU/SJOVU - instruction pipe control units.

Depending on its functions in the system each PU could be either a Program Management Unit (PMU) or a Data Management Unit (DMU). The PMU performs program-execution control functions, It broadcasts vector-algorithm instructions through an instruction-pipe interface. The DMUs are engaged only in data processing activities. In principle, the system could have one PMU and many DMUs. The prototype is designed to accommodate five boards altogether, one PMU and four DMUs.

#### 2.3.1. SJ-board System Design

At the time we started building the prototype, only SJCP and SJMI chips were available so we were able to build a minimal configuration of SJ computing system consisting of the microprocessor module and data storage manager. The block diagram is shown in Figure 2.3. On the board we have reserved space for the rest of the system components and also we have intercomponent-interface pad arrays to connect the new components to the system.

#### **2.3.1.1. Microprocessor Module**

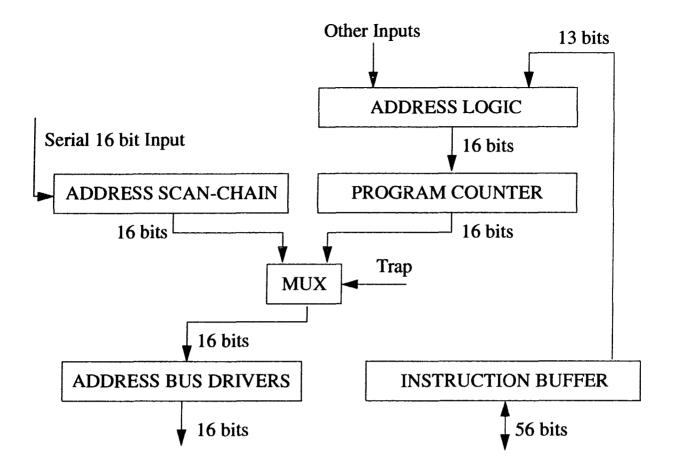

All the activities on the SJ-board are controlled by SJCP control processor. SJCP has 64k-word external microprogram storage. In future versions the microprogram storage might be on-chip. The microinstruction is 64 bits wide but actually SJCP is using only 56 bits. The other 8 bits (so called Y field) are specific for the Floating-Point Unit. The loading of the Microprogram memory takes place through the SJCP internal scan-chains. First, seven bytes are written consecutively into the instruction scan chain while the eighth byte is put on the Y BUS from the on-board FPGA. After that all eight bytes are strobed into the microprogram store at the address preloaded in the SJCP internal address scan-chain. In execution mode, the microprogram store is permanently enabled for reading, it is writable only during loading. We call this a read-mostly memory.

Access to SJCP resources is possible through an eight-bit address/data bus and a couple of control signals, CTR\_0 and CTR\_1, which specify the RD or WR

operation to take place. The operation could be a conventional data transfer or it could trigger a certain activity in SJCP. The lower eight address bits are latched in a on-chip address register during ALE and subsequently decoded to determine the selected function. The decoding of the control signals is shown in Table 6.

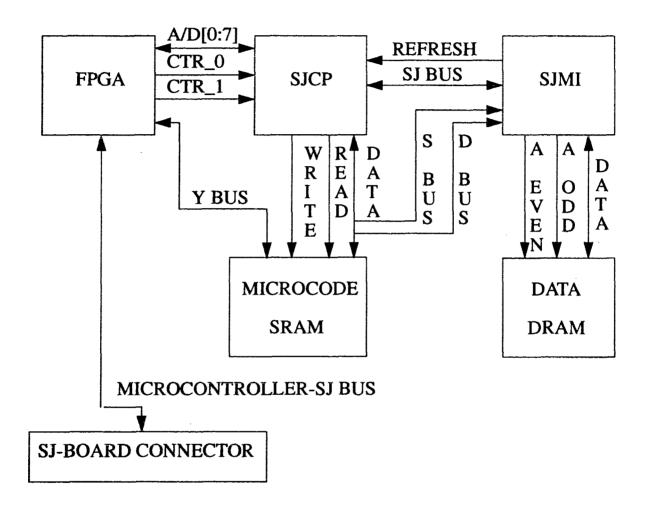

Figure 2.5: SJ-board Block Diagram

The generation of the control signals is not a trivial problem and it is discussed in detail in the next section. It is done through a pair of FPGAs which also perform bus control and decoding functions. Due to a shortage of I/O pins on SJCP, the microcontroller's three bus control signals were encoded into the two CTR1 and CTR0 signals.

| CTR_1 | CTR_0 | Operation |

|-------|-------|-----------|

| 0     | 0     | READ      |

| 1     | 0     | NOP       |

| 0     | 1     | WRITE     |

| 1     | 1     | ALE       |

**Table 6: Control Signals Decoding**

SJCP is connected with the Memory Manager (SJMI) by a 32-bit bidirectional bus (SJ BUS) which is used to transfer data between the two modules during program execution. SJMI is controlled by two instruction fields called source (S field) and destination (D field). SJCP stops when active REFRESH is detected, this happens when SJMI performs a DRAM refresh, and resumes when REFRESH goes away.

SJCP has 166 32-bit words of internal dual-port SRAM used as data storage or in data transfer operations between SJCP and SJMI, SJCP and the microcontroller, and SJMI and the microcontroller. This dual-port memory takes 128 addresses of DALLAS address space and a 3-bit bank register is used to access different 128byte banks.

## 2.3.1.2. Memory Management

SJMI can handle up to 64 Mbytes of interleaved DRAM organized in four banks, two even and two odd, each 32 bits wide. It has on-chip refresh logic with a programmable refresh cycle. In the prototype we are using four 4 Mbyte SIMM modules for a total of 16 Mbytes.

During instruction execution, the source and destination fields of each microinstruction are passed from the microprogram storage to SJMI and other coprocessors along the S and D buses to specify the source and destination of the data transfer, if any.

# 2.3.2. Board Design

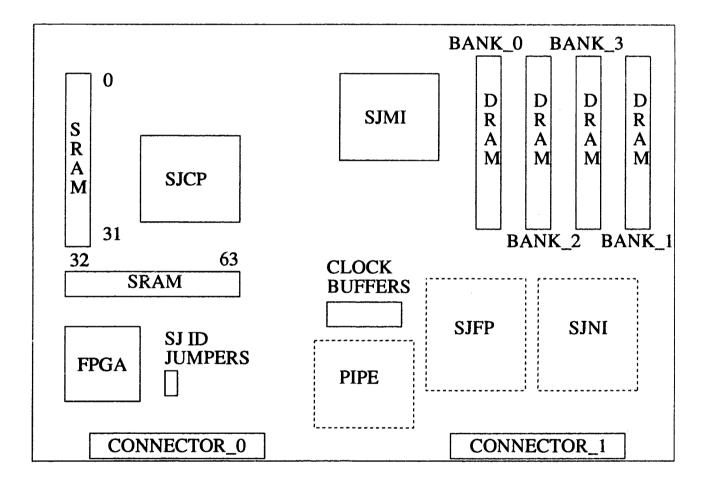

The board layout is shown in Figure 2.4. It is again a four-layer printed circuit

board. The first and forth layers are signal layers while the second and third layers are power and ground layers respectively.

The SJ-board connects to the microcontroller board by means of a pair of 96 pin connectors. CONNECTOR\_0 is used to attach the board to the microcontroller bus while CONNECTOR\_1 will be used for inter-process communications. It has three SJ ID configuration jumpers specifying the unique address of a particular board. The boxes drawn with a dashed line show the places reserved for the Instruction-Pipe Unit, Floating-Point Unit, and the Network Controller.

# Figure 2.6: SJ-board Layout

The clock buffers are used to buffer and invert the PHI1 and PHI2 system clocks coming from the PSCB on the microcontroller board through CONNECTOR\_0.

The board architecture could be improved along several lines. If we rotate the SJCP and SJMI modules in 180 degrees, this would shorten the address/data bus

traces between the FPGA and SJCP minimizing the ringing and crosstalk. We also can improve the system clock propagation delays, if we keep the SJCP clock inputs close to the bus connectors.

When we started designing the board, we used the SJCP and SJMI pin layout diagram given to us by the manufacturer. It was not until the board was ready for manufacturing, when we found out that actually we had the mirrored image of the pinout. At this point we had two alternatives: to redesign the board or to solder the SJCP and SJMI on the back side of the board. We chose the second one mainly for timing reasons. This will be fixed in later implementations.

## 2.4. Microcontroller - SJ Boards Interface

The microcontroller is facing the problem of how to interface efficiently multiple Processing Units. Some multiprocessor systems with large number of PUs have several levels of local buses even some custom networking which in any case involves buffering. In our case, each PU represents 256 bytes of directly addressable memory and all the transactions take place within one stretched microcontroller machine cycle. But even though the prototype has only five PUs, we still need to consider such factors like bus-lines overloading and signal propagation delays, and of course the timing.

In general, the basic functions the microcontroller-SJ-boards interface should be able to perform are:

- Address/Data Bus Control - The microcontroller and the SJ-boards are on the same physical bus. The interface logic should be able to control the direction of the bus depending on which device is driving it. Usually the bus is driven from the microcontroller towards the SJ boards. Only when we have a read from a particular PU, the bus direction is reversed. This is done to prevent the five SJ boards driving the bus at the same time, which would result in a short on the bus lines.

- Decoding - The SJ boards are in the microcontroller address space together with the SRAM and SCSI protocol chip. The interface logic should be able to identify each board uniquely in order to avoid bus contests and to generate the proper set of control signals. The decoding is done in two stages (see below please).

- Control Signals Generation - From one side we have the DS80C320 bus and on the other side the SJCP external interface. The interface logic should perform the necessary decoding and conversions in order to generate the proper control sequences.

## 2.4.1. Physical Datapath

The interface logic is realized through a pair of FPGAs, one on the microcontroller board, which I will refer to as FPGA-M and one on each SJ board, FPGA-SJ. FPGA-M performs partial decoding and bus control functions and FPGA-SJ completes the decoding process and generates the necessary control signals. Since the FPGAs have limited internal resources and limited number of external inputs, the functions should be distributed evenly between them.

**Figure 2.7: Physical Datapath**

The DS80C320 bus goes to FPGA-M and after that it directly connects to

as many as five FPGA-SJ units, which expands the bus into five separate buses, Figure 2.5.

As far as the dataflow is concerned, the FPGAs are playing simply a buffering role. The bus is driven normally towards the SJ boards and only during a decoded read it reverses its direction.

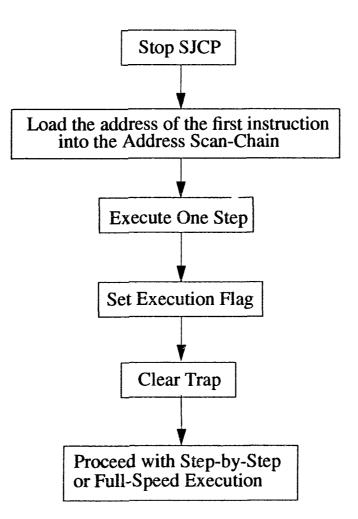

# 2.4.2. Microcontroller FPGA Design