## Test Vehicle for a Wafer Scale Field Programmable Gate Array

by

Benoit Dufort

B.A.Sc., Université Laval, 1993

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF APPLIED SCIENCE IN THE SCHOOL OF ENGINEERING SCIENCE

© Benoit Dufort 1995 Simon Fraser University July 1995

All rights reserved. This work may not be reproduced in whole or in part, by photocopying or other means, without permission of the author.

## Approval

| Title of Thesis: | Test Vehicle for a Wafer Scale |

|------------------|--------------------------------|

| Degree:          | Master of Applied Science      |

| Name:            | Benoit Dufort                  |

**Field Programmable Gate Array**

**Examining Committee:**

Dr. M. Jamal Deen, Chairman

Dr. Glenn H. Chapman, Setfior Supervisor

Dr. Richard F. Hobson, Supervisor

Dr. Colombo R. Bolognesi, Examiner

Date Approved: July 1395

#### PARTIAL COPYRIGHT LICENSE

I hereby grant to Simon Fraser University the right to lend my thesis, project or extended essay (the title of which is shown below) to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its usrs. I further agree that permission for multiple copying of this work for scholarly purposes may be granted by me or the Dean of Graduate Studies. It is understood that copying or publication of this work for financial gain shall not be allowed without my written permission.

**Title of Thesis/Project/Extended Essay**

"Test Vehicle for a Wafer Scale Field Programmable Gate Array"

Author:

(signature)

Benoit DUFORT (name)

<u>July 11, 95</u> (date)

### Abstract

Field Programmable Gate Arrays are growing steadily in use and have already change the way designers build digital circuits. With their low cost and very fast turnaround time, they are especially well suited for prototyping new designs. However, the general nature of FPGAs implies a circuit density much lower than custom designs. This currently limits the size of the circuits that can be implemented on a single FPGA to 40000 equivalent gates . Boards of FPGAs are used, but their speed remains slow, because of the large capacitance of the inter-chip routing.

This thesis investigates the use of Wafer Scale Technology to expand the size of FPGAs to 3 million gates for a 200mm wafer. The defect avoidance proposed uses the laser link technology to restructure the circuit in a square array. Two different techniques, the row-column substitution and the combination of cell by cell and column substitution, are analyzed. The first one is proposed to increase the yield of small FPGAs while the second one is designed to restructure wafer scale chips. Simulations to show the effect of the restructuring on the chip yield are presented.

The proposed design is described and the defect avoidance structures explained in detail. A new kind of device, called the testable laser link, has been designed and tested. Its application in the wafer scale FPGA is presented, both in the power distribution and the reconfiguration. Two chip sized test vehicles incorporating the restructuring devices described in the thesis have been successfully fabricated and the results of different tests of cells and signal routing are analyzed. These indicate that a wafer scale FPGA would be feasible with the described techniques.

## Acknowledgments

I wish to thank my senior supervisor, Dr. Glenn Chapman, for his help and guidance during this work. I also wish to thank my family and friends for their constant support during my time at Simon Fraser University.

I would like to thank the Canadian Microelectronic Corporation for fabricating the chips presented in this thesis.

This work was supported in part by the Natural Science and Engineering Research Council of Canada, the SFU Center for System Science and the British Columbia Advanced System Institute.

## **Table of Contents**

| Approval                                     | ii   |

|----------------------------------------------|------|

| Abstract                                     | iii  |

| Acknowledgments                              | iv   |

| Table of Contents                            | v    |

| List of Figures                              | ix   |

| List of Tables                               | xiii |

| Chapter 1: Introduction                      | 1    |

| 1.1 General                                  | 1    |

| 1.2 Applications                             | 4    |

| 1.3 Thesis Objectives                        | 4    |

| 1.4 Thesis Organization                      | 5    |

| Chapter 2: Theory of Wafer Scale Integration |      |

| and Field Programmable Gate Arrays           | 7    |

| 2.1 Wafer Scale Integration                  | 7    |

| 2.1.1 Active Switches                        | 8    |

| 2.1.2 Permanent Switches                     | 9    |

| 2.1.3 Laser Link                             | 9    |

| 2.2 Field Programmable Gate Arrays           | 10   |

| 2.2.1 What is an FPGA?                       | 11   |

| 2.2.2 FPGA Architectures                     | 12   |

| 2.2.3 FPGA Applications                      | 13   |

| 2.2.4 Implementation Process                 | 14   |

| 2.2.5 Commercially Available FPGAs           |      |

| 2.3 Summary                                  |      |

| Chapter 3: Laser Linking Wafer Scale Integration        |

|---------------------------------------------------------|

| 3.1 Mitel 1.5µm Technology Parameter Extraction         |

| 3.1.1 Laser Table Setup17                               |

| 3.1.2 Laser Link Power Calculations                     |

| 3.1.3 Laser Power Experiments                           |

| 3.1.4 Laser Link Experiment                             |

| 3.1.5 Laser Cut Experiments                             |

| 3.1.6 Damage to Silicon Nitride                         |

| 3.1.7 Batch Linking and Cutting                         |

| 3.1.8 Linking Summary                                   |

| 3.2 Practical Example: Test Vehicle for a Wafer Scale   |

| Thermal Pixel Scene Simulator                           |

| 3.2.1 Design                                            |

| 3.2.2 Experimental Procedure                            |

| 3.2.3 Experimental Results                              |

| 3.3 Summary                                             |

| Chapter 4: Defect Avoidance in FPGAs                    |

| 4.1 Defect Avoidance                                    |

| 4.1.1 Fabrication Defects                               |

| 4.1.2 General Defect Avoidance                          |

| 4.1.3 Making the Defect Avoidance Invisible to the User |

| 4.2 Restructuring of a 2-D Array                        |

| 4.2.1 Row-Column Substitution                           |

| 4.2.2 Cell by Cell Substitution                         |

| 4.2.3 Row-Column and Cell Substitution 40               |

| 4.3 Algorithms and Yield Simulations                    |

| 4.3.1 Defect Distribution Simulations                   |

| 4.3.2 Row-Column Restructuring                          | 44   |

|---------------------------------------------------------|------|

| 4.3.3 Cell by Cell Restructuring                        | 49   |

| 4.4 Design Considerations for Defect Avoidance in FPGAs | 57   |

| 4.4.1 Power Routing                                     | 57   |

| 4.4.2 Clock                                             | 60   |

| 4.4.3 Routing                                           | 61   |

| 4.4.4 Line Redundancy                                   | 68   |

| 4.4.5 Programming Circuit                               | 69   |

| 4.4.6 Testing                                           | 70   |

| 4.5 Software Overview                                   | 71   |

| 4.5.1 Restructuring Software                            | 71   |

| 4.5.2 Programming Software                              | 74   |

| 4.6 Summary                                             | 74   |

| Chapter 5: The Test Vehicle                             | .75  |

| 5.1 Design                                              | 75   |

| 5.1.1 Architecture                                      | 76   |

| 5.1.2 FPGA Programming Technology                       | 76   |

| 5.1.3 Logic Block                                       | 77   |

| 5.1.4 Connection Box                                    | 78   |

| 5.1.5 Routing                                           | 80   |

| 5.1.6 Chip Layout                                       | 81   |

| 5.2 Power                                               | . 88 |

| 5.3 Delay                                               | . 89 |

| 5.3.1 Delay Approximation                               | . 89 |

| 5.3.2 Delay Simulations                                 | . 90 |

| 5.4 Delay Experiments                                   | . 94 |

| 5.4.1 Routing Delay                                     | . 94 |

| 5.4.2 XOR Delay Test                     |     |

|------------------------------------------|-----|

| 5.4.3 Laser Linked Paths                 |     |

| 5.4.4 Double Length Lines                |     |

| 5.4.5 The Ring Oscillator Test           |     |

| 5.4.6 Larger Cell Simulation             |     |

| 5.5 Summary                              | 107 |

| Chapter 6: Conclusion                    |     |

| 6.1 The Test Vehicle                     |     |

| 6.2 Technical and Economical Feasibility |     |

| 6.3 Future Work                          |     |

| 6.4 Summary                              |     |

| List of References                       | 112 |

| Appendix A: Hspice Ring Oscillator File  |     |

## **List of Figures**

| Figure 1.1: FPGA Block Diagram                                                 | 2  |

|--------------------------------------------------------------------------------|----|

| Figure 2.1: Mitel 1.5µm CMOS Laser Link                                        | 10 |

| Figure 2.2: Conceptual Simple FPGA                                             | 11 |

| Figure 2.3: FPGA Implementation Process                                        | 15 |

| Figure 3.1: Laser Table Setup                                                  | 18 |

| Figure 3.2: Cross Section of the Linking Process                               | 19 |

| Figure 3.3: Graph of the Power vs. Depth of the Melt Front                     | 21 |

| Figure 3.4: Position of the Laser Zaps                                         | 23 |

| Figure 3.5: Photograph of the Links                                            | 23 |

| Figure 3.6: Two Methods for Cutting Large Metal Lines                          | 24 |

| Figure 3.7: Photograph of the Cutting Methods                                  | 25 |

| Figure 3.8: Photograph of the Damage in the Silicon Nitride                    | 26 |

| Figure 3.9: Photograph of the Transducer Cell                                  | 29 |

| Figure 3.10: Photograph of the Test Chip                                       | 30 |

| Figure 3.11: Optical Probing                                                   | 30 |

| Figure 3.12: Design Schematic                                                  | 31 |

| Figure 4.1: Three Categories of Defects: a) Logic Defect: eg. Gate Oxide Hole; |    |

| b) Power Defect: eg. Power Short;                                              |    |

| c) Routing Defect: eg. Bus Open Circuit and Bus Short                          | 34 |

| Figure 4.2: Two Redundancy Classes: a) Global Sparing; b) Local Sparing        | 36 |

| Figure 4.3: Row-Column Substitution                                            | 38 |

| Figure 4.4: Vertical Cell by Cell Substitution                                 | 39 |

| Figure 4.5: Row-Column and Cell Substitution                                                |

|---------------------------------------------------------------------------------------------|

| Figure 4.6: Defect Map Example ( $\lambda$ =0.1)                                            |

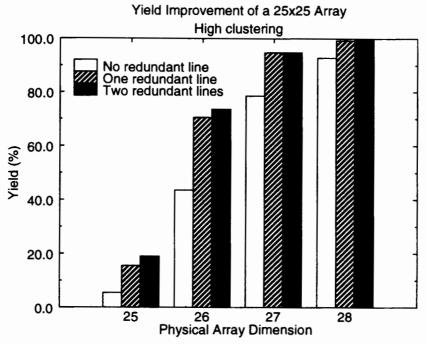

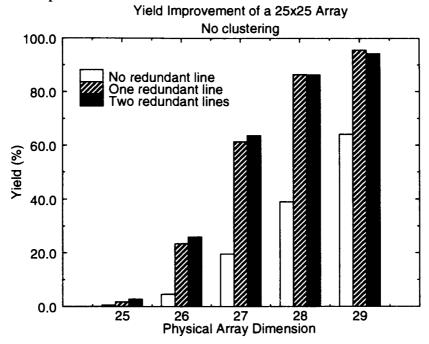

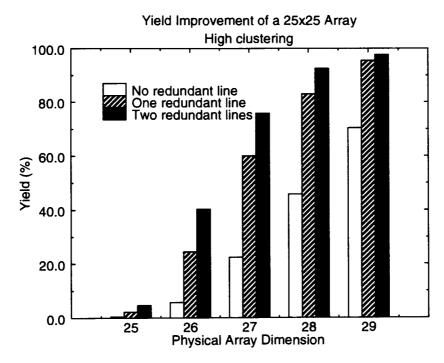

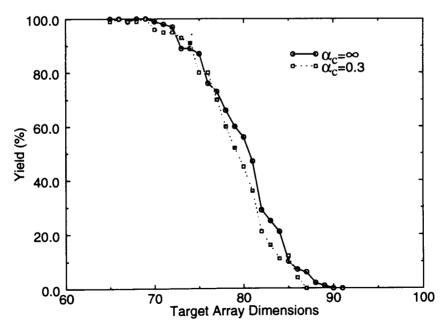

| Figure 4.7: Yield Results for a Logical 25x25 Array, no clustering ( $\lambda$ =0.005) 46   |

| Figure 4.8: Yield Results for a Logical 25x25 Array, high clustering ( $\lambda$ =0.005) 47 |

| Figure 4.9: Yield Results for a Logical 25x25 Array, no clustering ( $\lambda$ =0.01)       |

| Figure 4.10: Yield Results for a Logical 25x25 Array, high clustering ( $\lambda$ =0.01) 48 |

| Figure 4.11: Gupta Algorithm Restructuring example                                          |

| Figure 4.12: Cell by Cell Restructuring Example                                             |

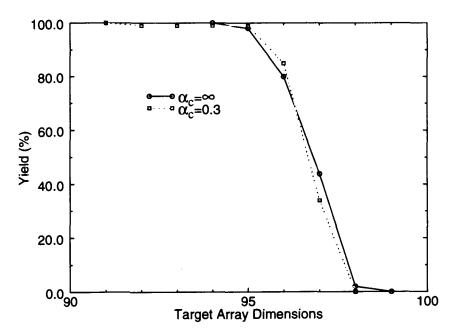

| Figure 4.13: Cell by Cell Restructuring Simulation,                                         |

| no extra line, $\lambda$ =0.01 (100 defects/wafer)                                          |

| Figure 4.14: Cell by Cell Restructuring Simulation,                                         |

| one extra line, $\lambda$ =0.01 (100 defects/wafer)                                         |

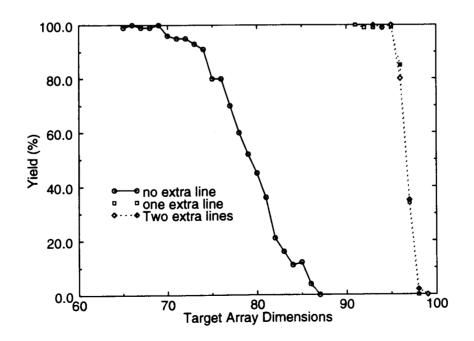

| Figure 4.15: Effect of Extra Lines, $\lambda$ =0.01 (100 defects/wafer), $\alpha_c$ =0.3    |

| Figure 4.16: Cell by Cell Restructuring Simulation,                                         |

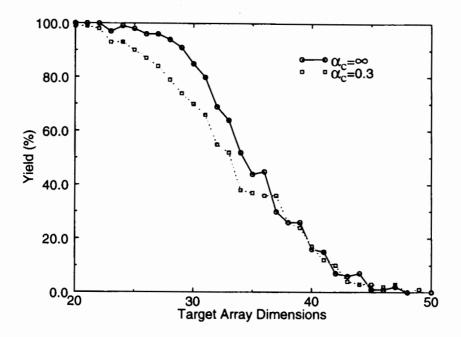

| no extra line, $\lambda$ =0.06 (600 defects/wafer)                                          |

| Figure 4.17: Cell by Cell Restructuring Simulation,                                         |

| one extra line, $\lambda$ =0.06 (600 defects/wafer)                                         |

| Figure 4.18: Effect of Extra Lines, $\lambda$ =0.06 (600 defects/wafer), $\alpha_c$ =0.3    |

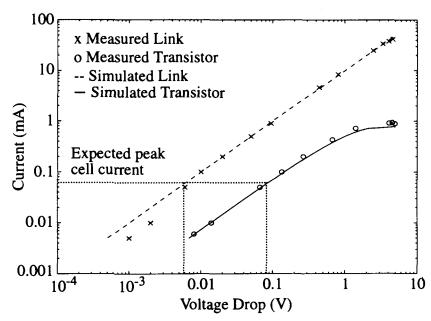

| Figure 4.19: Testable Laser Link                                                            |

| Figure 4.20: Graph of the Voltage Drop across the Testable Power Link                       |

| Figure 4.21: H-tree Clock Network                                                           |

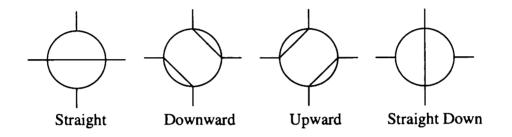

| Figure 4.22: Routing Switch                                                                 |

| Figure 4.23: Laser Pass Transistor                                                          |

| Figure 4.24: Reconfigurable Routing Switch                                                  |

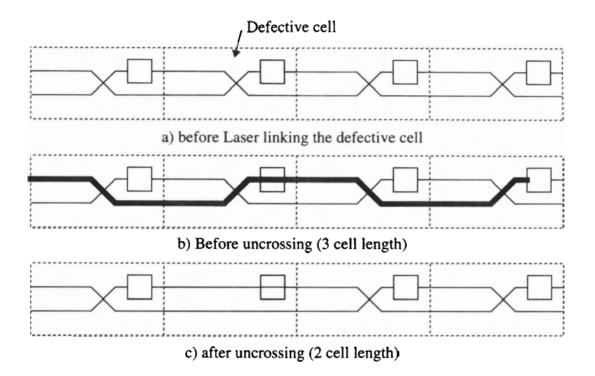

| Figure 4.25: Double Length Line Uncrossing Example                               |

|----------------------------------------------------------------------------------|

| Figure 4.26: Laser Links Arrangement to Uncross the Lines                        |

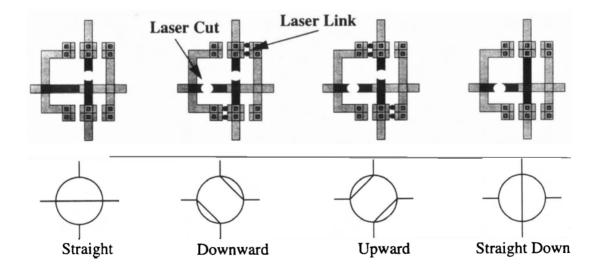

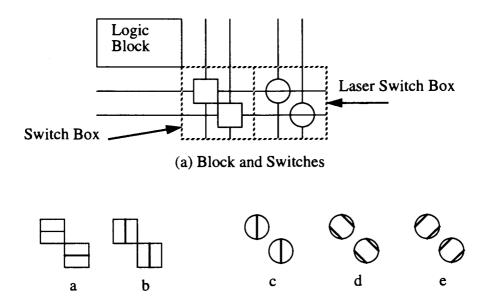

| Figure 4.27: Possible Laser Switch Configurations                                |

| Figure 4.28: Physical Design                                                     |

| Figure 4.29: Example of Defect Avoidance (darker Logic Blocks are defective) 66  |

| Figure 4.30: Laser Switch                                                        |

| Figure 4.31: Possible Switch Configurations, with Linking and Cutting            |

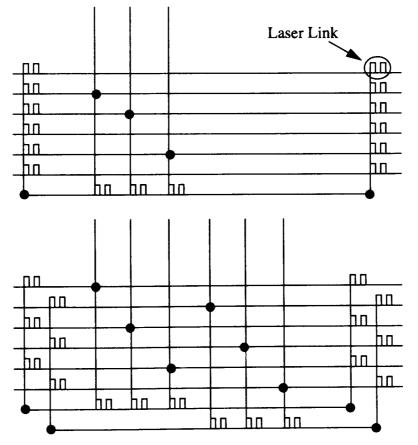

| Figure 4.32: Line Redundancy. Top: one extra line;                               |

| Bottom: two dedicated extra lines                                                |

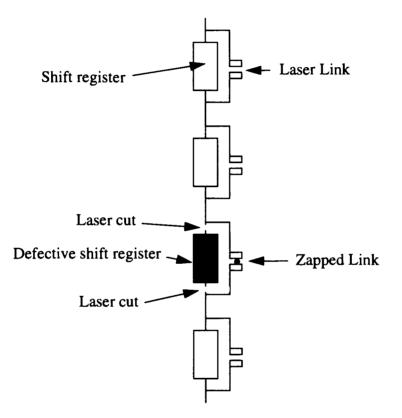

| Figure 4.33: Shift Register Bypass 69                                            |

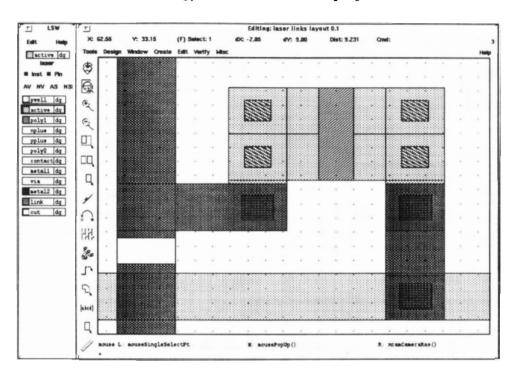

| Figure 4.34: Implementation of the Link and Cut Layers in Cadence                |

| Figure 4.35: Restructuring Patterns                                              |

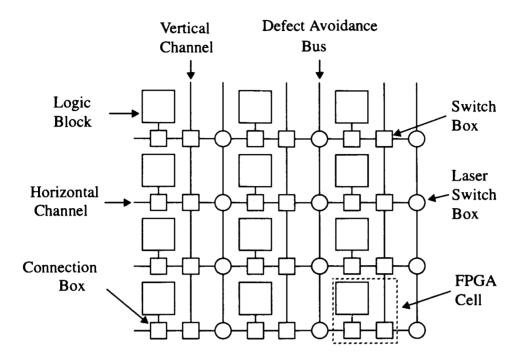

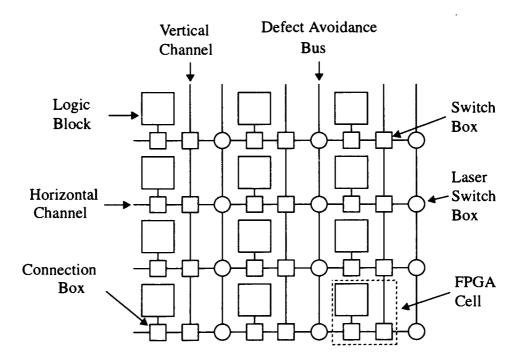

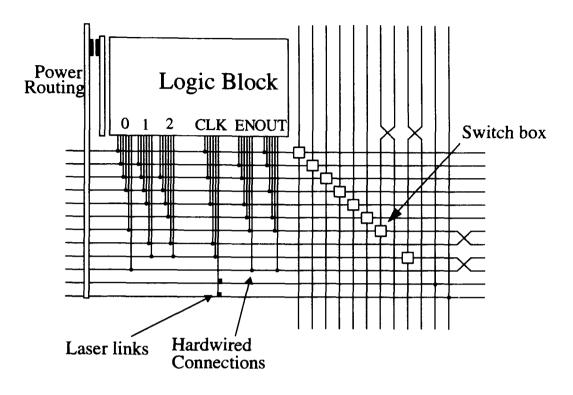

| Figure 5.1: Symmetrical Restructurable Architecture                              |

| Figure 5.2: Schematic of the Shift Register Bit Cell                             |

| Figure 5.3: Logic Block (LUT: Look Up Table; D: D Flip-flop)                     |

| Figure 5.4: Look-up Table Schematic                                              |

| Figure 5.5: Connection Box Diagram                                               |

| Figure 5.6: Block Diagram of the FPGA Cell                                       |

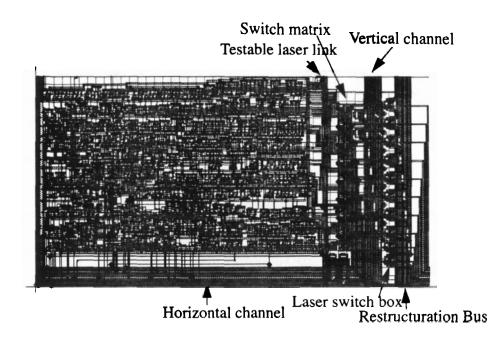

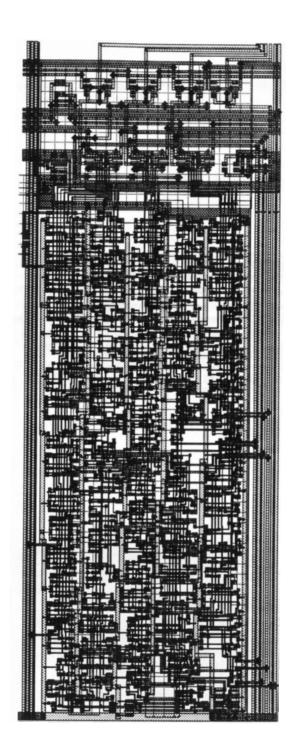

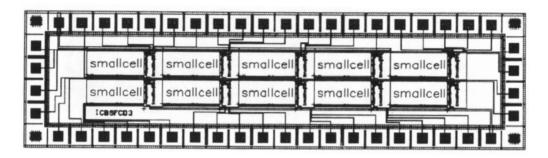

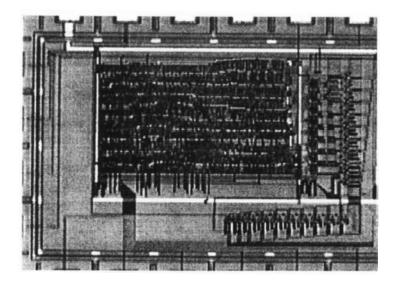

| Figure 5.7: Circuit Layout of the FPGA Cell in Mitel 1.5µm (1206µm x 650µm) . 82 |

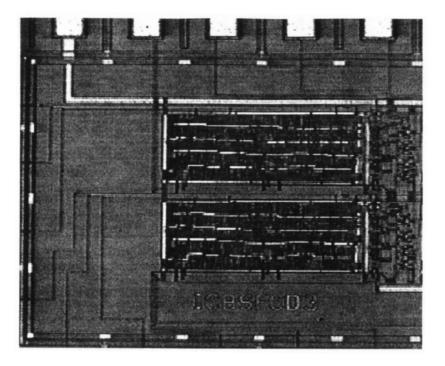

| Figure 5.8: Layout of the Smaller Cell in Mitel 1.5µm (834µm x 333µm)            |

| Figure 5.9: Circuit Layout of the Large Chip (ICBSFCD4) 1.5cm x 1.5mm            |

| Figure 5.10: Circuit Layout of the Small Chip (ICBSFCD3) 6.2mm x 1.5mm 84        |

| Figure 5.11: Photograph of the Large Cell Layout (1206µm x 650µm)                |

| Figure 5.12: Photograph of the Small Cell Layout (834µm x 333µm) 85              |

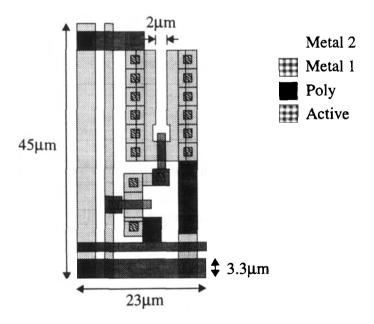

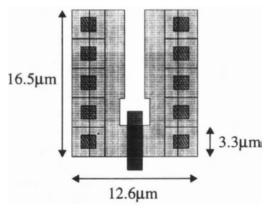

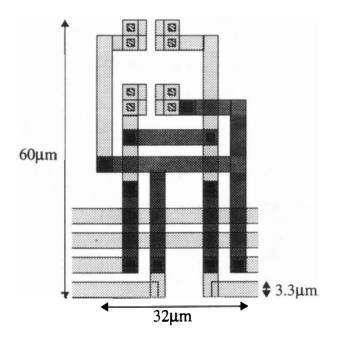

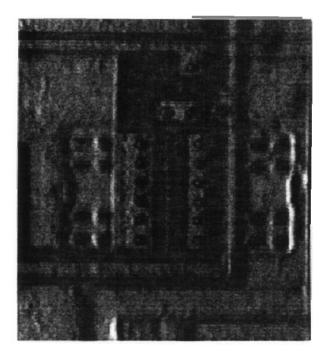

| Figure 5.13: Power Testable Link Photograph (45µm x 23µm)                |

|--------------------------------------------------------------------------|

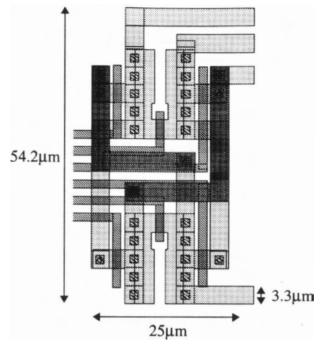

| Figure 5.14: Reconfigurable Switch Photograph (54.2µm x 25µm)            |

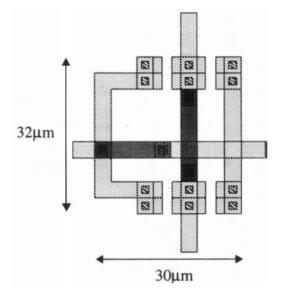

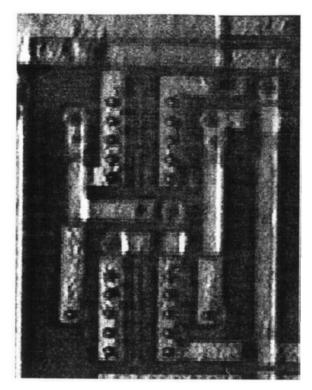

| Figure 5.15: Laser Switch Photograph (32µm x 30µm)                       |

| Figure 5.16: Line Uncrossing Structure Photograph (60µm x 32µm)          |

| Figure 5.17: Logic Block Delay Circuit (the numbers are spice nodes)     |

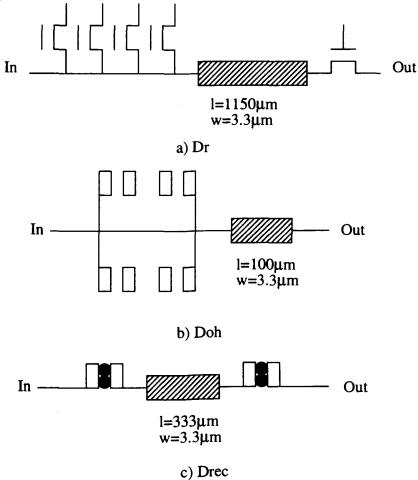

| Figure 5.18: Circuits used for Delay Simulations: a) Dr, routing delay;  |

| b) Doh, overhead delay; c) Drec, restructuring delay                     |

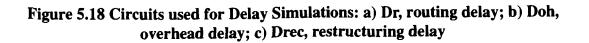

| Figure 5.19: Graph of the Delay vs. Yield for a Row of ten Working Cells |

| Figure 5.20: XOR Experiment Setup                                            | 96  |

|------------------------------------------------------------------------------|-----|

| Figure 5.21: Laser Link Paths                                                | 97  |

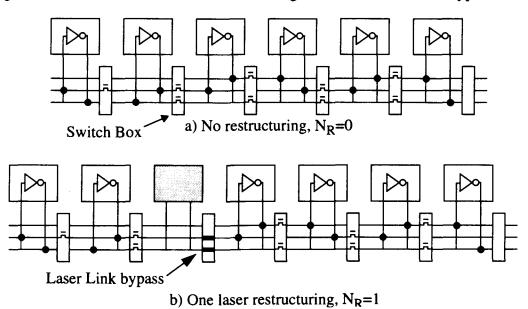

| Figure 5.22: Restructuring Experiment                                        | 98  |

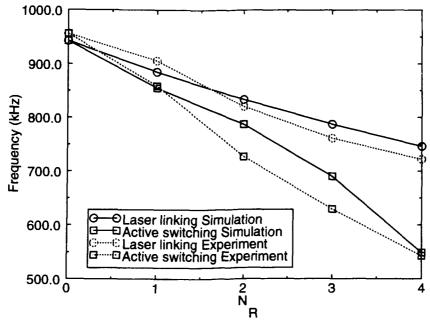

| Figure 5.23: Restructuring Experiment, Small Chip (ICBSFCD3)                 | 101 |

| Figure 5.24: Ring Oscillator Test, Small Chip (ICBSFCD3)                     | 102 |

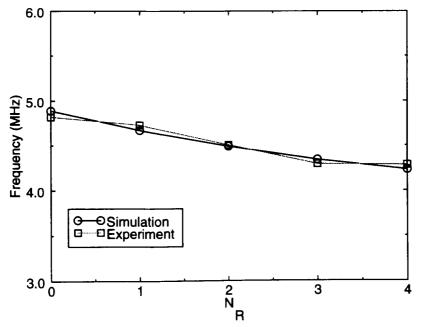

| Figure 5.25: Ring Oscillator Restructuring Experiment, Large Chip (ICBSFCD4) | 103 |

| Figure 5.26: Ring Oscillator Test, Large Chip (ICBSFCD4)                     | 105 |

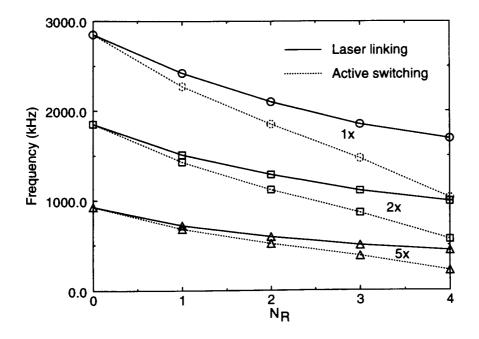

| Figure 5.27: Larger Cells Comparison, Active Switching and Laser Linking     | 106 |

## **List of Tables**

| Table 3.1: Resistance of one Zap (Mitel 1.5µm link)                 |   |

|---------------------------------------------------------------------|---|

| Table 4.1: Distribution of Wafer Lots; target $\lambda=0.1$         |   |

| Table 4.2: Row Column Algorithm C-like Pseudo-code       45         |   |

| Table 4.3: Cell by Cell Substitution C-like Pseudo-code       50    |   |

| Table 5.1: Power Test Results    88                                 |   |

| Table 5.2: Simulated Delays                                         |   |

| Table 5.3: The XOR Gate                                             |   |

| Table 5.4: Resistance and Delay of the Laser Linked Paths       98  |   |

| Table 5.5: Resistance and Delay of the Active Switch Paths       99 |   |

| Table 5.6: Double Length Paths Uncrossing Results         100       | ) |

| Table 5.7: Hspice Simulation and Experiments                        |   |

| for the Ring Oscillator, Small Chip (ICBSFCD3) 102                  | • |

| Table 5.8: Results for the Ring Oscillator,                         |   |

| Active Switching, Large Chip (ICBSFCD4) 104                         | ŀ |

| Table 5.9: Results for the Ring Oscillator,                         |   |

| Laser Linking, Large Chip (ICBSFCD4) 104                            | ŀ |

| Table 5.10: Larger Cells Comparison, Frequency in kHz 106           | 5 |

# Chapter 1

## Introduction

### **1.1 General**

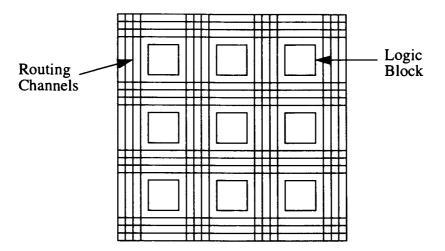

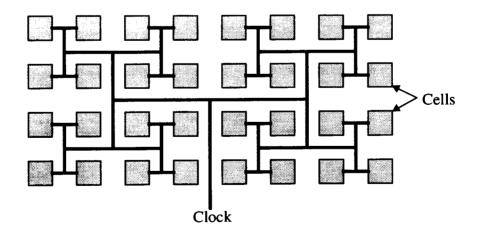

Field Programmable Gate Arrays (FPGAs) have progressed rapidly since their introduction in 1985, and are now widely employed by designers, especially as a cheap and fast means to implement new designs. An FPGA is basically an array of uncommitted programmable logic blocks that can perform different digital functions. Those blocks can be interconnected in different ways by use of a programmable routing structure. Figure 1.1 gives a block diagram of a typical FPGA. With their very low development cost and turnaround time for implementing thousands of logic gates, FPGAs provide a new capability which has changed the future of digital design. The largest FPGAs have an equivalent gate count of approximately 40,000 gates [1]. With the large amount of routing involved in an FPGA design, however, usually around 70%-90% [2], it is difficult to increase the cell count and, therefore, the design complexity of a single chip. Large FPGAs are also very expensive, mainly because of their low yields. One way to increase the gate count of a single FPGA is to use a denser technology, but still the amount of routing is an obstacle to very high gate count FPGAs. Arrays of FPGA chips on a board are used as a prototype platform [3], however the delay between the chips remains large compared to the delay within the chip.

**Figure 1.1 FPGA Block Diagram**

While seldom considered, one way to increase the gate count of FPGAs is to employ the technique known as Wafer Scale Integration. The chip size of a standard design must be kept small in order to achieve reasonable yield, because of the defects inherent in any microelectronic fabrication process. One way to counter this problem is to use redundancy and defect avoidance. By harvesting and using only the working parts of a circuit, it is possible to increase the size of a chip, ultimately to an entire wafer.

The restructuring technique employed at Simon Fraser University (SFU) is the laser link technology, developed at MIT Lincoln Laboratory [4]. By using the power of a laser, connections can be made between two metal layers of a microelectronic process and the same laser may serve to cut lines, allowing the restructuring of the design.

This thesis investigates the use of this technique to produce FPGAs of large area

and very high gate count. The idea of a wafer scale FPGA has already been proposed in another paper [5]. A different approach is proposed where the defect avoidance is invisible to the user. The focus of this thesis is to solve the interconnection and defect avoidance aspects of wafer scale systems. The FPGA cells employed are simple structures which would be replaced by more complex cells in a full system. Reasonable estimates indicate that in a final system, with a  $0.5\mu$ m CMOS technology, it would be possible to implement an FPGA of approximately 1.5 million equivalent gates on a 150mm wafer, and close to 3 million on a 200mm wafer, given a yield of 75% for the cells. The same restructuring technique can also serve to build smaller FPGAs, in the order of 120 000 equivalent gates with an approximate size of 3cm x 3cm.

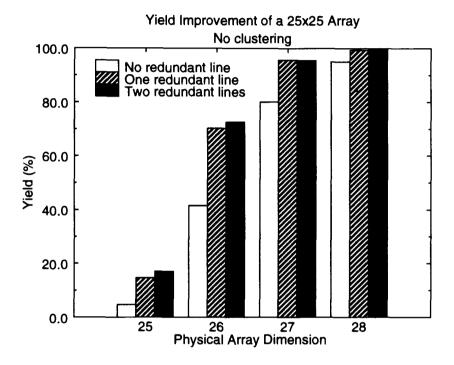

The restructuring can also serve to increase the yield of standard FPGAs, by providing one or two extra rows in case there is a defect, in the same way dynamic RAM chips are reconfigured today. Without increasing the gate count, this technique would be useful to reduce dramatically the cost of large FPGAs as in the case of RAM, where the number of working chips is increased by a factor of 5 with laser restructuring [12], and also provide a means to produce devices of larger areas.

FPGA designs are very well appropriated to wafer scale implementation. First, since FPGAs are arrays of identical cells, they are easier to test and reconfigure than large custom circuits; secondly, the FPGA being a reconfigurable system in itself, some of the reconfiguration circuitry is already available in the standard design and less overhead is needed to allow for reconfiguration. Finally, there is a very good potential market for large FPGAs, much better than other wafer scale projects which are very specialized.

3

### **1.2 Applications**

The first application that comes to mind for a wafer scale FPGA is a prototype emulator. With their current capacities, standard devices are limited in the designs they can implement. Very large devices, such as microprocessors, require a very high gate count and therefore very complex and expensive emulators. A wafer scale FPGA would provide a cheaper and faster way to simulate those very large designs.

Another interesting application is for self healing circuits. Not only the circuit but also the testing and reconfiguration circuitry could be implemented on the same FPGA. This could prove very useful in hard to reach areas or in applications where the hardware has to be fault tolerant. FPGA is the technology of choice for a new type of computers where instead of programming instructions in a standard hardware, the hardware itself is reconfigured to suit the computing requirements. Once again, very large FPGAs would be very useful and perform better than a large number of small FPGAs.

An interesting alternative is to use the defect avoidance techniques of the large systems and apply them to moderate size FPGAs to allow much better yield. This technique is already used in all the dynamic memory chip and could greatly reduce the price of actual high-end FPGAs.

## **1.3 Thesis Objectives**

The main objective of this thesis is to show that it is possible to apply the different techniques of Wafer Scale Integration to an FPGA design. Those techniques include power considerations, redundancy, restructuring, testing and clock distribution. A new kind of device to facilitate power testing and distribution is also presented. Different defect avoidance techniques are analyzed and simulated to find the best way to restructure FPGAs. Different types of redundancy are also analyzed.

The object of the work is not to build a complete wafer scale system, but rather to solve the problems of wafer scale on smaller dimension devices that are easier to work with and less expensive. Once the problems have been solved on the smaller devices, the increase in size should be relatively straightforward.

The work presented concentrates on designing a test vehicle to prove the concepts and apply them to a wafer scale design. There is a section describing the software requirements of a wafer scale FPGA but no extensive work has been done in this area. No attempts to optimize the logic nor the routing of FPGAs has been done. Instead, the restructuring method developed is general and can be used on different FPGA technologies and thus can be optimized by using state of the art logic and routing.

### **1.4 Thesis Organization**

Chapter two is a theoretical review of both the Wafer Scale and the FPGA technologies. A description of the concepts essential to the understanding of large area FPGA systems is presented.

In chapter three, experiments on the laser link restructuring technique in the Mitel 1.5µm technology are presented. Work done during the early part of the master on another wafer scale test vehicle, the thermal scene simulator, are discussed, with an emphasis on the experimental work done with the chips.

Chapter four addresses the concepts of defect avoidance in FPGAs. Simulations performed to find the best restructuring method are analyzed. The design considerations involved with building a wafer scale FPGA are studied. The chapter ends with an

5

overview of the software needed once a wafer scale system is build, both for testing of the hardware and programming of the device.

Chapter five emphasizes on the experimental work done on the test vehicle. The design is presented with each part explained in detail and the experiments on the defect avoidance methods exposed. The power distribution and the new device called the Testable Power Link are tested and their performance analyzed. The clock time delay, a critical parameter for FPGA users, is studied in detail and comparisons between HSPICE simulation and the experiments are shown. A ring oscillator was mapped on the test vehicle and its performance for different types of restructuring is presented.

The last chapter concludes by analyzing the feasibility, both technical and economical, of the Wafer Scale FPGA. A section on future work is also presented.

## **Chapter 2**

## **Theory of Wafer Scale Integration and Field Programmable Gate Arrays**

This chapter deals with the theory background used in conceiving a wafer scale field programmable gate array. The first section treats of the wafer scale integration technology in general. The second section deals with the theory of the FPGAS, their applications and the commercially available products.

### 2.1 Wafer Scale Integration

The main limitation of microelectronic fabrication is presence of production defects in the circuits. Only one defect on a chip makes it impossible to use. As the technologies get more mature, the defect density decreases but the chips must be kept relatively small to ensure sufficient yield. To build a large area chip is virtually impossible if there is no way to avoid the defects in the circuit.

The process of building large chips with the capacity to avoid defective areas is called Wafer Scale Integration [6]. The basic idea is that instead of fabricating small chips and retaining only those without defects, a very large chip can be built if there is a way to bypass the circuitry affected by defective areas. One way to do this is to use redundancy: when a defective cell is identified, a spare cell is used to replace it. The challenge is to build a circuitry to perform the reconfiguration. This circuitry must be as small as possible and have very little influence on the operation of the rest of the circuit.

So it is possible with this technique to increase significantly the size of microelectronic circuits. Because of the large amount of transistors on such a large device, the technology of choice is CMOS, due to its low power dissipation. But power still remains an important issue of wafer scale integration. The distribution of the signal throughout a very large device also becomes an issue, especially for the power rails and the clock lines. Testing of the different parts of the circuits may also become a problem and a circuit allowing the testing of hard to reach cells must be designed. Defect avoidance algorithms must be designed to make the best use of the area and maximize the speed of the circuits. Those are all aspects that the wafer scale designer must take into account.

There are two different approaches for the reconfiguration circuitry: active switches and permanent switches [6].

#### 2.1.1 Active Switches

Active switches are basically pass transistors or transmission gates. The signals to different parts of the circuit can be rerouted by programming those switches. They have the advantage to be easily programmable and reconfigured many times. They have however many drawbacks. First, they use more space than permanent switches, especially the programming circuitry [7]; they are also more resistive, thus imposing a longer delay

on the lines. Because of their large area overhead, they are also more sensitive to defects, and the switches themselves can be defective, making the circuit impossible to reconfigure.

#### 2.1.2 Permanent Switches

Under this classification are different types of switches, such as EPROMs, EEPROMs, Laser Programmable Switches and Anti-Fuses. They all have the drawback that they are programmable only once (except EEPROMs). But they require less area and they offer much better electrical characteristics than active switching. Permanent switches are well suited for defect avoidance because once the defects are known, the circuit is reconfigured only once. But they do not allow the possibility of self healing. They are also much better candidates for the power distribution circuitry, since smaller resistances can be achieved with permanent switches.

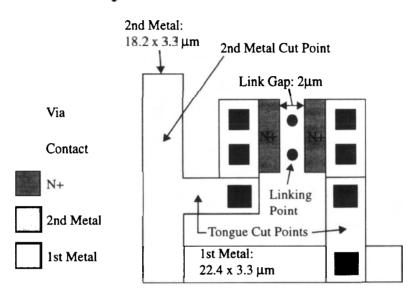

#### 2.1.3 Laser Link

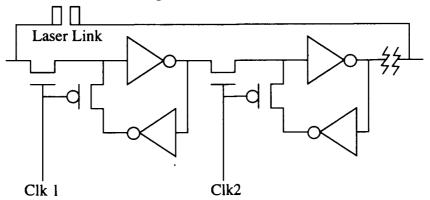

The type of switch used here at SFU is called the Laser Link and has been developed at MIT Lincoln Laboratories in the mid-eighties as part of the Restructurable VLSI program [4]. The idea is to employ the power of a laser to make connections between two metal layers. To this effect, a special structure called the Laser Link is needed. It is basically a gateless transistor (see Figure 2.1). In unconnected form the laser link has the high impedance of two back to back diodes. A connection is formed by an Argon laser focused in the gap between the implant regions. By melting the silicon in the gap with a 2 W, 50 $\mu$ s laser pulse focused to 1.2  $\mu$ m radius spot between the two heavily doped regions, the dopant flows across the gap, forming a low resistance connection (~100 $\Omega$ ) between the two metal lines. Typically two such "zap" points are made per link.

The main advantage of this type of structure is that it can be implemented in standard CMOS technology since it does not require any additional steps or materials. Of course it requires the use of a laser table that can be precisely aligned to allow the laser spot to be focused between the active regions.

Figure 2.1 Mitel 1.5µm CMOS Laser Link

To successfully reconfigure a design, cuts are made to disconnect certain lines in the circuit. This is done by shining the laser on top of the metal line and melting it. To start a design, it is necessary to know the different parameters such as laser power and pulse duration in order to make a suitable connection in a given technology. The next chapter explains the experimental procedure used to extract those parameters for the Mitel  $1.5\mu m$ CMOS technology and gives an example of a wafer scale circuit experiment done here at SFU.

### 2.2 Field Programmable Gate Arrays

With current technology, it is possible to build large custom designs at relatively low cost. However, because of the extensive manufacturing effort, the cost is high for each unit unless large volumes are produced. So it becomes really hard and expensive to build a prototype. Field Programmable Gate Arrays have emerged as the ultimate solution for low cost and fast turnaround prototyping. An FPGA based prototype can be manufactured in only minutes and their cost is in the order of \$100 for low gate counts [2]. This is the reason why FPGAs have evolved so rapidly from a tiny market four years ago to a very large business today. It is predicted that almost 1 billion dollars worth of FPGAs will be sold each year by 1996 [2].

#### 2.2.1 What is an FPGA?

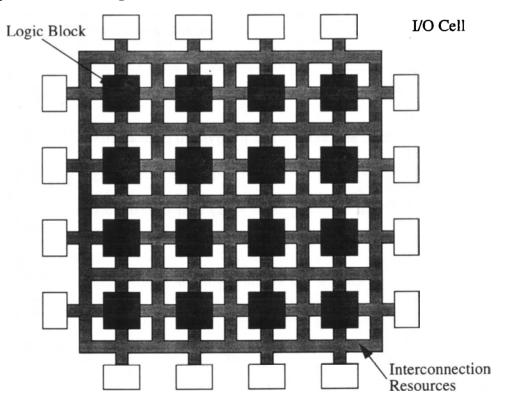

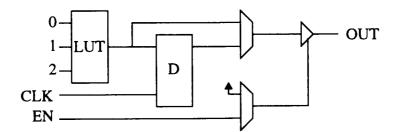

The Field Programmable Gate Array is basically an array of elements capable of performing logic functions that can be interconnected in a general way. Both the logic functions and the interconnections are user programmable. A general FPGA is composed of three parts, as seen in Figure 2.2.

Figure 2.2 Conceptual Simple FPGA

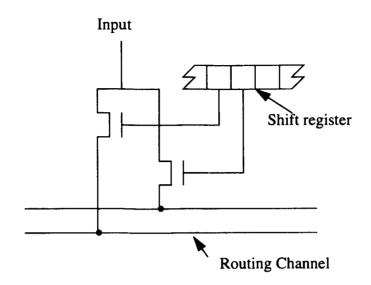

The Logic Block contains the logic to implement different functions. It can be as simple as a two-input nand gate or be quite complicated, such as look-up tables and flip-flops. The interconnection resources are composed of wire segments and programmable switches that allow the signals to propagate between the logic blocks and to go outside the chips via the I/O Cells. These cells are usually composed of multiplexers and buffers to connect the pads to the wire segments. There are several ways to program the logic functions and the switches to route the signal, including: RAM cells controlling pass transistors, anti-fuses, EPROM and EEPROM transistors.

#### **2.2.2 FPGA Architectures**

In this section, the different architectures used in FPGA design are presented, with some comments to their applicability to wafer scale designs.

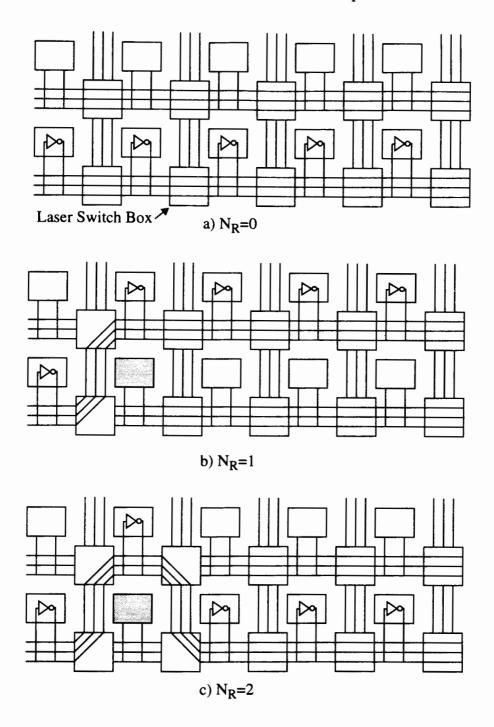

Symmetrical architecture: this is the most commonly used, where the logic blocks are surrounded by vertical and horizontal channels of routing. This is a very good architecture for wafer scale FPGA because it allows bypassing of single cells or entire rows.

*Row based architecture*: in this type of architecture, the logic blocks are organized in rows and the routing resources are disposed between the rows. This architecture is well suited for row reconfiguration but may cause some problems in reconfiguring very large designs.

Sea of gates architecture: the logic blocks are all side by side and the routing resources are placed on top of them. This causes some problems in most of the reconfiguration techniques and thus this architecture is not well suited for wafer scale applications.

Hierarchical PLDs architecture: this is an architecture where instead of having a

12

large number of simple logic blocks, there is a small number of programmable logic devices(PLDs), which are composed of different logic blocks. This could be an interesting architecture to explore for wafer scale integration: for example, memory cells consume many gates in some designs in a simple FPGA. Significant gains could be obtained by placing blocks of memory throughout the system. It is simpler however to have a repetition of the same cell for the reconfiguration.

#### 2.2.3 FPGA Applications

FPGAs can be used in all applications that can be performed now by other sorts of programmable logic devices. Their ability to be reconfigured on site also gives rise to new technologies. Here are some examples of FPGA applications:

Application-Specific Integrated Circuits (ASICs); being a completely general medium for digital logic implementation, FPGAs are particularly well suited for the design of ASICs. Some examples include controllers, graphics engines and many telecommunication applications.

Random logic implementation; since the FPGAs have a higher density than PALs (Programmable Array Logic), they are a good choice for implementing random logic in circuits where speed is not critical. One FPGA can replace ten to twenty PALs and perform the same function. FPGAs can also replace advantageously many SSI chips that require a lot of area on circuit boards, for "glue" logic.

Prototyping; FPGAs are almost ideal for prototyping applications. Their low cost and the extremely fast turnaround time they offer give them tremendous advantages over traditional prototyping methods. This is an area where a very large FPGA would be very useful, since the more gate equivalent an FPGA can offer, the larger the circuit it can implement.

13

FPGA-based Compute engines; this is an all new class of computers where instead of fetching instructions in a known hardware, it is the hardware itself which is actually reconfigured to perform the task. This increases the performance in the order of 100 times. Presently, boards of FPGAs are used for those kinds of computers; Wafer Scale FPGAs would increase the performance and capacity of such devices.

On site reconfiguration of hardware; this is particularly useful for applications that may require hardware reconfiguration and repair in hard to reach locations, such as satellites. Once again, many FPGAs could be replaced by a wafer scale design.

#### **2.2.4 Implementation Process**

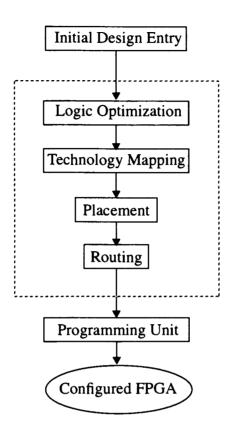

In order to successfully implement a circuit on an FPGA, an efficient CAD system must be used; this system must be able to perform the tasks shown in Figure 2.3.

The first step is to enter the design. This can be done by any schematic design tool, VHDL description or any acceptable format for the CAD tool. Then, the FPGA CAD tools have to perform the logic optimization, consisting of modifying the logic expressions either for speed or area density. The next step is to perform the technology mapping: it consists of dividing the circuit into logic functions that can be realized by the logic block of the FPGA used; for example, if the logic block used is a two input nand gate, the whole circuit has to be transformed into nand gates. Once again there are two ways to do this: either the mapper can optimize the number of logic blocks used or optimize the circuit for speed and use more logic blocks. The next step is Placement, where the logic blocks are placed to minimize the interconnection delays. Finally, the Routing, which assigns the wire segments and switches to connect the logic blocks together. The two final steps of the CAD tool may be iterative and it can be necessary to redo the placement if the router is unable to successfully route all the connections. These steps can also be repeated to optimize the design for speed.

**Figure 2.3 FPGA Implementation Process**

The last step in the implementation process is the Programming of the FPGA. It depends on the programming technology of the FPGA used. For a RAM programmable FPGA, only a bit pattern fetched out of a separate memory is sufficient. For other technologies, such as anti fuses or EPROMs, an appropriate programming unit must be used.

#### 2.2.5 Commercially Available FPGAs

Several combinations of architecture, logic block type and programming technologies are available on the market [2].

The most important is the Xilinx FPGA. The latest generation of Xilinx FPGAs

uses a RAM programmable symmetrical architecture with look-up table based logic blocks.

Actel offers a row-based design with anti-fuse programming and a multiplexer based logic block. Compared to Xilinx FPGAs, the Actel design has a smaller logic block.

Altera uses the hierarchical approach with EPROM programming while Plessey offers sea-of-nand-gates static RAM programmable FPGAs.

There are other companies that offer different types and technologies. The choice of an FPGA depends on the particular application and the speed needed. The CAD tools available should also be taken into account when choosing a type of FPGA to use. Each company offers its own software but a specific software must be used for each type of FPGA and the user can not make a separate choice between the hardware and the programming tool.

### **2.3 Summary**

The present chapter described the basics of Wafer Scale Integration and FPGAs. These are two very wide fields but only succinct information necessary to the understanding of the next chapters has been presented. The section on Wafer Scale Integration described the types of switches used and presented the type used here, the laser link. The section on FPGAs furnished explanations of the different architectures and presented designs that are commercially available.

# Chapter 3

## **Laser Linking Wafer Scale Integration**

This chapter presents experiments done to extract parameters for laser link devices using the Mitel technology as a wafer scale medium; the knowledge of those parameters is crucial before any design work can be undertaken. It furnishes also explanations of the experiments done on laser linking with the thermal pixel scene simulator, a wafer scale test vehicle developed here at SFU.

### 3.1 Mitel 1.5µm Technology Parameter Extraction

#### 3.1.1 Laser Table Setup

To make the laser links and cuts, a special setup is needed. The first part of this setup is the laser. The laser used here at SFU is a 5.0 W Argon laser. Because of the very small dimensions of today's microelectronic structures, a very precise table is needed to

correctly aligned the structure to be processed with the laser. The table uses laser interferometry to allow a 0.1  $\mu$ m precision in both the horizontal and vertical axes. In order to correctly melt the silicon, a short duration (approximately 100 $\mu$ s) laser pulse is needed. This is achieved by passing the laser beam through an electro-optic shutter. A z-axis micropositioner is also used for the remote focusing of the chip. All the equipment is controlled via a Windows based software developed here at SFU. This software can be used to zap single points or a script file can be used to do batch work. A photograph of the laser table setup is shown in Figure 3.1.

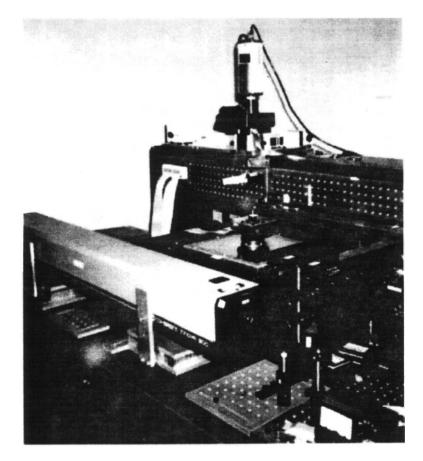

Figure 3.1 Laser Table Setup

#### 3.1.2 Laser Link Power Calculations

Figure 3.2 shows a cross section view of the laser link in the Mitel technology. This

is in fact a simplified model used to calculate the power required to form the melt pool.

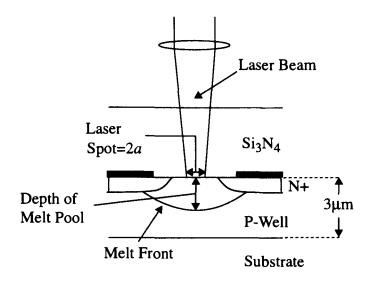

#### **Figure 3.2 Cross Section of the Linking Process**

First of all, the vertical temperature distribution from a focused laser spot can be approximated by using the formula ([8] page 171):

$$\Delta T = \frac{2H}{k} \sqrt{\alpha_T t} \left[ ierf\left(\frac{z}{2\sqrt{\alpha_T t}}\right) - ierf\left(\frac{\sqrt{z^2 + a^2}}{2\sqrt{\alpha_T t}}\right) \right]$$

(3.1)

Where H is the power density, t the time of the pulse, z the depth of penetration,  $\alpha_T$  the thermal diffusivity and *a* the radius of the pulse. This formula assumes a constant  $\alpha_T$  with temperature, which is not really true, but a useful first approximation.

For silicon ([8] page 174):

$$\alpha_T = 103 \cdot 10^{-6} \frac{m^2}{s}$$

$$k = 170 \frac{W}{m \cdot K}$$

$$T_m = 1680K$$

This formula also assumes the light is absorbed at the surface, which is a good

approximation as the green (514nm) Argon light is absorbed by a depth of about  $0.3\mu$ m. In order to calculate the power needed from the laser, the reflectivity at the silicon-silicon nitride interface must be calculated, by using:

$$R = \left(\frac{n_1 - n_2}{n_1 + n_2}\right)^2 \tag{3.2}$$

$n_{Si}=4.2$  and  $n_{Si3N4}=2$  [9], then R=0.126. The effect of the oxide between the silicon nitride and the silicon is neglected in the calculation. The reflection coefficient of the air-Si interface is also needed. This coefficient is R=0.11. The power absorbed by the Si<sub>3</sub>N<sub>4</sub> is given by the Beer-Lambert law ([10] page 165):

$$P(z) = P_0 e^{-2\alpha_l z}$$

(3.3)

Where  $\alpha_l$  is the light absorption coefficient for silicon nitride. For argon laser light (514nm),  $\alpha_l=300 \text{ m}^{-1}$  [11]. Thus the power density at the surface of the silicon is approximately:

$$H = \frac{P_0 e^{-2\alpha_l z}}{\pi a^2}$$

(3.4)

where P<sub>o</sub>=Laser power.

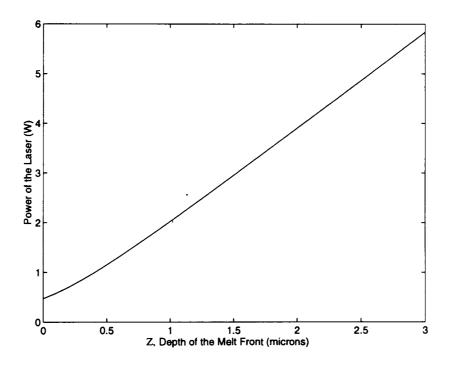

Instead of calculating one value only for a specific depth, a graph of the power required from the laser pulse in function of the depth of the melt pool is given in Figure 3.3. This is obtained by solving (3.1) for  $\Delta T$ =1680K, the silicon melting point, for laser power densities from (3.4) using the typical values for this research of:

$$z_{Si3N4} = 3\mu m \qquad t_{pulse} = 100\mu s \qquad a_{spot} = 0.5\mu m$$

The thickness of the passivation layer is an approximation since the real value is unknown.

The graph shows the power needed is in the order of 2.0 W to create a melt pool sufficient to allow the dopants to form a bridge between the two N+ regions, knowing the distance between the active region is  $2\mu m$  and assuming the melt front propagates with the same velocity in the vertical and horizontal directions. Experiments show this assumption is reasonable. The graph also tells that for a power of about 5.8 W, the melt front reaches the substrate below the P-well. Such a high power must be avoided because a connection to the substrate results in a non usable link.

Figure 3.3 Graph of the Power vs. Depth of the Melt Front

#### **3.1.3 Laser Power Experiments**

The first set of experiment was done to find the power required to have a low resistance connection between the active regions. Table 3.1 gives the obtained results. The time of the laser pulse is  $100 \ \mu$ s; the resistance of five separate connections was averaged.

After 2.5 W, the resistance starts to saturate. While the resistance is lower at 2.75W, the damage is greater and can break the vias of the laser link. The safest power to use is 2.50W. If the link is long enough, the laser can be zapped at two separate points to reduce the resistance of the connection.

| Power(W) | R (Ω) | σ    |

|----------|-------|------|

| 2.00     | 260.3 | 20.9 |

| 2.25     | 183.1 | 15.7 |

| 2.50     | 149.2 | 11.2 |

| 2.75     | 134.1 | 6.1  |

Table 3.1: Resistance of one Zap (Mitel 1.5µm link)

If the second zap is too close to the first one, or if the second zap is at the same location, there is no decrease in resistance. Experiment shows the spots should be at least 6µm apart to have a significant decrease in resistance. At 2.50 W, a second zap decreased the resistance of the link to  $109\pm 2\Omega$ . The experiments show the resistance of two zaps follows a curve vs. the power similar to the curve for the resistance of one zap.

#### **3.1.4 Laser Link Experiment**

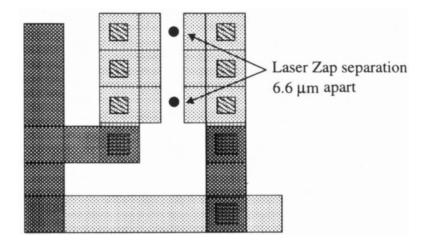

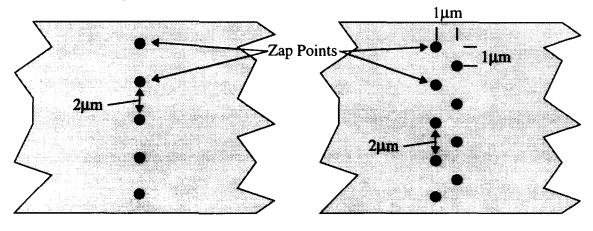

The next experiment consists in doing many links and test the resistance of each of them. The zapping pattern can be seen in Figure 3.4. The width of the active regions is 9.9  $\mu$ m and the gap between is 2 $\mu$ m (the minimum allowed separation in Mitel 1.5 $\mu$ m technology). The first zap is made 1.65  $\mu$ m from the top and the second at 6.6  $\mu$ m from the first zap. The laser power is 2.50W and the pulse duration is 100 $\mu$ s.

A third spot in the middle does not decrease the resistance and is thus useless. This is because the two melt pools created by the zaps are touching and no gain is made by adding an extra zap. The results for 10 links give  $R_{average} = 109\pm 5\Omega$ .

Figure 3.4 Position of the Laser Zaps

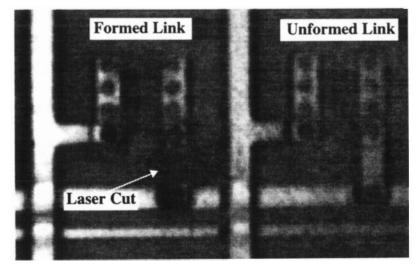

A rough rule of thumb to estimate the resistance of links can be deduced from experimental data: one zap produces a resistance of  $100\Omega$ ; a  $50\Omega$  constant resistance from the contact cuts to the N+ region and the implant region is added to the zap resistances. A two-zap link will have  $50\Omega + (100\Omega \parallel 100\Omega)$  giving a total of  $100\Omega$ . A three-zap link has a resistance of about  $83\Omega$ . This shows the third zap, which has little measurable effect, is not really creating an additional parallel resistive path. Figure 3.5 is a photograph of two laser links, the one on the left has been linked with the method explained above. The laser cut on a second metal line can also be seen.

Figure 3.5 Photograph of the Links

### **3.1.5 Laser Cut Experiments**

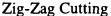

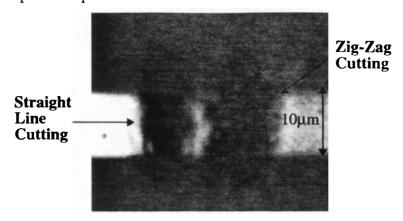

The power required to cut the aluminum lines must be found. Experiments show there is no problem in cutting the  $3.3\mu$ m width lines with a laser power higher than 2.5W, by zapping the line in the middle with a pulse of 100µs and a spot size of  $1.2\mu$ m FWHM (Full Width Half Maximum). Out of a total of approximately 100 cuts made this way, all of them showed a resistance higher than 10 M $\Omega$  So the best way seems to use the same parameters for the cuts and the links. This cutting behavior applies to metal1 and metal2 lines. In order to cut wider lines, such as power lines, a larger number of zaps is needed. The effect of each zap is reduced because of the greater loss of energy due to heat flow. Due to the lack of proper test structures, it was hard to evaluate if the large line was really cut, but by visual inspection, two cutting patterns were developed. They are shown in Figure 3.6 for a 10µm wide metal1 line.

Straight Line Cutting

### Figure 3.6 Two Methods for Cutting Large Metal Lines

The straight line method consists of a first zap at 1  $\mu$ m from the edge of the line and a zap each 2 $\mu$ m afterwards, until a distance of less than 1  $\mu$ m from the other edge is reached. In the Zig-Zag method, a first zap is made 1 $\mu$ m from the edge, then 1 $\mu$ m away in each direction. The Zig-Zag method seems more reliable (electrical test should be performed to confirm this) than the straight line method but takes a longer time due to the higher number of pulses required.

Figure 3.7 Photograph of the Cutting Methods

The time taken to cut a 10µm wide line is 4.27s for the straight line method and 13.45s for the Zig-Zag. The Zig-Zag method also takes up more space. The choice should be made in function of the time and the area available. Figure 3.7 is a photograph of the two methods; the larger area taken by the zig-zag method is clearly seen.

### 3.1.6 Damage to Silicon Nitride

Silicon nitride can be very sensitive to low intensities of laser light. It will fluoresce at about 10mW of power for a 1.2 $\mu$ m spot, and it has a low damage threshold that depends on the exact composition of the nitride. In the photographs, lots of damage surrounding the links and cuts can be seen. This is due to the behavior of the silicon nitride under the laser pulse. Such damage is not seen in the Northern Telecom 3 $\mu$ m process which uses glass instead of nitride. Figure 3.8 shows the radius of damage for different laser powers. The large damage at 4.5W is probably due to a defect present in the silicon nitride layer. Its diameter is close to 10 $\mu$ m. These defects can have a significant impact because the layer seems much more opaque when shot once with the laser and there is no or little effect when a pulse is applied on top of a damaged area. These damages increase the minimum spacing allowable between links and lines to cut.

Figure 3.8 Photograph of the Damage in the Silicon Nitride

### 3.1.7 Batch Linking and Cutting

In this section the behavior of many links and cuts done in parallel with a script file is discussed. First the chip has to be very well aligned, especially if the links or cuts are far apart on the table. Due to the 'wiggling' (side motion) effects of the z axis motor, the focus was not changed during the linking process. The results were as follows: for five links in parallel, the resistance was  $41.2\pm0.4 \ \Omega$  and the total time to do the connections was 10.58s. This gives an average link resistance of  $206\Omega$ . The individual links have a measured resistance of about  $100\Omega$  with this setup. This means the links have a slightly higher resistance when done in batch. An explanation is that the alignment is not as precise as when the links are done individually, therefore some of them, especially the last ones, show a higher resistance. The average time to do each link is 2.12 s, which is rather long. Faster control systems of the table will be needed for a very large number of links.

For the cuts, it took 3.7s to do 5 cuts of  $3.3\mu m$  wide lines in a row. The resistance was high,  $26M\Omega$ , proving the cutting was successful. The average time for each cut was 0.74s. The alignment seems less critical with the cuts. A different focus is used for cuts

and links. The difference is about  $3\mu$ m. To do batch linking and cutting with the same file, or over a large area, the focus has to be adjusted and therefore a Z axis controller which is very precise and stable is needed.

### 3.1.8 Linking Summary

The goal of these experiments was to extract the parameters needed to use the laser linking and cutting with the Mitel 1.5 $\mu$ m technology. Results have shown that the Mitel technology can be used efficiently for this purpose. With proper table settings and careful alignment, links resistances in the order of 100 $\Omega$  can be achieved. The cutting of thin lines (less than 3.3 $\mu$ m) seems very reliable, more than with other technologies used before, like the 3 $\mu$ m CMOS from Northern Telecom. The cutting of large lines seems to be efficient, but in this experiment only visual inspection was used because of the lack of test structures.

The links seem to be less reproducible and their resistance is influenced by the parameters. The minimum width of the links seems to be around 10 $\mu$ m if a resistance in the order of 100 $\Omega$  is wanted. This is because the distance between two zaps must be at least ~6 $\mu$ m to be effective. If a second zap is too close to the first one, there is no effect. A careful alignment of the electro-optic shutter is needed to achieve maximum throughput and effective use of the laser. The shutter's closed condition should block the light so there is no permanent effect on the chip when the table is moved.

The designer should be careful about the extension of the P-well on its design. Even if allowed by the DRC checker, the P-well should not extend less than  $3\mu m$  from a link. This is to avoid a connection to the substrate; such connections were seen in links closer than  $3\mu m$  from the P-well, but not in those at a greater distance. It is assumed these shorts occur because the P-well is shallower near its edge. In addition, the power of the laser has to be kept reasonable to avoid a vertical connection to the P-well.

One difficulty with the Mitel technology comes from the silicon nitride passivation layer. The laser produces large damage which can interfere with surrounding structures and block the laser for further processing. The designer should be aware of this and keep a reasonable distance between structures needing repair. The silicon nitride may become conductive when zapped with the laser and interconnection between metal 1 and 2 may be possible [12], although not encountered during these experiments.

The batch linking and cutting is reliable over a small area and by keeping the same focus. The speed is slow for linking, around 2 s per link, and it must be improved if a large number of links have to be made. A design with all the links aligned is faster to zap than a random pattern. The z axis has to be very stable if the focus has to be changed. In the current setup, there is an x and y movement when the focus is changed, causing a misalignment of the coordinates.

These experiments have shown linking and cutting is possible with the Mitel technology but improvements in the laser table control are needed for large batch jobs.

### **3.2 Practical Example: Test Vehicle for a Wafer Scale** Thermal Pixel Scene Simulator

This section describes the laser linking work done on a wafer scale test vehicle designed by M. J. Syrzycki, L. S. Carr, G. H. Chapman and M. Parameswaran: the Thermal Pixel Scene Simulator [13]. It combines micromachining and wafer scale restructuring techniques to build a large array of infrared emitters. The main purpose of this section is to present an example of the restructuring work done with the laser table on the laser links.

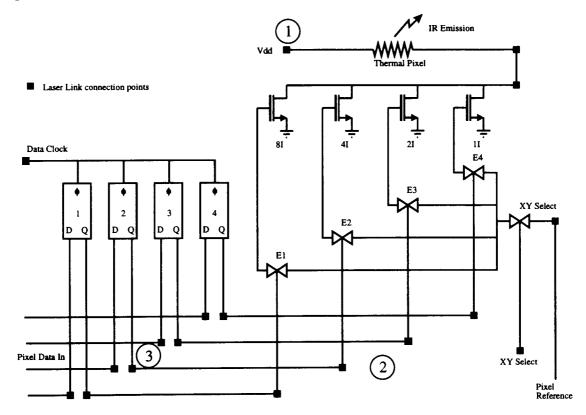

### 3.2.1 Design

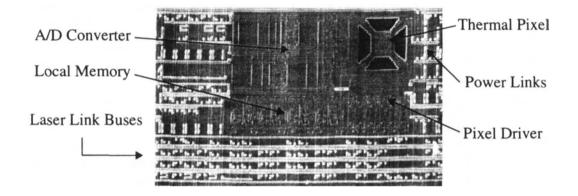

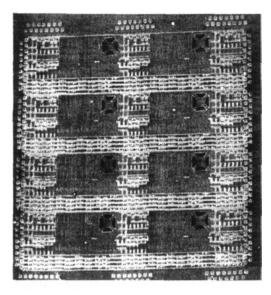

Figure 3.9 shows the layout of the basic transducer cell. On the upper right, the thermal pixel, a micromachined device that emits infrared radiation when a current is applied, can be seen. Beneath the device is a pixel driver, to control the current fed to the emitter. The local memory is used to store the value of the pixel. The A/D converter is used to convert the signal from the photodiode. This part of the design was not used during these experiments.

### Figure 3.9 SEM Photograph of the Transducer Cell (1260µm x 742µm)

Surrounding the basic circuitry are restructuring laser link buses. On the right, the large laser links are used to hook up the power to the cell and to drive the current in the thermal emitter. The other laser links serve to connect the different signals to the logic part of the design. The laser links are disposed in an alternate up and down fashion to provide a denser bus. The design was manufactured in Northern Telecom  $3\mu m$  CMOS. The photograph of the test chip is shown in Figure 3.10. The test chip is a 4x2 array of transducer cells with the laser link buses running across the entire chip.

Figure 3.10 SEM Photograph of the Test Chip (7mm x 7mm)

### **3.2.2 Experimental Procedure**

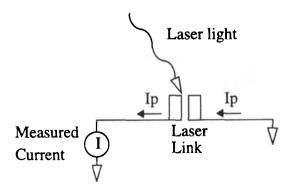

When first powered up, the power rails are disconnected and there is no power consumption. Before making the connection to the power rails, and before any laser link is connected, optical probing [14] is performed. By shining the laser at low power ( $\sim$ 3mW) at the junction between the substrate and the active region, electron-hole pairs are created that generate a small photocurrent (around 30µA) between the substrate and the line connected to the link. By measuring the photocurrent, the path resistance can be measured and the signal route verified. This is shown in Figure 3.11.

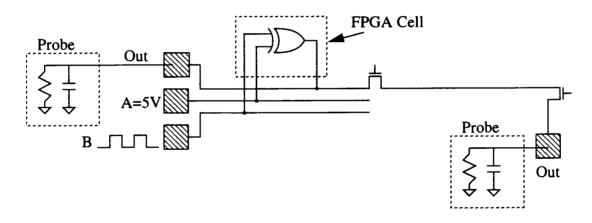

**Figure 3.11 Optical Probing**

The first step is to connect the power to the cell (Step 1 in Figure 3.12). When done, the power consumption is measured. If the current draw is normal, the interconnection of the signal lines can begin. If there is a high power surge, indicating a short in the cell circuitry, the cell is disconnected. The first step in interconnecting the signal buses is to connect the four signal lines to the driver circuitry and test its operation (Step 2). If this is successful, the hook-up of the latches can be performed (Step 3). To do this, the line to the driver circuit is cut and by connecting two laser links, the cut is bypassed and the signal redirected into a D flip-flop. The final test to the cell is then performed and consists in being able to drive the pixel with a four bit memory, resulting in 16 possible current draws. Typical cell interconnections required 19 links and 5 cuts.

**Figure 3.12 Design Schematic**

### **3.2.3 Experimental Results**

Two types of chips were tested. The first one was tested as fabricated while the other one was anisotropically etched to form a suspended plate holding the pixel. The parameters for the laser links and cuts were extracted the same way as explained in the previous section for the Mitel technology. There was no difference found in the parameters for both chips. The typical resistance for the standard laser link was  $75\Omega$  while the wider power links showed a  $25\Omega$  resistance. The first test chip, which was unetched, had seven operating pixels, six of which were latched. The etched chip was fully functional, each one of the eight pixels working with the latching circuitry [15].

This work, performed early in the master program, was very useful in learning the basics of wafer scale integration and also to learn how to use the laser table system. Many of the concepts were later used in the design and test of the FPGA vehicle.

### 3.3 Summary

This chapter has described the experimental work done with the laser linking wafer scale technology. In the first section, the experimental procedure to extract the linking and cutting parameters was presented while the second section dealt with the work done on another type of test vehicle, the wafer scale thermal pixel scene simulator.

The experiments described above provided useful insights and necessary results in the elaboration of the FPGA test vehicle.

## **Chapter 4**

# **Defect Avoidance in FPGAs**

The key in building a working Wafer Scale field programmable gate array is to design a system to eliminate the different types of defects present on the wafer after fabrication. In this chapter, there is a brief introduction of the types of defects and faults they create. Thereafter a summary of different defect avoidance techniques will be presented and the requirements for restructuring an FPGA will be investigated.

The following section concerns restructuring algorithms and their effects on the harvest of good cells. Simulations are made to test the performance of the algorithms and the architectures. An other section concerns the design requirements for building a wafer scale FPGA while the last section is an overview of the different tools needed to program a large FPGA and how they differ from the commercially available software.

### **4.1 Defect Avoidance**

This section treats of the general defect avoidance techniques and how they can be applied to FPGA restructuring. In all these cases only one type of FPGA cell throughout the wafer is assumed.

### **4.1.1 Fabrication Defects**

There are numerous defect mechanisms in any microelectronic process. The goal of this section is not to explain every type of defects but rather to classify the faults they create to find a proper way to avoid them. Figure 4.1 shows an example of the major categories.

Figure 4.1 Three Categories of Defects: a) Logic Defect: e.g. Gate Oxide Hole; b) Power Defect: e.g. Power Short; c) Routing Defect: e.g. Bus Open Circuit and Bus Short

Logic Defects: all the defects affecting the logic operation of a circuit are grouped under this category. Those defects can be of many types, such as misalignment, pinhole defects, shorts or open circuits; their effect is localized, however, and affects only the logic operation of a certain part of the circuit.

Power Defects: these types of defects can be caused by many defect mechanisms, but the most common outcome is the power bus metal to metal short. This is the most critical kind of defect because if it is not taken into account in the design, just one of these defects can kill an entire wafer even before tests can be performed. For this purpose a special defect avoidance scheme must be employed for this category of defects.

Routing Defects: this category includes all the defects that affect the buses on the wafer, either the signal buses or the reconfiguration buses. They can be very deadly if they are not taken into account because the reconfiguration circuitry can be inoperative, killing the entire wafer.

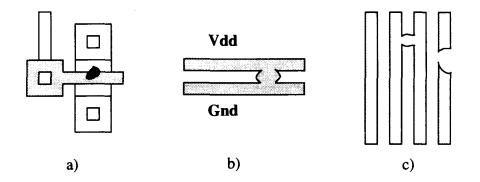

### 4.1.2 General Defect Avoidance

Defect avoidance is defined as the different ways to avoid defective parts of a circuit and provide means to employ the working parts to build a larger circuit than achievable with standard microelectronics. One way to obtain this is to divide the circuit into identical parts. They can be rows, running from side to side of the wafer, or they can be cells, a small part of circuitry that can perform a certain function. Defect avoidance is realized by providing spares that can be connected instead of the defective cells or rows. This is called redundancy. The level of redundancy depends on the density of the defects and the desired yield. There are two classes of redundancy: global and local sparing. In global sparing, a spare can replace any of the cells in the circuit; this is very versatile but can lead to long delays if the spare cell is situated far away. There are also some applications where the physical placement of the cell is critical, like large sensor or transducer arrays. The kind of redundancy used then is called local sparing [16], where the spares are physically close to the original cell. Figure 4.2 gives an example of the two redundancy classes. Figure 4.2 a) shows an example of a spare column of cells where the spares are used to replace two defective cells to form a 6x6 array of working cells. In Figure 4.2 b), local sparing is used to produce an array of 3x3 cells. The dashed line encloses the cell and its spares. Only one out of those four cells needs to be working.

Figure 4.2 Two Redundancy Classes: a) Global Sparing; b) Local Sparing

For FPGAs, the physical placement of the cells is not critical because all cells are identical. The spare cell, however, must be close to the defective cell in order to reduce the time delay between the cells. Local sparing is ideal for that purpose but requires very large overhead. The best way to restructure an array of cells is not to use dedicated spare cells, but rather build the array using the closest available cell as a spare. This means every cell in the array can be a spare.

#### 4.1.3 Making the Defect Avoidance Invisible to the User

The idea of a wafer scale FPGA has been proposed by others[5], but was presented with a different approach to defect avoidance. In this earlier paper, the defect avoidance is performed by the FPGA software itself, using the inherent reconfigurability of the FPGA circuitry. However, the FPGA software has to be aware of which cells in the array are defective to bypass them. It may also cause problems because the FPGA may become no longer symmetrical. Macro circuits already optimized cannot be used because of the defective cells breaking the array. This method is also not tolerant of certain faults such as power shorts. Although this method requires no overhead for restructuring, the above reasons make it hard to use.

The proposed wafer scale FPGA in this thesis does not use the electronic bypass capability of its routing architecture but rather physical restructuring switches. While this technique uses a minimum of overhead because of the small area occupied by the laser links, the major advantage of this method is to make the restructuring invisible to the user. The restructuring consists in harvesting a two dimensional array of working cells from an array containing defective cells and/or buses. By using different techniques, the array appears fault free and the actual map of the defects does not have to be known by the user when programming the FPGA.

The following section explains how to restructure such arrays to provide a restructuring invisible to the user.

### 4.2 Restructuring of a 2-D Array

Different restructuring techniques are presented. They all have the same goal, i.e. to build the largest 2-D array from a basic array containing defects. Advantages and drawbacks of these techniques are evaluated and their potential for building FPGAs discussed.

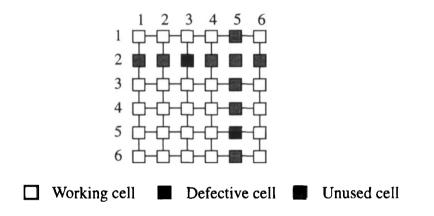

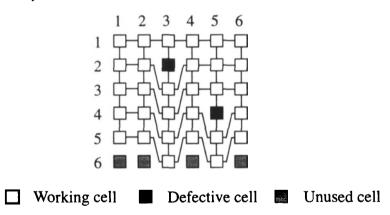

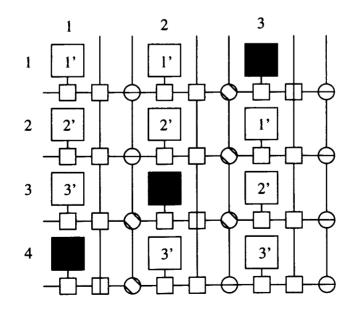

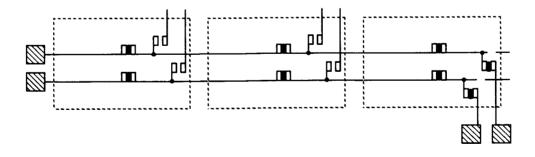

### 4.2.1 Row-Column Substitution

The simplest way of avoiding defects is the row-column substitution. If a defective cell is found during the tests, the entire row or column containing this cell is bypassed; this method is very fast and requires simple algorithms. The bypassing circuitry is kept to a

minimum, since the signals only have to go through the cell and reach the adjacent one. Figure 4.3 shows a 2D array of 6 x 6 cells being restructured using the row-column substitution technique. The algorithm must alternate and substitute a row after a column in order to maximize the size of the array. Proceeding that way, the worst array is equal to the size of the original array minus the number of defects divided by 2. The restructuring is however more complex, because of defects occurring in the bypass circuitry. The algorithm must bypass cells with defects in the reconfiguration circuitry first, since they only can be bypassed either by a column or a row.

**Figure 4.3 Row-Column Substitution**

As an example, the bottom defective cell (row 5, column 5) in Figure 4.3 has to bypass the signal from the cell on its left to the cell on its right. This can only be done if the horizontal bypass circuitry is not defective. If this circuitry is defective, then this cell has to be bypassed with a row and the other defective cell would be bypassed by a column to keep the logical array at 5x5 cells. Of course, both the horizontal and vertical bypass circuitry may be faulty; in this case, the algorithm must use both the column and the row substitution, reducing the size of the final array.

While this method is simple and economical in time, it leaves lots of unused cells

and, if the defect density is high, the final array will be very small. The size of the array should increase if the defects tend to agglomerate, because many defects can be bypassed with only one column or row substitution. Due to its simplicity, this method is well suited to the restructuring of smaller arrays where the yield is already high. A method similar to dynamic RAM memory column substitution will be investigated for the restructuring of small FPGAs later in this chapter.

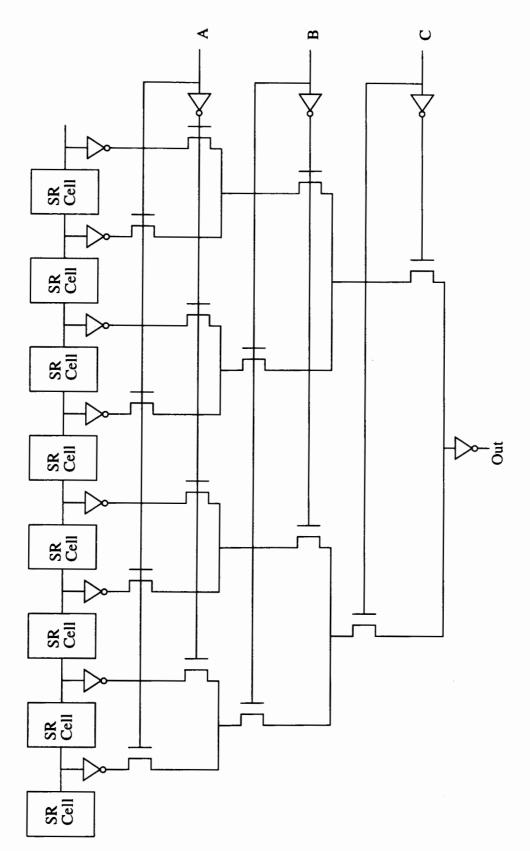

### 4.2.2 Cell by Cell Substitution

The next method is called cell by cell substitution. When a defective cell is encountered, a neighboring cell is used to replace it. Special restructuring buses are placed between the columns of cells. With a combination of switches, the defective cells can be bypassed and an array can be constructed.

Figure 4.4 Vertical Cell by Cell Substitution

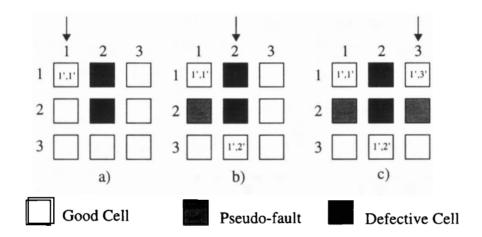

An example is shown in Figure 4.4. There is a defective cell in row 2, column 3. When connecting the rows, the cell in the row below (row 3) is used to replace the defective cell (row 2). So every cell in column 3 must be shifted down in order to complete the rows. An interesting thing happens if another defective cell appears in column 3. Now the cells need to be shifted 2 rows down in order to complete the restructuring. There are

two ways to handle this problem: the first is to provide an additional restructuring channel between each column. This is straightforward but requires additional area and the maximum number of defective cells allowed in a row is equal to the number of restructuring channels. The second way is to use pseudo faults: working cells are sacrificed to allow the use of only one restructuring channel while being able to restructure an array with many defective cells in the same area. This is very important because the defects tend to cluster on a wafer. In the vertical cell by cell substitution, the columns are kept straight while the rows are shifted down; this means more rows than columns are needed to restructure a square array. Another way to perform the cell by cell substitution is to use restructuring channels in both the vertical and horizontal direction. This allows efficient harvesting but requires complex algorithms and the major drawback is the high amount of overhead involved in these architectures. Because of the large area already occupied by the FPGA routing, this technique is not investigated in this thesis.

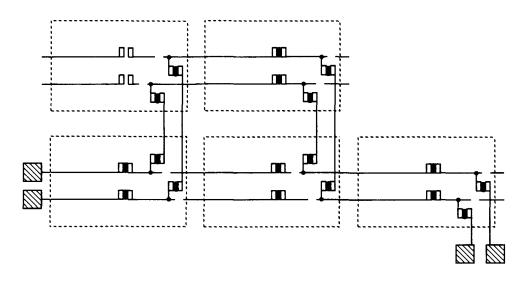

### 4.2.3 Row-Column and Cell Substitution

The cell by cell substitution is an efficient way to restructure an array, but it assumes that the restructuring circuitry is fault-free. The best way to restructure FPGAs is to use a combination of the two methods presented above. The main restructuring remains the cell by cell substitution, however a set of extra columns is also provided. This extra set has a dual purpose: first, it allows the bypass of an entire column if a restructuring bus is defective; secondly, the extra columns can be used to replace columns containing the most defects and gain extra rows. An example of such a restructuring is shown in Figure 4.5. The defective cell (2, 3) was bypassed using the cell by cell substitution while the cluster of three defective cells in column 5 was bypassed by the column substitution method. The result is a 5x5 array while cell by cell substitution alone would allow only 3 rows.

Figure 4.5 Row-Column and Cell Substitution

### 4.3 Algorithms and Yield Simulations

This section shows the algorithms and yield simulations performed to find the best restructuring technique applicable to FPGAs. The restructuring methods elaborated in the last section are studied and explained in detail, while the algorithms and Monte-Carlo simulation results are set out and discussed. A brief description of the defect distribution model is also presented.

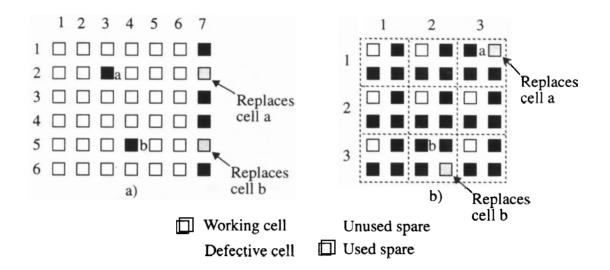

### 4.3.1 Defect Distribution Simulations

There are many papers dealing with the simulation of the defect distribution of a particular fabrication process [18-23]. In earlier yield models, the defect distribution on the wafer was thought to follow a Poisson distribution:

$$P(X=k) = \frac{e^{-\lambda}\lambda^k}{k!}$$

(4.1)

where  $\lambda$ =defect density per unit area, k=number of defects and P=probability of having k defects in the unit area. This distribution means that the probability of a defect appearing

in a region of the wafer is completely independent of the defects already present.

Experimental data however shows the probability of a defect appearing in an area is dependant on the number of defects already present in this area. This phenomenon is called defect clustering. The distribution is then better represented by a Negative Binomial Distribution:

$$P(x, S) = \frac{\Gamma(x + \alpha_c)}{x! \Gamma(\alpha_c)} \frac{(\lambda/\alpha_c)^x}{(1 + \lambda/\alpha_c)^{x + \alpha_c}}$$

(4.2)

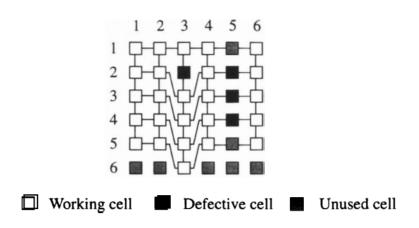

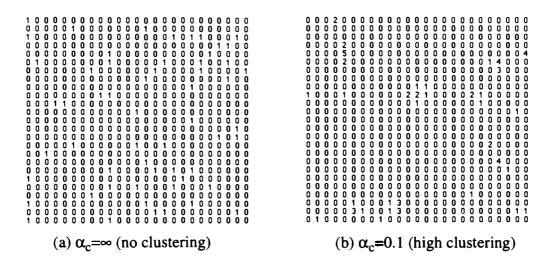

where P=probability of having x defects in an area S,  $\lambda$ =defect density and  $\alpha_c$ =cluster coefficient. In most models the area used for  $\lambda$  is that of the circuit block or cell. Clusters begin to appear on the wafer, depending on the value of the  $\alpha_c$  parameter. A low value for  $\alpha_c$  means a high clustering. An infinite  $\alpha_c$  parameter means no clustering,  $\alpha_c$ =1 is moderate clustering while  $\alpha_c$ =0.1 is high clustering. Values of  $\alpha_c$  ranging from 0.125 to 4 have been encountered in samples of different products [22].

It is almost impossible to create a model that will perfectly reflect the defect distribution of a known process. Extensive research on the process itself can only give partial knowledge of the defect distribution. A defect distribution Monte Carlo simulation was developed here at SFU. The goal was to distribute defects on a wafer with a distribution that follows the Negative Binomial Distribution. The simulation is based on the model presented by C. H. Stapper in [23]. The program starts with an array of non defective cells; after a time interval  $\Delta t$ , the appearance of a defect in the cell is calculated by comparing a random number generated with an assigned probability for each cell. This probability is a linear function of the number of defects in the cell and in its four nearest neighbors. The weight associated with the number of defects in the cell is higher than the weight for the neighbors. By changing the value of these weights, the  $\alpha_c$  parameter can be

changed. If the number of defects in the cell itself and the neighboring cells is not taken into account, a Poisson distribution is obtained. The program stops when the desired defect density is obtained. An example of two defective cell maps is shown in Figure 4.6.

Figure 4.6 Defect Map Example ( $\lambda$ =0.1)

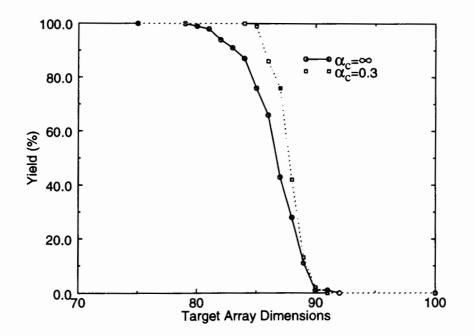

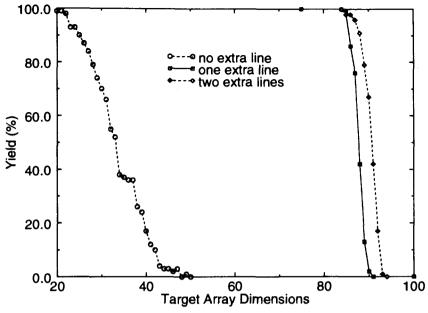

The map on the left (Figure 4.6 a) is a pure Poisson distribution ( $\alpha_c = \infty$ ) while the one on the right (Figure 4.6 b) has a very small clustering coefficient ( $\alpha_c = 0.1$ ) thus significant clustering. Both maps have the same average number of defects per cell ( $\lambda=0.1$ ). Note on the right that certain cells have a very high number of defects and how the defects tend to be grouped in clusters.