•

National Library of Canada

Canadian. Theses Service

Ottawa, Canada K1A 0N4 Bibliothèque nationale du Canada

Services des thèses canadiennes

# CANADIAN THESES

# THÈSES CANADIENNES

## NOTICE

The quality of this microfiche is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Previously copyrighted materials (journal articles, published tests, etc.) are not filmed.

Reproduction in full or in part of this film is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30.

## AVIS

La qualité de cette microfiche dépend grandement de la qualité de la thèse soumise au microfilimage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des vages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

Les documents qui font déjà l'objet d'un droit d'auteur (articles de revue, examens publiés, etc.) ne sont pas microfilmés.

La reproduction, même partielle, de ce microfilm est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30.

THIS DISSERTATION HAS BEEN MICROFILMED EXACTLY AS RECEIVED LA THÈSE A ÉTÉ MICROFILMÉE TELLE QUE NOUS L'AVONS REÇUE

## EVALUATION OF SOME DISTRIBUTED FUNCTION ARCHITECTURES FOR ARRAY

PROCESSING DATA MANIPULATION

by

. 18

-John Jonas Gudaitis

B. Sc., University of Missouri at Rolla, 1975.

# THESIS SUBMITTED IN PARTIAL FULFILLMENT OF ~ THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE

in the Department

of

Computing Science

(C)

John Jonas Gudaitis 1985 SIMON FRASER UNIVERSITY

July, 1985

All rights reserved. This work may not be reproduced in whole or in part, by photocopy or other means, without permission of the author. Permission has been granted to the National Library of Canada to microfilm this thesis and to lend or sell copies of the film.

The author (copyright owner) has reserved other publication rights, and neither the thesis nor extensive extracts from it may be printed or otherwise reproduced without his/her written permission. L'autorisation a été accordée à la Bibliothèque nationale du Canada de microfilmer cette thèse et de prêter ou de vendre des exemplaires du film.

L'auteur (titulaire du droit d'auteur) se réserve les autres droits de publication; ni la thèse ni de longs extraits de celle-ci ne doivent être imprimés ou autrement-reproduits sans son autogisation écrite.

ISBN Ø-315-30711-0

#### APPROVAL

Name: John Gudaitis

Degree: Master of Science

Title of thesis:

Evaluation of Some Distr; buted Function Architectures for Array Processing Data Manipulation

Examining Committee:

Chairperson:

Thomas K. Poiker

Richard F. Hobson Senior Supervisor

Brian V. Funt

Louis J. Hafer

Hassan K. Reghbati External Examiner Assistant Professor Department of Computing Science Simon Fraser University

Date Approved:

3 July 1985

-3

#### PARTIAL COPYRIGHT LICENSE

I hereby grant to Simon Fraser University the right to lend my thesis, project or extended essay (the title of which is shown below) to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its users. I further agree that permission for multiple copying of this work for scholarly purposes may be granted by me or the Dean of Graduate Studies. It is understood that copying or publication of this work for financial gain shall not be allowed without my written permission.

Title of Thesis/Project/Extended Essay

Evaluation of Some Distributed Function architectures for arri Proce

Author:

(signature)

John Jonas Gudaitis

(name)

quet 12, 1985 (date)

#### ABSTRACT

Parallelism has been used extensively in supercomputer systems to improve performance but has had limited application in microcomputers. A structured architecture machine (SAM) was designed for use as a high performance engineering workstation. It has a distributed function architecture that allows modular extensibility to increase performance. SAM uses indirect high-level language execution to give good performance while providing the user friendly interface associated with interpretive systems. This thesis investigates data manipulation strategy for SAM architectures through simulated execution of array processing benchmarks. Attached slave processors provided the simplest method for optimizing system performance. Maintaining good firmware structure without performance degradation requires assistance from special hardware to support control constructs and device interfacing. Performance of benchmark execution on SAM is more than an order of magnitude better than execution of compiled C versions running on a VAX750 and a SUN workstation.

5

iii

# TABLE OF CONTENTS

10

| Approvalii                                                   |

|--------------------------------------------------------------|

| Abstractiii                                                  |

| List of Tables                                               |

| List of Figuresvii                                           |

| 1. INTRODUCTION                                              |

| 1.1 High-Level Language Support1                             |

| 1.2 Instruction Set Performance                              |

| 1.2.1 Increasing Performance of Instruction Set<br>Execution |

| 1.3 Structured Architecture9                                 |

| 1.4 Overview of Thesis11                                     |

| 1.4.1 Thesis Goals11                                         |

| 1.4.2 Methods12                                              |

| 1.4.3 Organization of Thesis                                 |

| 1.4.4 Assumptions                                            |

| 2. SYSTEM MODELS AND EXPECTED PERFORMANCE                    |

| 2.1 Benchmarks16                                             |

| 2.2 System 1 Performance17                                   |

| 2.3 System 2 Performance                                     |

| 2.4 System 3 Performance                                     |

| 3. SAM 0.5                                                   |

| 3.1 System 1                                                 |

| 3.1.1 Microprogram structure                                 |

| 3.1.2 Memory streaming                                       |

| 3.1.3 Analysis of results                                    |

iv

| ٤          |                                              |

|------------|----------------------------------------------|

| 3.         | 2 System 2                                   |

|            | 3.2.1 System 2 performance                   |

| <b>4</b>   | 3.2.2 Analysis                               |

| 3.         | 3 System 3                                   |

| 3.         | 4 Glossary of SAMjr Microprogramming Terms53 |

| 4. SAM 1.0 |                                              |

| 4.         | 1 System 1                                   |

| 4.         | 2 System 2                                   |

|            | 4.2.1 SFU interfacing                        |

| 4.         | 3 Potential Arithmetic Processors            |

|            | 4.3.1 Multiple APU Algorithms71              |

| 4.         | 4 System 3                                   |

|            | 5 Summary of Performance                     |

| 4.         | 6 Space - Time Tradeof £5                    |

|            | 7 Glossary of SAMjr Microprogramming Terms83 |

| 5. SUMMARY | AND CONCLUSIONS                              |

| 5.         | 1 Scalar vs Vector Processing                |

| 5.         | 2 Comparison of SAM .5 and SAM 1.0           |

| 5.         | 3 Comparison with other systems              |

| 5.         | 4 Memory Streaming92                         |

| 5.         | 5 Separate Arithmetic Processors             |

| 5.         | 6 Firmware structure                         |

| 5.         | 7 Dynamic size data                          |

| 5.         | 8 Conclusions                                |

|            | 5.8.1 Future Research                        |

| Bibliograp | hy                                           |

×

v

4

t

.

|                    | LIST OF TABLES                        |            |      |

|--------------------|---------------------------------------|------------|------|

|                    | · · · · · · · · · · · · · · · · · · · |            |      |

| TABLE              |                                       | 1          | PAGE |

| 4 - 1 SAM 1 Perfor | mance                                 | •••••      | 80   |

| 5 - 1 Benchmark Pe | rformance Comparison                  | •••••••••• | 90   |

| 5 - 2 FRI for Sele | cted Computer System                  | is         |      |

ł

ħ

# LIST OF FIGURES

|    | FÌ | G      | JRE        | PAGE                                                                     |   |

|----|----|--------|------------|--------------------------------------------------------------------------|---|

|    | 1  | -      | 1          | Instruction execution                                                    |   |

|    | 2  | -      | 1          | Algorithms for Matrix Multiply 17                                        |   |

|    | 2  | -      | 2          | Minimal SAM System 18                                                    | , |

| •  | 2  | -      | 3          | System 2 - Auxillary SFUs 20                                             |   |

| e- | 2  | -      | 4          | Overlapping data fetch with action21                                     |   |

|    | 2  | -      | 5          | Effect of Buffering on Timing 22                                         |   |

| _  | 2  | -      | 6          | System 3: Independent APU 24                                             |   |

|    | 3  | -      | 1          | SAMjr Schematic 25                                                       |   |

|    | 3  | -      | 2          | Micros MK16 Schematic25                                                  |   |

| ,  | 3  | -      | 3          | DMU instruction execution 28                                             |   |

|    | 3  | -      | 4          | General Vector Control Microprogram and Support<br>Functions             |   |

|    | 3  | -      | 5          | Size Specific Dyadic Vector control Microprogram 32                      |   |

|    | 3  | -      | 6          | Dyadic Vector Loop with Memory Streaming 34                              |   |

|    | 3  | -      | <b>7</b> ` | Size Specific Dot Product Control Microprogram<br>using Algorithm (a) 36 |   |

|    | 3  | -      | 8          | Size Specific Dot Product Control Microprogram<br>using Algorithm (b) 37 |   |

|    | 3  | -      | 9          | Workload Distribution of Vector Add 39                                   |   |

|    | 3  | -      | 10         | Workload Distribution of Benchmark 2 40                                  |   |

|    | 3  | -<br>- | 11         | System 2 Configurations 43                                               |   |

|    | 3  | -      | 12         | Size Specific Vector Multiply Microprogram 44                            |   |

|    | 3  | -      | 13         | Overlapped Vector Multiply Microprogram for<br>structure (a) 47          |   |

vii

| 3. | -          | 14 | System 3 Architecture                                             | 51 |

|----|------------|----|-------------------------------------------------------------------|----|

| 3  | -          | 15 | General Vector action Microprogram for System 3                   | 51 |

| 3  | -          | 16 | Overlapped Vector action Microprogram                             | 52 |

| 4  | -          | 1  | SJ16 Microarchitecture                                            | 57 |

| 4  |            | 2  | New SAMjr Architecture                                            | 59 |

| 4  | -          | 3  | SJ16 Vector Control Loop for 16 bit Data                          | 60 |

| 4  | -          | 4  | Dot Product Microprogram                                          | 62 |

| 4  | -          | 5  | Special Matrix Multiply Microprogram                              | 63 |

| 4  | -          | 6  | Decode Firmware Structure                                         | 65 |

| 4  | -1         | 7  | Special Vector Integer Add Microprogram                           | 66 |

| 4  | -          | 8  | Multiple fast chip control                                        | 72 |

| 4  | -          | 9  | Multiple slow chip control                                        | 73 |

| 4  | -          | 10 | APU Weitek Chip Set Control                                       | 74 |

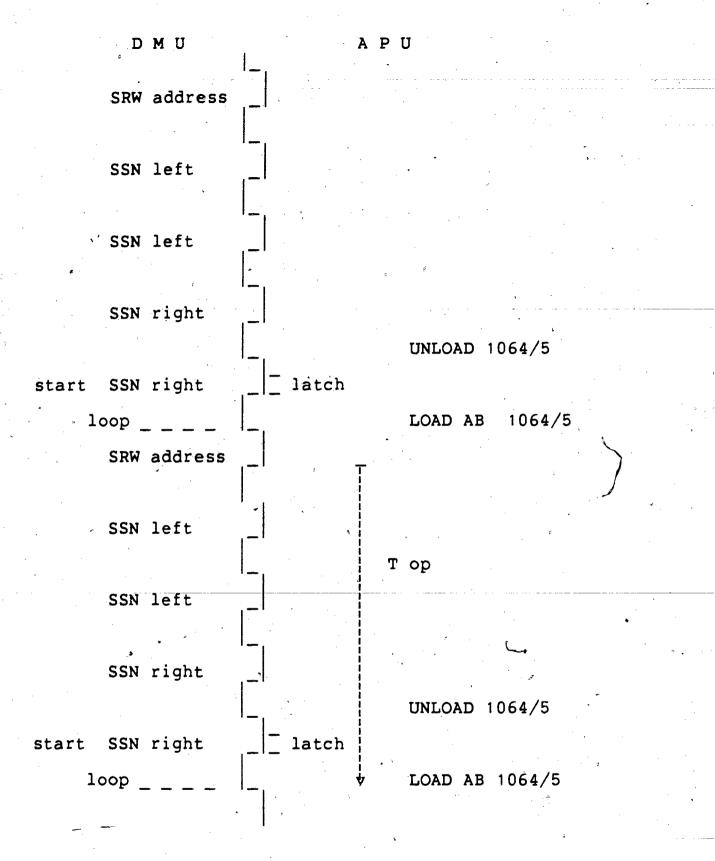

| 4  | -          | 11 | DMU and APU timing diagram for vector inner product               | 75 |

| 4  | <b>-</b> s | 12 | DMU control code for 16 bit vector dyadic actions<br>using case   | 76 |

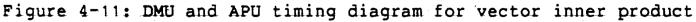

| 4  | -          | 13 | SAM system hierarchy                                              | 79 |

| 5  | -          | 1  | Functional Distribution of Benchmark 1 using<br>Scalar Processing | 87 |

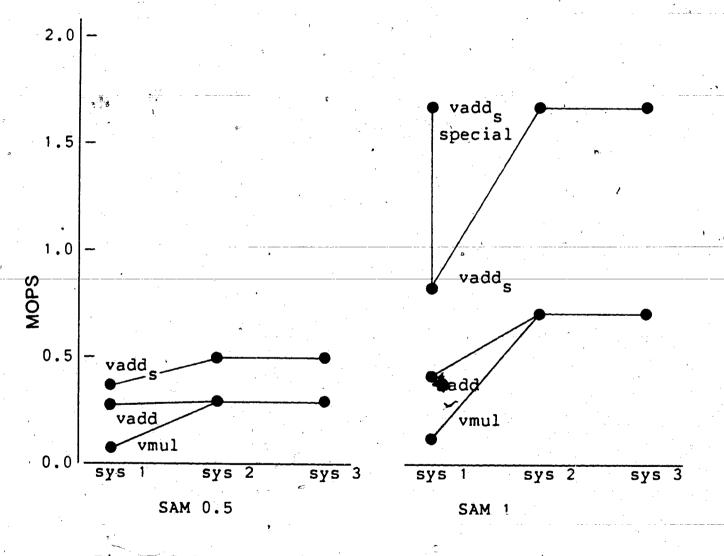

| 5  | -          | 2  | Comparison of SAM 0.5 and SAM 1.0                                 | 88 |

2

viii

4

•

$\leq$

~

CHAPTER 1

### INTRODUCTION

This thesis explores some aspects of the performance of a structured architecture machine developed for the interpretation of high-level languages (HLL). It is hoped that the results will help dispel some myths associated with interpretive HLL computer systems and thus allow such systems to become more popular. This thesis will examine some strategies to improve data manipulation performance, borrowing ideas used in supercomputer systems and applying them to a microcomputer system. A brief introduction to past efforts in these areas follows. Section 1.1 reviews efforts in HLL support. The performance of instruction sets is then discussed in section 1.2. Section 1.3 discusses the use of structured architecture to design cost effective systems. Finally, an overview of the thesis is given in section 1.4.

1.1 High-Level Language Support

HLL support has been a subject of investigation ever since the days of the first computer, with many researchers attempting to reduce the semantic gap between high-level language concepts and the underlying computer architecture that actually supports these concepts. Reviews of this research can be found in [12]

and [72]. Chu[13] categorized computer systems architecture according to the proximity of the HLL seen by the user to the machine language actually executed.

Type 1, von Neumann, is used in most commercial computer systems. It is characterized by a low level register-oriented instruction set, generally requiring a complex compilation process to convert a HLL program into machine language code. Complex instruction sets such as that of the VAX-11[21] provide some instructions oriented toward HLLs but are too limited to have much effect on reduction of the semantic gap. This type of architecture has been criticized by Backus[6] and Chu and Abrams[16] for contributing to the so called "software crisis". They believe that the tedious design - edit - compile - load run - debug, process lowers programmer productivity. Efficiency considerations have influenced the design of HLLs to be supported by compilation. Very high level languages (VHLLs), such as APL, Lisp, Prolog, NIAL that support program development at a high level of data abstraction, are usually interpreted by software on this type of architecture. This extra layer of software causes the perceived inefficiency of language interpretation.

Type 2 architectures raise the level of the machine language by supporting interpretation of syntax-oriented intermediate code. While this reduces the semantic gap, it does not reduce the necessity for large subroutine libraries or improve the software development process.\*Borroughs B5500 is an

example of this architecture supporting algo1.

Type 3 architectures are the indirect execution type exemplified by the Symbol system [64]. The main improvements over type 2 are a hardware translator and an improvement in proximity for the intermediate polish string language.

Type 4 is the direct execution architecture studied by Chu, Bloom, and others. There is no intermediate language so therefore no semantic gap. All user software and system programs are written in the HLL.

Dietzel and Patterson [20] have suggested a High-level language computer system as a possibility for a more productive environment for software development. Their definition concerns only the interface presented to the user, so that type one systems are included if the operating system insulates the user from the lower layers of software. This could include ROM based BASIC microcomputer systems. Although this concept can be supported with compilation, an interpretive high-level language system offers benefits especially for VHLLS.

#### 1.2 Instruction Set Performance

The instruction set selected (user architecture) affects the software development process, but performance also determines user acceptance. The user architecture must allow efficient implementation. Compilation may not achieve this goal for applications where source code is changed frequently.

Flynn and Hoevel [31] have pointed out the inefficiencies of the compilation approach on conventional machines. They derived a directly executable language (DEL) that reduced the semantic gap and thereby reduced the size of the intermediate code. This should improve performance by reducing the number of instruction fetches, executes, and memory references. Their DEL featured a transformationally complete instruction set which they felt would simplify compilation. They also showed how to design an efficient system to interpret a DEL. While their research showed significant improvement over other complex instruction sets, other methods have produced better run time performance. Reduced instruction set computers (RISCs), for example, seem to give better performance, at least for some HLLs[74].

Some recently designed computer systems use statistical methods for instruction set design [36,75,68]. The most frequently used operations in a HLL are given a corresponding machine instruction. Instruction set usage obeys the 20-80 rule [97], so only a small subset of a language needs to be implemented efficiently to get good performance. Actually, the main factors in scalar block-structured HLL performance have been found to be procedure call and variable binding[57,76]. Thus the fast overlapped register banks of RISC may be largely responsible for its good performance[35].

Thurber[89] notes a lack of support for HLL data structures in computer architectures. An example of data structure support

is vector processing. One approach to providing support for arithmetic operations on arrays has been to use vectorizing compilers running on supercomputers. While this has had some success in improving performance, it forces users to write more complex low level code. Such a programming environment requires control coding at a level lower than that of the machine hardware and has been shown to provide less than full performance [22]. Language extensions are more useful but usually limited in the data manipulations allowed. It has been noted that supercomputer development has spawned novel high performance hardware but has not contributed to advances in software [19]. Hardware improvements will be more effective when they are transparent to the user. VHLLs with full support for vector processing should offer a better environment for program development and an opportunity for performance improvement through language directed design.

Chu [14,15] promotes the advantages of a direct execution computer, especially its conceptual simplicity. This architecture has been criticized for poor performance [44,57]. Hardware interpretation can improve this problem, but this architecture still suffers from redundant syntax analysis, which adds unnecessary hardware costs to the system. With enough hardware support, such a system may be competitive with other methods in run time performance. However, indirect execution can provide a user interface indistinguishable from direct execution but with lesser hardware requirements and reduced redundant

5.

processing. Hobson[40] has extended the DEL approach to interpreted languages. He has derived a directly interpretable language (DIL) with a one to one correspondence to source operations that permits recovery of the source. Thus only one copy of a program need be maintained with obvious benefits when programs are modified.

1.2.1 Increasing Performance of Instruction Set Execution

While the instruction set puts limits on performance, actual performance is dependent on implementation strategies. Speed increases due to technology advances are limited so further performance enhancement must come from changes in system architecture. This section examines some methods that have been used to reduce instruction execution time.

Consider the interpretation of a typical HLL instruction as shown in figure 1-1. It consists of a sequence of primitive actions which accomplish the required task. For scalar instructions the entire sequence is repeated for each instruction. Compiled code does not require steps 2 and 3 since verification can usually be done by a compiler for strongly typed languages. For vector instructions the last three actions need to be repeated for each element of the vector. Therefore increasing performance of a scalar machine involves all phases of instruction execution, while vector machine performance may be enhanced by reducing the execution time of the loop section,

especially for long vectors.

Instruction pipelining has been used to improve performance of mainframe computer systems for scalar instruction sets. To achieve higher performance, some later phases of an instruction can be overlapped with the early phases of the next instruction. To accomplish this requires some extra hardware resources. In conventional high performance von Neumann machines, centrally controlled instruction and data manipulation units are used to allow concurrent execution of phases [7]. This requires complex control features to handle scheduling and data dependency problems [48]. Statistics on HLL instruction usage indicate that such methods may not significantly improve scalar performance, since subroutine calls predominate in performance determination. Branches and a scarcity of functional instructions further

| SCALAR<br>fetch and decode | VECTOR<br>fetch and decode |

|----------------------------|----------------------------|

| verify operand(s) syntax   | verify operand(s) syntax   |

| verifysemantics            | verify semantics           |

| fetch operand              | fetch operand              |

| action                     | action                     |

| store results              | store results              |

| *                          | ¥                          |

Figure 1-1. Instruction execution sequence.

reduce the performance potential of scalar overlapped computers.

Multiple processing units have been used to increase performance [24, 25, 66]. Using n processors has potential for n fold speedup. In practice, multiple homogenous processor systems suffer from scheduling overhead and memory access contention. Some of these systems exhibit breakover point behavior where addition of a processor can actually decrease system performance [88]. Memory and processor communication requires complex bus interconnections [55]. It is also difficult to express some problems in a form that can be used on such a system.

Thurber[89] suggests using a functionally distributed architecture to overcome these problems. A pipeline is an example of this architecture. A multiprocessor distributed function architecture (DFA) can achieve overlapped performance without complex central control. The Symbol computer system mentioned earlier is an example of this type of architecture designed for a single HLL. The Symbol system offered improved performance because of its modular multiprocessor architecture which allows overlapped operation of the translation and execution processes. Unlike the homogenous multiple processor architecture, this system consists of heterogenous processors each designed to perform specific functions. With appropriate functional partioning and interfaces the design of each module is independent of the others.

In a typical overlapped computer, dedicated hardware modules can be used to achieve good performance since machine

instruction execution is very regular. The greater diversity in high-level language instructions makes the control problem for overlapping more difficult. The problem is further complicated in languages allowing vector operations since vector length determines the ratios for phase execution times. A distributed function computer can compensate for timing variablity by the use of queues between processors to absorb variation in workload. Use of queues can also increase performance. This has been shown in a scalar Cray 1 type architecture[81] and a data flow machine model [52].

## 1.3 Structured Architecture

While the cost of hardware components has dropped rapidly, the design phase of system development has become increasingly costly. Structured architecture attempts to reduce the complexity of computer system design by borrowing some of the principles learned from structured programming. Modularity is just as important in computer system design as in software design. Parnas [73] suggests that system decomposition be based on module independence. DFA architectures satisfy his criteria since each module is designed for a particular class of functions. Encapsulation of related functions also can meet the VLSI constraint of minimizing chip pin count. Conventional computer systems do not distinguish between control computation and data manipulation. A resource may be shared between a control operation and a data manipulation. This can lead to

extra interaction between independent processes because of possible contention for the resource. Shared resources must also be designed to accommodate both types of processing. An example is a multiplier used both for array indexing and a user specified multiplication of some data.

The size and complexity of current microprogramming projects require new methods for firmware development. This has given rise to a new field of study - firmware engineering. User microprogramming and large system microprogramming have led to a need to upgrade microprogramming techniques. In particular, the horizontal microprogramming used in supercomputers is only appropriate for static architectures.

A structured architecture machine (SAM) [38] has been designed with a modular extensible architecture for indirect high-level language interpretation. The aim is to develop a single user workstation that will offer performance comparable to the usual execution of compiled code, with enhanced performance for array manipulation and special engineering applications. Microprogramming is used for control rather than hardware because of its greater flexibility. This is especially important for an experimental system undergoing frequent modifications. Language independent features can later be supported by hardware to improve performance. Seldom used language features can be implemented in a subset of the HLL with very little performance penalty.

The SAM project differs from Flynn and Hoevel's work in several respects. It is aimed at interpretation of DLLs rather than compiled DELs. SAM uses a language directed architecture rather than microprogramming of an unbiased host microengine. Functional task partioning results in separate modules for environmental control, program management, and data manipulation. This allows parallel execution of the different stages of instruction execution.

1.4 Overview of Thesis

#### 1.4.1 Thesis Goals

This thesis evaluates the performance of some system designs during the data manipulation phase of DIL interpretation. Structured architecture design is used to derive a system suitable for DIL interpretation. Hobson [42] has already studied improvements in the fetch-decode and verification stages of execution, introducing a hardware operand verification unit (OVU) to reduce semantic verification time. This study concentrates on improvement of the later stages of instruction execution. In extending the SAM architecture, arithmetic units are added to provide overlapped operation.

Execution time is not the only factor in measuring performance. Program development time, compile time, and debug time reduce performance, especially for programs with a low number of production runs. Interpretive systems perform better

in these respects but such measures are difficult to quantify, so this thesis measures execution time performance. Even for this aspect, the results show that a properly designed interpretive system offers performance comparable to the usual execution of compiled code.

Since the SAM project is aimed at development of a low cost high performance single user HLL system, implementation methods must be cost effective. Techniques used for performance improvement on supercomputers may not be appropriate. For example, 64 bit data buses are too costly unless this size of data is used frequently. A goal of the SAM project is to find ways to reduce microprogramming complexity. A multiprocessor system, each unit vertically microprogrammed, offers much more flexibility than a central horizontally microprogrammed system. Statistical analysis can be used to select instructions to be supported directly.

## 1.4.2 Methods

The effect of architectural changes was measured by simulating benchmark execution. Microcode interpreters were coded in microAPL [41]. An architecture support package written in APL supports hardware modeling. Introduction of new architectural features required modification to this package. A discrete event simulator was written to support similation of multiple processors. This was written in APL and has a structure almost identical to the system architecture. A top level module

handles timing of transfers to the appropriate module at the next level. These modules (PMU, DMU, APU) then simulate instruction execution in the corresponding physical modules.

During system 1 simulation, statistics were gathered on the amount of time spent in each phase of instruction execution. This information then guided task partioning for SAM extensions.

Although this study concentrated on supporting vector instructions, benchmark performance using a scalar DEL was also determined for the simplest SAM system. A comparison with vector performance revealed that it was not worthwhile pursuing methods to enhance scalar data manipulation performance.

#### 1.4.3 Organization of Thesis

The results of this study are organized into 4 chapters. Chapter 2 introduces some data manipulation strategies and examines performance limitations. Two different microarchitectures are used for SAM building blocks. Chapters 3 and 4 explore implementions of these strategies psing the building blocks and their influence on SAM's performance. Finally, chapter 5 summarizes the results and compares the performance of SAM to other machines.

# 1.4.4 Assumptions

Execution of an ADEL type instruction set[40] is assumed in this study for the vector HLL. No specific HLL is assumed

since syntax details are handled by a program management unit (PMU), but APL and ADEL are used as typical examples of vector oriented languages. In this study our concern is with execution of internal DIL code accessed by the data manipulation unit (DMU) after completion of verification. Only those instructions required for benchmark simulation are defined and implemented.

A numeric type with varying size for variables is assumed. The size varies as needed to maintain precision. Many HLLs base type distinctions on arbitrary historic considerations. Furthermore, actual physical implementation of the type is system dependent for the same HLL. Variables are assumed to be local to the current environment since binding of non local variables is implementation and language dependent. Local variables are accessed directly from the current data segment that was set up on entry to the current environment. The operand syllable is used as a direct index into the current data segment. APL requires a slightly different binding method and an implementation on SAM will use hardware assist in variable binding [42]. The above model was used for this study since the hardware design was not complete.

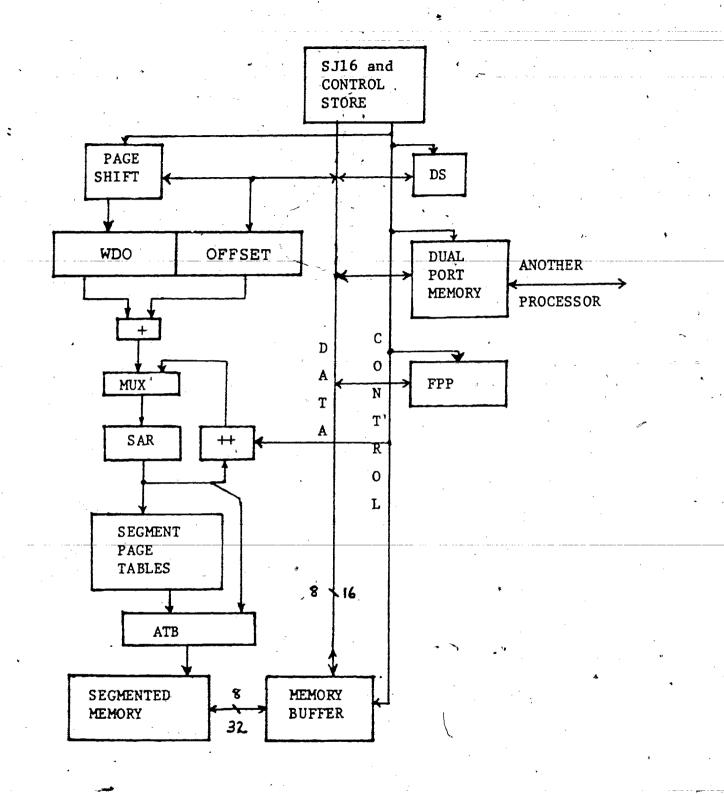

# SYSTEM MODELS AND EXPECTED PERFORMANCE

In this chapter, some system architectures are presented and idealized performance limits for two benchmarks are derived by considering the number of parallel resources available along with the maximum data flow available in the data paths of the system models. Real system implementations and performance will be examined in chapters 3 and 4.

Flynn and Hoevel used a nonfunctional ratio to measure instruction set inefficiency. However, their NF ratio suffers from a favoritism for complex instruction sets and is not a good measure of run time performance. Performance estimates are distorted since complex instructions, especially variable length ones require longer decode and execution times. This thesis uses a functional ratio of implementation (FRI) to measure the proportion of time spent on functional calculation. FRI is defined as the ratio of time spent in a functional calculation divided by the total time spent. A ratio of one means that there is no overhead spent in moving data to where it is acted upon. This can occur in an associative processor or in a conventional processor with full overlap. FRI can be greater than one if multiple arithmetic units are used concurrently or if a pipelined arithmetic unit is used.

Three versions of SAM are considered in this thesis, a minimal functional system and 2 others that expand DMU to increase performance.

### 2.1 Benchmarks

Two primary benchmarks are used to compare the performance of architectural modifications. Benchmark one is a simple addition or multiplication of two vectors of equal length. It is expressed as a 5 syllable DIL instruction

DLR, D, L, R, OP.

This and simple variations of it are the most frequently used arithmetic instructions in languages like APL and therefore important to system performance [8,9,18,40].

Benchmark two is matrix multiplication. Its DIL form consists of 6 syllables

DOTDLR, D, L, R, OP1, OP2.

While not used frequently by average users, its long execution time and complex data accessing make it important to performance, especially in an engineering workstation environment. We consider the standard brute force method, cf. figure 2-1(a), and also a variation used in high performance vector machines, cf. figure 2-1(b). These algorithms multiply a 1 by m matrix with a m by n matrix. Other methods such as Strassen's [39,92] are not well suited to vector or cache machines since data accesses are not sequential.

```

for i=1 to 1

for j=1 to m

C[i,j]=0

for k=1 to n

C[i,j]=C[i,j] + A[i,k] * B[k,j]

(a)

C = 0

for i=1 to 1

for k=1 to n

for j=1 to m

C[i,j]=C[i,j] + A[i,k] * B[k,j]

(b)

```

Figure 2-1: Algorithms for Matrix Multiply.

2.2 System 1 Performance

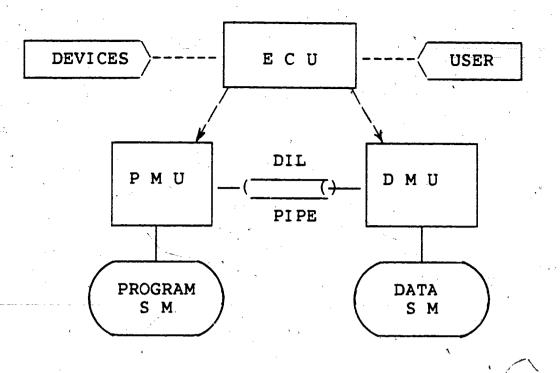

System 1, cf. figure 2-2, is a minimal 3 processor system. It consists of an environment control unit (ECU) for user interaction, a program management unit (PMU) to handle instruction sequencing, and a data manipulation unit (DMU) to fetch and process data. A more detailed description of SAM is available in other publications [38].

ECU accepts user input, translates HLL source input to a linear DIL form, and initiates program execution when requested. PMU fetches DIL code from segmented memory, verifies operand syntax, and sends verified code to DMU. Some control constructs can be handled entirely within PMU. DMU takes DIL code from the PMU - DMU interface, verifies operand semantics, fetches operand data from a data segmented memory, performs specified actions on the data, and returns results to segmented memory.

Figure 2-2: Minimal SAM system.

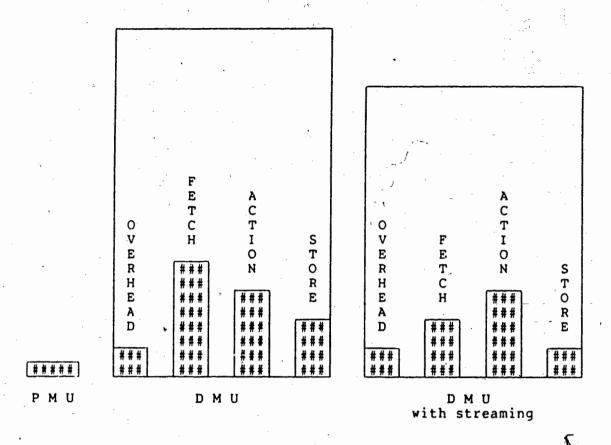

This analysis is mainly concerned with vector loop performance. For arrays of reasonable length, setup time should have minimal effect on performance. Consider the execution of the loop section of a typical diadic vector instruction.

fetch left fetch right perform action store results loop operand operand

Performance for one processor is determined by the sum of the times taken for each phase. Run time loop cost is

$T_{loop} = t_{lf} + t_{rf} + t_{action} + t_{store} + t_{overhead}$ (2-1) Usually  $t_{lf} = t_{rf} = t_{fetch}$  and ideally there is no overhead, so  $T_{loop} = 2 t_{fetch} + t_{action} + t_{store}$ (2-2) Instruction time =  $\overline{n} \times T_{loop} + t_{setup}$ (2-3) FRI =  $t_{action} / (T_{loop} + t_{setup} / N)$ . (2-4) With a single processor, the only way to improve FRI and increase system performance is to speed up memory transactions.

Now consider algorithm (a) for matrix multiply in figure 2-1, henceforth called algorithm 1(a). Performance mainly depends on execution time of the inner loop. In the inner loop we need to fetch sequential elements of A, fetch elements of B in column order, multiply them and add the result to a local running sum. Thus, for system 1 with no parallelism, inner loop cost is

$T_{innerloop} = t_{sf} + t_{nsf} + t_{mul} + t_{add}$  (2-5) where sf is sequential fetch and nsf is nonsequential fetch. and

FRI  $\simeq$  (t<sub>mul</sub> + t<sub>add</sub>) / T<sub>innerloop</sub>. (2-6) This is the dominant term for cost since it must be done 1 m n times.

For algorithm 1b which calculates complete rows of the result, all accesses are sequential. This improves performance if sequential accesses are faster than nonsequential accesses. The cost for the inner loop'becomes

Tinnerloop = t<sub>sf</sub> + t<sub>mul</sub> + t<sub>sf</sub> + t<sub>add</sub> + t<sub>store</sub>. (2-7) Note that A[i,k] is a constant that only needs to be loaded once at the beginning of the loop. Comparing algorithm a with algorithm b and assumming that a sequential store takes the same time as a sequential fetch, we find that a is faster if sequential fetch = nonsequential fetch; they are equal if

sequential fetch = 2 nonsequential fetch; and b is faster if sequential fetch < 2 nonsequential fetch.</pre>

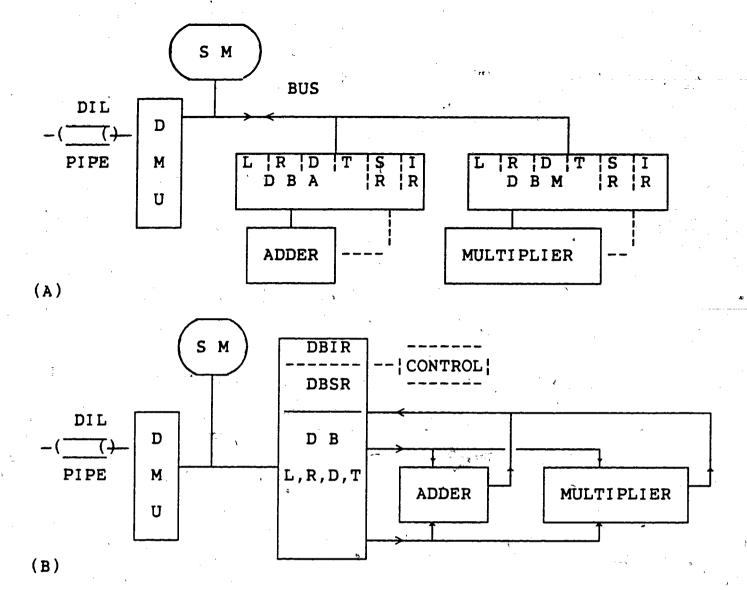

## 2.3 System 2 Performance

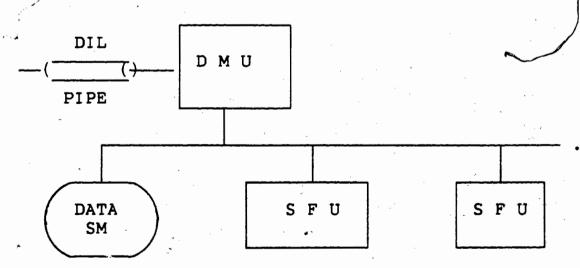

In system 2, auxiliary special function units (SFU's) are added on DMU's external BUS to assist with its processing load, cf. figure 2-3. In this study only arithmetic slave units are considered. These extra arithmetic processors can be used to improve DMU performance especially for complex actions such as multiply, divide, and floating point operations. System complexity is reduced if the processors also perform integer arithmetic. Performance can be further increased by concurrent execution of DMU and slave processors. Arithmetic units can be attached as either separate SFU's or a chip set can be attached as a single SFU with a shared data buffer.

We now consider overlapped performance for this system. Performance without overlapping would be the same as in system

Figure 2-3: DMU with Auxillary SFU''s.

one but with decreased action time for multiply. Action time now includes time to communicate action codes and/or synchronize SFU execution.

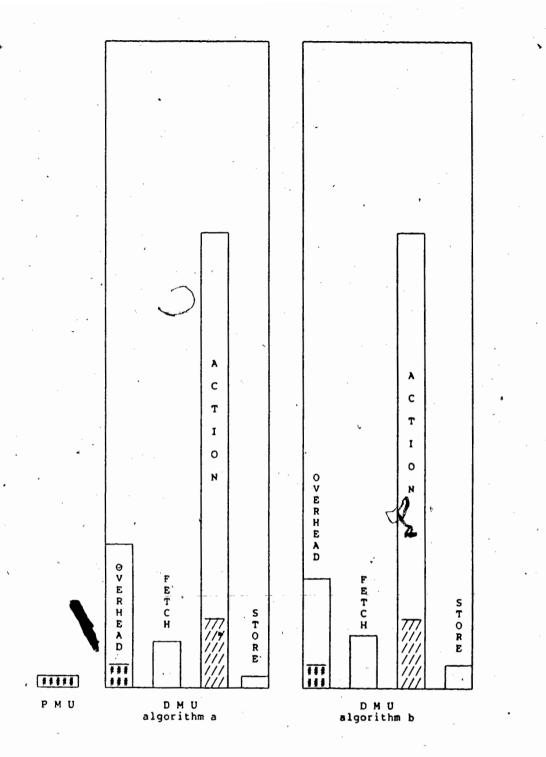

At this point some aspects of the interface between units need to be considered since this affects the amount of overlap that can be achieved. Assume that SFUs are connected as slaves to DMU with actions initiated by DMU. The algorithm for overlapped execution, cf. figure 2-4, uses a one stage software pipeline [59] to support overlapped operation.

fetch left operand fetch right operand start action DO loop (vector length times) fetch left operand fetch right operand store previous result start action end store last result

Figure 2 - 4 : Overlapping data fetch with action.

Operands are loaded, an action initiated, and then new operands are loaded while the action takes place. When available, the result is stored and a new action started. The operand registers must be buffered or isolated so that new values can be loaded without affecting the current operation. If the output register is unbuffered the result must be stored before a new action is initiated and therefore the store and action phases cannot be overlapped. Figure 2-5(a) shows timing for the unbuffered output case and figure 2-5(b) the buffered output case.

| lf  rf   action  str set 1lf  rf  action  str lf  rf  lf  rf  lf  rf  set 3                                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a)                                                                                                                                                                                      |

| IfrfactionstrData<br>set 1Ifrfactionstrset 2Ifrfactionstrset 3Ifrfactionset 411                                                                                                          |

| (b)<br>Figure 2-5: Effect of Buffering on Timing.                                                                                                                                        |

| The loop time performance of case (a) for benchmark 1 is                                                                                                                                 |

| $T_{loop} = MAX \{ 2t_{fetch}, t_{action} \} + t_{store} $ (2-8)<br>and                                                                                                                  |

| FRI = $t_{action} / (MAX{2 t_{fetch}, t_{action}} + t_{store})$<br>FRI cannot be 1 since the denominator above cannot be smaller                                                         |

| than t <sub>action</sub> + t <sub>store</sub> .<br>For case (b),                                                                                                                         |

| T <sub>loop</sub> = MAX { 2t <sub>fetch</sub> + t <sub>store</sub> , t <sub>action</sub> } (2-10)<br>Here FRI approaches 1 for longer actions                                            |

| <pre>if taction &gt; 2 tfetch + tstore. Benchmark 1 was unaffected by the method used to attach</pre>                                                                                    |

| SFU's. Benchmark 2 will be affected since results from one SFU                                                                                                                           |

| must be sent on the bus to another if actions are performed in                                                                                                                           |

| separate SFU's. For algorithm 1 (a), cost of the inner loop is                                                                                                                           |

| Max{ t <sub>sf</sub> + t <sub>nsf</sub> + t <sub>bus</sub> , t <sub>mul</sub> + t <sub>add</sub> } (2-11)<br>if addition and multiplication are done on separate units. T <sub>bus</sub> |

| is the time required to move results from one unit to the input                                                                                                                          |

of another. If a single unit is used,

Tinnerloop = Max{ t<sub>sf</sub> + t<sub>nsf</sub>, t<sub>mul</sub> + t<sub>add</sub> }. (2-12)

Note that the first iteration is not overlapped thus reducing

performance.

For algorithm 1b with memory accesses overlapped with actions the cost is

## 2.4 System 3 Performance

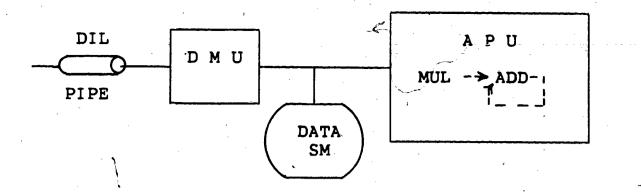

System 3 uses an independent arithmetic processing unit (APU), cf. figure 2-6, capable of chaining multiple actions. System 3 ideal performance for benchmark 1 is the same as system 2 with complete buffering.

For benchmark 2, cost of the inner loop for matrix multiply algorithm 1(a) becomes

(2 - 15)

Tinnerloop =

Max{ tsf + tnsf, tmul, tadd}.

In this case the first 2 iterations are not overlapped.

For algorithm 1 (b), innerloop performance is Max { 2 t<sub>sf</sub> + t<sub>store</sub>, t<sub>mui</sub>, t<sub>add</sub> }. (2-16)

Figure 2-6: System 3 - Independent APU.

Ĭſ

#### CHAPTER 3

#### SAM 0.5

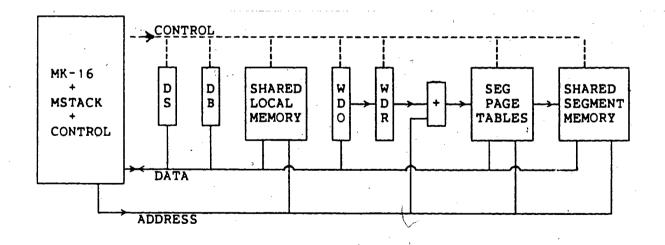

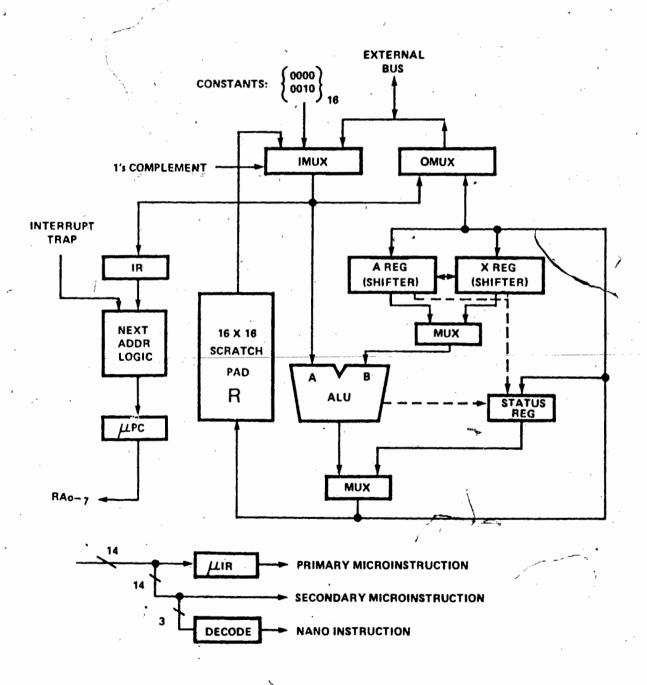

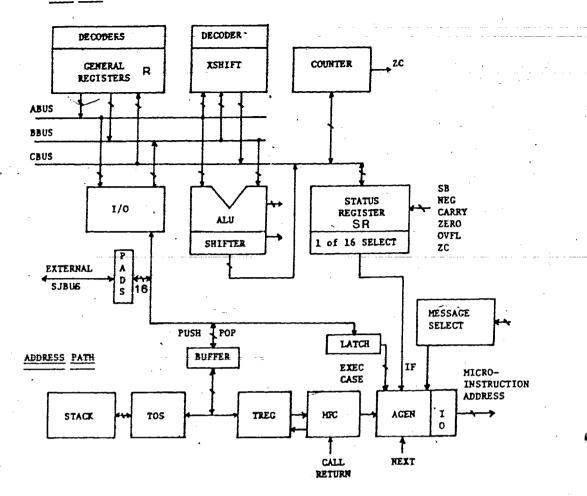

The first version of SAM used a building block module based on a Micros MK16 [71], for PMU and DMU. Figure 3-1 shows a block diagram of this module. Important features are a data stack(DS), a data buffer(DB), and a segmented memory(SM) accessed through windows(WDO), or set of currently open segments. In addition a microprogram stack(MSTACK) supports a microprogram call mechanism. Figure 3-2 shows details of the MK16 internal architecture. See glossary for definitions of other terms. It is essentially a two bus single accumulator microengine. Dyadic

Figure 3-1: SAMjr Schematic.

microoperations take 2 or 3 cycles depending on which source and destination registers are used. MK16 is controlled by a 32 bit microword. Eight more bits were added to control external features via the control bus and to simplify microprogramming. These bits select the SFU's that will transmit or receive bus data. The least significant 4 bits select the SFU register to be used. This must be the same in both source and destination SFU's. Internal and external microoperations proceed concurrently. SAM 0.5 design and simulation was based on availability of a 4 MHz MK16 as promised by Micros Corporation. The SAMjr prototype used an LSI emulator. The clock cycle was extended to 333 nsec to accommodate external data flow.

Q

The previous chapter discussed theoretical performance limits. We now consider implemention on a concrete system. We may not be able to achieve the theoretical performance because of system objectives such as modular structure of firmware, the use of vertical microprogramming, and reasonable cost. A real implementation must consider details such as special function unit synchronization overhead and the detection of overflow from an action. Supporting dynamic precision requires automatic recovery from output precision changes. An MK16 emulator was used to obtain concrete results, introducing architectural changes to evaluate the effect on microprogram structure and performance. Microinstructions are described using a set of mnemonics, which are descibed in a glossary at the end of this chapter. These are executable APL functions describing data flow

and side effects of an microoperation. During simulation, they are executed as a result of microprogram execution. Timing calculations were appended to microinstructions to calculate run time performance during simulation.

Figure 3-2: Micros MK16 Schematic.

### 3.1 System 1

# 3.1.1 Microprogram structure

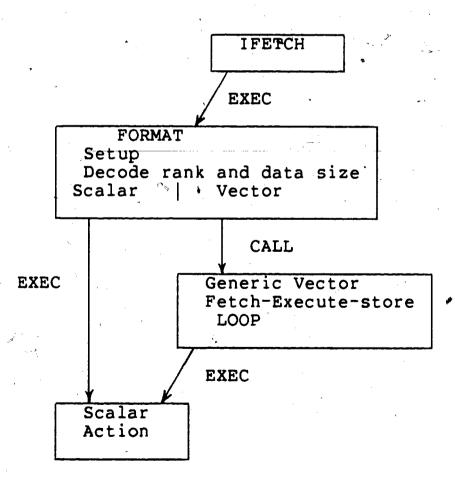

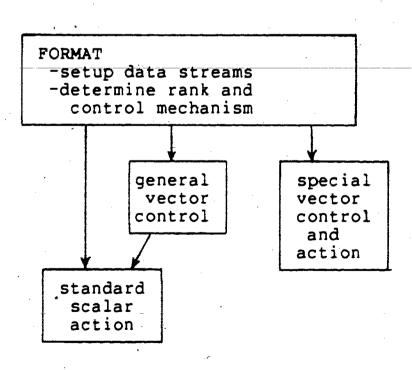

One goal of this project was to examine how microprogram structure affected performance, i.e. Can good modular design coexist with high performance? Figure 3-3 shows the instruction execution hierarchy. DIL code execution proceeds from instruction fetch to format execution using a table driven EXEC, a variable procedure call mechanism. The format procedure performs verification, checks operand rank, and calls the

appropriate rank and data size specific fetch routines. For array operands, operand sylables provide an index into an array descriptor, which gives rank, size, and array data location in segmented memory. The action is EXEC'd from within the vector control microprogram. Dyadic action routines were implemented with a standardized interface, with arguments in DB[left] and DB[right] and results returned in DB[dest].

An objective in implementing the algorithms was to find a microprogram structure that is not costly in execution time. For vector algorithms, loop code is the most important element in determining performance. The first efforts aimed at generality to conserve microcode space. Consider the first benchmark, a DLR vector instruction. The first attempt, cf. figure 3-4, will be used to illustrate microcoding with microAPL. This is a quite general microprogram that works for any of the defined numeric precisions and is modularized with no performance penalty with calls to Lfetch, Rfetch, and STORE routines which can be shared with other formats. Point to point data transfer is indicated by the left arrow, "<-". AR and XR refer to A reg and X reg respectively in figure 3-2. DB is the external data buffer in figure 3-1. R refers to one of the 16 registers in the scratchpad in figure 3-2.

Loop execution starts with fetches of left and right operands through CALLs to left operand fetch, LFETCH, and right operand fetch, RFETCH, subroutines. The status register, SR, is loaded with an operand size tag to allow fetch subroutines to

VLOOPG DMU General vector control С С R[count] is loaded by calling program LOOP: CALL 'LFETCH'  $\Delta$  SR <--R[LTAG] CALL 'RFETCH'  $\Delta$  SR <-R[RTAG] EXEC DB[OP]  $\triangle$  SR<-R[TAG] ->ERROR IF OVFL CALL 'DSTORE'  $\Delta$  SR<-R[TAG] R[COUNT] <-- SNZ DEC1 R[COUNT] ->LOOP IF ¬ZERO clear status and return ERROR: CALL 'RECOVER' "Data size overflow" LFETCH General left operand fetch С Fetch operand and leave in buffer DB[50...L3] С SR contains left size tag on entry С R[LINDX]<-INC2 SRW R[LINDX] "Memory address" ->0 if INT16  $\triangle$  DB[L0]<-S[WORD] "Memory data" R[LINDX]<-INC2 SRW R[LINDX]  $\rightarrow 0$  if INT32  $\triangle$  DB[L1]<-S[WORD] ADD Generic DMU add microprogram С  $\rightarrow$  SHORT IF INT16  $\triangle$  AR  $\langle -DB[R0]$  $\rightarrow$ LONG IF INT32  $\triangle$  XR  $\leftarrow$ DB[R1] SHORT: AR <- SAR AR PLUS DB[L0]  $\rightarrow 0$  IF  $\neg OVFL \Delta DB[D0] < -AR$ ->SKIP if  $\neg$ CARRY  $\triangle$  DB[D1] <-D'0' DB[D1] <--D'-1' SKIP: AR <-R TAG  $->0 \Delta R[TAG] <- LSHIFT AR, 0$ LONG: AR <-SAR AR PLUS DB[L0] XR <-SAR XR PLUSC DB[L1]  $\rightarrow$  CONV IF OVFL  $\triangle$  DB[D0] < AR  $->0 \Delta DB[D1] < -XR$ CONV: CALL 'XOVER' "Convert to floating point" Figure 3-4: General Vector Control Microprogram and Support Functions. " $\Delta$ " is used to separate microoperations within  $a_{\infty}$ microinstruction. determine data size. The tags were read from memory within the format routine. Within LFETCH, SRW(segment read word) sets up

the segment window address and starts a memory cycle. R[LINDX]

is an address pointer used by DMU control microprograms. In the next line, S[WORD] accesses the memory data word. If LTAG size bits were set to indicate 16 bit integers, then control returns to VLOOPG-Otherwise, more data will be fetched. RFETCH is similar to LFETCH. The generic operation syllable is then EXEC'd. The action subroutine, in this example, ADD, then decodes and executes the specific action, setting condition flags when needed. In the ADD microprogram, overflow is set if the result size is larger than that of the operands. This condition is tested by the branch on OVFL in VLOOPG. If therewas no overflow, the result is stored in memory by a DSTORE subroutine. This is similar to the fetch routines, except that SWW(segment write word) is used. Then a loop counter, R[count], is decremented and the loop repeated if the counter is not equal to zero. This general microprogram takes 13 cycles + action time per loop for 16 bit data and 19 cycles + action time for 32 bit data. Action time refers to the number of cycles taken by the action firmware microprogram. Setup time in the format routine required 26 cycles. An even more general microprogram combining scalar and vector versions of a DLR format was written, but its performance was unacceptably slow since loop overhead was twice that of figure 3-4.

A different approach, cf. figure 3-5, uses further run time "compilation" to a specific DLR loop for each precision. Size specific data fetch is in now incorporated into the vector control loop. This requires slightly more microstore space, but

improves performance. This technique yields an execution time of 8 cycles + action time per loop for 16 bit data and 14 cycles plus action time for 32 bit data. Thus we pay a penalty of up to ~50% for generality. Inefficiency in the general algorithm stems from the necessity in MK16 to reload SR for each precision test. Freeing the status register also allows us to move the counter incrementation and gain a cycle, although this only works if the action function does not sample the zero flag.

Another possible solution with a minor change to the microarchitecture is to dedicate fields in SR for left, right, destination tags and the arithmetic flags. This technique would result in a loop execution time of 8 cycles + action time. This method requires a change to the microarchitecture to allow any bit in the SR to be tested. This method also has a problem in that SR may not be able to hold all precision tags if many data sizes are used. A separate bit is required for each precizion,

VLOOP16

| С | DMU vector control loop for inti6 diadic action                                               |

|---|-----------------------------------------------------------------------------------------------|

| С | R[CNT] is loaded by calling program                                                           |

|   | LOOP:                                                                                         |

|   | R[LINDX]<-INC2 SRW R[LINDX]                                                                   |

| , | DB[L0]<-S[WORD] $\Delta$ "memory fetch"                                                       |

|   | R[RINDX]<-INC2 SRW R[RINDX]                                                                   |

|   | DB[R0] < -S[WORD]                                                                             |

|   | EXEC R[OP]                                                                                    |

|   | R[DINDX] < INC2 SWW R[DINDX]                                                                  |

|   | $\rightarrow$ =>ERROR IF OVFL $\triangle$ S[WORD]<=DB[D0] $\triangle$ R[CNT]<=SNZ DEC1 R[CNT] |

| ÷ | ->LOOP IF ¬ZERO $\Delta$ "Continue loop if zero flag is not set"                              |

|   | return                                                                                        |

|   | ERROR: CALL 'RECOVER'                                                                         |

|   | return                                                                                        |

Figure 3-5: Size Specific Dyadic Vector control Microprogram.

since an IF microop is used to test data size. Sequential tests are needed to decode data size, but these were combined with data fetches so they did not increase loop time. Initial loading of SR is slowed since tags must be shifted and combined with SR. This increases setup time unless OVU hardware is used for this function.

It is important at this stage to weed out delays due to minor idiosyncracies in the microarchitecture since apparent speedups from other architectural changes could simply be due to masking the effects of these idiosyncracies when each processor has less to do in an algorithm. Therefore fixed precision routines are used for further study, and the problem of code compaction is left to be solved when a complete system is implemented.

# 3.1.2 Memory streaming

It should be possible to speed up sequential memory accesses. The simulator was modified to measure the advantages of such a technique. Vector instructions should execute faster since bus address cycles are no longer needed. Memory interface hardware can be designed to provide data streaming capability. Stream buffers are provided between the data bus and memory. Data bus transfers proceed at 8 or 16 bits per cycle, while transfers from memory to stream buffers use wider data paths. The memory system can use interleaving or the new nibble mode chips to support extra bandwidth. The width required depends on

the ratio of memory cycle time to processor cycle time. Once started, a memory stream no longer requires bus address cycles. Pipelining in the memory interface hides address translation time delays. A memory stream interface was designed and incorporated into SAM 1 and could have been added to SAM 0.5 if desired. The code segment in figure 3-6 shows the use of streaming in a typical vector loop for a diadic action.

#### VLOOP16

Initialize counter Left stream address <- zero Right stream address <- zero Dest stream address <- zero LOOP: DB[left] <- SSN left DB[right] <- SSN right EXEC action inc count Δ dest SDN DB[result] ->loop if count ≠0

Figure 3-6: Dyadic Vector Loop with Memory Streaming.

Two new microoperations, SSN and SDN, support read and write streaming respectively. Memory transactions take only one cycle if streams were previously initialized. Loop time is reduced to 5 cycles + action time for 16 bit data and 8 cycles + action time for 32 bit data.

Matrix multiplication should be faster using algorithm (a) using normal memory fetching. Streaming should equalize the two algorithms, unless nonsequential fetches require more than 2 cycles, in which case algorithm (b) becomes faster. The standard interface for dyadic action routines caused some difficulty in implementing matrix multiply. The addition routine leaves the accumulated sum in DB[D] but this register will be overwritten by the next multiply action. This means that the sum must be saved elsewhere and restored within each loop. This was done, keeping the sum on the data stack, DS. This slows performance, but not significantly, since execution time is dominated by multiply time. The problem could be resolved by defining a special accumulate action that uses different registers but this would not work for a general inner product.

For a general Matrix Multiply which accepts any size data, Tinnerloop was 24 cycles plus action time for 16 bit data and 35 cycles plus action time for 32 bit data. A size specific version, cf. figure 3-7, was run resulting in an innerloop time of 13 cycles plus action time for 16 bit data and 21 cycles for 32 bit data. Although nearly twice as fast as the general microprogram, this routine still has a lot of overhead, mostly due to moving the running sum from DB to DS and back. Supporting a combined multiply accumulate action solves the problem but only for the specific matrix multiply. This technique saves 6 cycles for 16 bit data and 10 cycles for 32 bit data. Streaming reduced loop time by one cycle for 16 bit data and 3 cycles for 32 bit data.

.35

#### DOTA16

```

DMU int16 Dot Product control microprogram computes

С

inner prod of N by K matrix (A) with K by M matrix (B)

C

С

DB[OP] contains left action of dot

DB[OP2] contains right action

С

Initial values are loaded by format microprogram

С

LOOP1:

R[COL] <- R[M]

LOOP2:

AR <-NEGATE R[COL] "R[COL] counts cols down from R[M]"

AR < -R[M] PLUS AR

AR <-LSHIFT AR.0

"Convert to word offset"

R[RINDX] < -R[RA] PLUS AR

R[COUNT] < -R[K] \Delta PUSH

INNERLOOP:

R[LINDX] <- INC2 SRW R[LINDX]

AR <-DEC1 R[M] \Delta DB[L0] <-S[WORD]

R[RINDX] <- INC2 SRW R[RINDX]

AR \leftarrowLSHIFT AR, 0 \triangle DB[R0]\leftarrowS[WORD]

EXEC DB[OP2] \Delta R[RINDX] <-R[RINDX] PLUS AR

\rightarrow ERROR IF OVFL \triangle AR \leftarrow DB[D0]

DB[R0] < -AR

AR <-DS[R0]

DB[L0] < -AR

EXEC DB[OP]

\rightarrow ERROR2 IF OVFL \triangle AR \rightarrow DB[D0]

R[COUNT] \leq SNZ DEC1 R[COUNT]

\rightarrow INNERLOOP IF \neg ZERO \triangle DS[R0] \leftarrow AR

R[DINDX] <-- INC2 SWW R[DINDX]

AR \leq -R[K] \Delta POP \Delta S[WORD] \leq -DB[D0]

AR <-LSHIFT AR,0

R[LINDX] <--R[LINDX] MINUS AR

R[COL] \le SNZ DEC1 R[COL]

-> LOOP2 IF ¬ZERO

R[LCOUNT] <- SNZ DEC1 R[LCOUNT]

-> LOOP1 IF ¬ZERO

return

ERROR: CALL 'RECOVER'

"Mul error"

FPROR2: CALL 'RECOVER'

"Add error"

return

Figure 3-7: Size Specific Dot Product Control Microprogram

using Algorithm (a).

```

In theory, algorithm 1(b) requires only two sequential memory fetches per loop, since A[i,k] is constant within the inner loop. However the standard action interface again causes problems. A[i,k] cannot be held in DB[L] during the loop because it will be overwritten by the C value read in for the addition part. As in algorithm 1(a) the constant may be moved to a temporary location and restored or a new accumulate action can be defined. Again the data stack was used, cf. figure 3-8. DOTB16 C \DMU int16 Dot Product control microprogram computes (inner prod of N by K matrix (A) with K by M matrix (B) С C DB[OP] contains left action of dot **DB**OP2] contains right action C Initial values are loaded by format microprogram С LOOP1: R[COL] <- R[K] $R[RINDX] < -R[RA] \Delta PUSH$ LOOP2: R[LINDX] <- INC2 SRW R[LINDX]  $R[COUNT] < -R[M] \Delta DS[L0] < -S[WORD]$ **INNERLOOP:** DB[L0] < -DS[L0]R[RINDX]<-INC2 SRW R[RINDX] DB[R0]<-S[WORD] EXEC DB[OP2]  $\rightarrow$  ERROR IF OVFL  $\triangle$  AR < -DB[D0]DB[R0] < -ARSRW R[LINDX] DB[L0] < -S[WORD]EXEC DB[OP]  $\rightarrow$  ERROR IF OVFL  $\triangle$  R[COUNT] < SNZ DEC1 R[COUNT] R[DINDX] <-INC2 SWW R[DINDX]  $\rightarrow$  INNERLOOP IF  $\neg$  ZERO  $\triangle$  S[WORD]  $\leftarrow$  DB[D0] AR < -R[M]AR <-LSHIFT AR,0 R[DINDX] < -R[DINDX] MINUS AR $R[COL] \le SNZ DEC1 R[COL]$ -> LOOP2 IF 7ZERO R[LCOUNT] <-SNZ DEC1 R[LCOUNT]  $\rightarrow$  LOOP1 IF  $\neg$ ZERO  $\triangle$  R[DINDX]  $\langle -R$ [DINDX] PLUS AR return ERROR1: CALL 'RECOVER' "Multiply overflow" ERROR2: CALL 'RECOVER' "Add overflow" return

Figure 3-8: Size Specific Dot Product Control Microprogram using Algorithm (b). This size specific version of algorithm b gives an innerloop time of 12 cycles plus action time for 16 bit data. A 32 bit version takes 21 cycles plus action time. Streaming will reduce loop time by 2 cycles for 16 bit data and 4 cycles for 32 bit data, but necessitates separate read and write destination streams.

# 3.1.3 Analysis of results

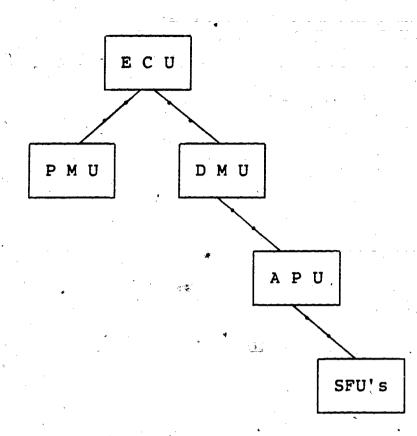

During the simulation of system one, timings of the different phases of instruction execution were determined. These results, cf. figure 3-9, give an estimate of the workload of the different processes which may later be executed by separate processors. These results point out the primary bottlenecks in system performance. For vector addition, most of the time was spent in the setup and fetch phases. The dyadic scalar addition microprogram takes 3 cycles for 16 bit data and 6 cycles for 32 bit data. For multiplication, the balance swings to the action phase because of the slowness of multiplication on MK16. The multiplication microprogram takes 32 to 48 cycles for 16 bit data and ~200 cycles for 32 bit data. A VLSI functional multiplier equalizes addition and multiplication times so both cases will approximate the results from addition in systems 2 and 3.

In order to maximize system performance, processor workloads need to be balanced. All overhead is due to fixed # setup time. This can be reduced with hardware support for the

Figure 3-9:Workload Distribution of Vector Add)

verification phase. A special operand verification unit (OVU) is being designed for this purpose[42]. Since memory fetch comprises the major component of DMU execution time during vector loops, memory streaming can be used to reduce fetch time. With memory streaming, fetch plus store and action phases are nearly equal for addition, so introduction of an extra processor could almost double performance if these operations are done in parallel.

While benchmark 2 execution time is dominated by multiply time, cf. figure 3-10, DMU overhead is significant even for the innerloop - 40% for the general version and 25% for the size specific microprogram. For small arrays, outer loops add even more overhead. If multiply time is reduced significantly by

Figure 3-10:Workload Distribution of Benchmark 2

Solid area of overhead, |##|, indicates fixed setup time. Shaded area, |//|, indicates action time if multiply time = add time. using a hardware multiplier, DMU overhead becomes a system bottleneck. An unexpected result of this study was that algorithm (b) was faster than algorithm (a) even without memory streaming. From figure 3-10, it appears that this is due to the higher overhead of algorithm (a), which requires complex address calculations in both the inner and outer loops.

The results presented in this section were parameterized into DMU loop time and action time. The results can be used to determine maximum cycle times for an arithmetic unit so that the system is not slowed.

3.2 System 2

In system 2, it is assumed that a combinational chip set is used to support actions. Support for vector action routines requires changes to the DMU instruction hierarchy. When a format program finds from operand tags that a vector action is required, it must determine if a specific vector action microprogram is available. In the SAM 0.5 simulation, a simple local memory table lookup is used. A more complete discussion is given in section 4.2. Two variations of the DMU-SFU interface are considered to see how they affect structure and performance. They are ordered according to increasing SFU control complexity.

In the simplest configuration, cf. figure 3-11 (a), limited cabability functional units are attached to the external data and control buses. To simplify the figure these are shown as a single bus. Each unit contains its own data buffer and status register. SFU's can have up to 16 registers selectable under microprogram control. Read or write of a selected register is enabled by the control bus. With this method only a simple finite state machine is needed to control each of the functional units. If each unit performs actions of varying precision, then a tag buffer (possibly part of IR) will be needed to control the unit. Otherwise a separate unit is needed for each action precision pair. DMU needs to know which unit is being loaded, thus requiring a specific vector loop for each action,

Figure 3-11: System 2 Configurations.

i.e. VADD16, VADD32, VMUL16 ...

In this configuration, DMU decodes the function code and then uses appropriate functional units to perform the required action, cf. figure 3-12. Action can be started by sending an action code to a functional unit, e.g. DBA [IR] <- 'add16'. Unfortunately, APL does not allow assignment to or subscripting of a function, so equivalent code was used in the simulation,

e.g. STARTADDER  $\Delta$  DBAIR <- 'add16'. Another method is to use a SFU control bit to indicate action

#### VMUL16

```

C DMU vector control loop for int16 diadic Multiply

R[CNT] is loaded by calling program,

C

LOOP:

R[LINDX] <-- INC2 SRW R[LINDX]

DBM[L0] < -S[WORD]

"memory fetch"

R[RINDX] <-- INC2 SRW R[RINDX]

DBM[R0] < -S[WORD]

DBM[IR] <- 'mul16'

NOP

R[DINDX]<-INC2 SWW R[DINDX]

SR<-DBM[SR]

\rightarrow ERR IF OVFL \triangle S[WORD] < DBM[D0] \triangle R[CNT] < SNZ DEC1 R[CNT]

->LOOP IF ¬ZERO

"Continue loop if zero flag is not set"

return

ERR: CALL 'RECOVER'

return

```

Figure 3-12: Size Specific Vector Multiply Microprogram.

start, e.g. DBAS [R0] <- SSN right.</pre>

This saves a bus cycle since the last data fetch can be combined with function start but may double the number of addresses needed for each functional unit if a conventional symmetric addressing convention is used. Again, equivalent code was needed in the simulation,

e.g. STARTADDER Δ DBA[R0] <- SSN right. The interface microprograms presented so far depend on a knowledge of SFU action time. They can be made more hardware independent by replacing the NOP's with the sequence

```

WAIT: SR<-DBM [SR]

```

In the second configuration shown in figure 3-11 (b), the functional units are on a separate bus with a common data buffer through which they communicate to the DMU data bus. A control

register DBIR is loaded by DMU. This register then selects the unit to perform the next action. Only one functional unit can be active at any time unless combined actions such as an inner product step are defined and implemented in an arithmetic unit. Since all dyadic primitives of a language may not be supported in hardware, DMU must either support a vector loop for each action as in the previous case or execute the action syllable to determine if the action is supported.

### 3.2.1 System 2 performance

We now look at DMU performance assumming a fast combinational arithmetic chip set is available.

The question arises of how best to use the slave. Even without attempting to overlap operations, performance is greatly improved for some functions supported by hardware. For example, the action part of the 16 bit multiply can be reduced to 1 cycle using a combinational logic chip from an average of 16 x 2.5 cycles using DMU firmware in system 1. Without overlap using the interface structure of figure 3-11 (a), a VADD16 or VMUL16 microprogram takes 9 cycles plus action time - 1 per loop for 16' bit data and 15 cycles plus action time - 1 for 32 bit data. Memory streaming reduces these times to 6 cycles plus action time for 16 bit data and 9 cycles plus action time for 32 bit data. Performance increases are due to increased chip area that can be dedicated to specific functions.

To increase performance further, we attempt to utilize the cycles when DMU is waiting for an arithmetic unit to finish by loading the next operands, cf. figure 3-13. Performance increases are greatest when fetch-store time and function time are approximately equal. With buffered output we can also store the previous result while waiting for the action to complete. Some extra hardware is required to support overlapping. First, the inputs must be double buffered since the old inputs must be available during the action phase. Therefore another set of registers must be available to accept the new operands. This will usually be part of an arithmetic chip. Data must be moved and latched before new data arrive. Since bus data movement takes place in the first half of a clock cycle after SFU control decoding, approximately 3/4 of a cycle or ~250 nsec is available to move the data if streaming is used and 1 3/4 cycles without streaming. A simple output latch is acceptable if the output is unloaded before a new action is started. However if we wish to overlap output storage with actions a double set of output registers is needed, since new results may be latched before the old outputs are unloaded. Some arithmetic units have an output latch built into the chip. This, along with the dual port data buffer, will suffice to support full overlapping.

With full overlap, the loop time for structure (a) is reduced to 9 cycles if action < 5 for 16 bit data and 15 cycles for action <10 for 32 bit data. With streaming, the corresponding times are 6 cycles if action < 2 and 9 cycles for

### VMUL16 DMU vector control loop for int16 diadic Multiply С R[CNT] is loaded by calling program DBM[L0]<-SSN left DBM[R0]<-SSN right DBM[IR] <- 'mul16' LOOP: DBM[L0]<-SSN left DBM[R0]<-SSN right WAIT: SR<-DBM[SR] : ->WAIT IF BUSY $DBM[IR] \leftarrow 'mul_16' \Delta R[CNT] \leftarrow SNZ DEC1 R[CNT]$ $\rightarrow$ ERROR IF OVFL $\Delta$ dest SDN DBM[D0] ->LOOP IF ¬ZERO Δ "Continue l'oop if zero flag is not set" WAIT1: SR<-DBM[SR] ->WAIT1 IF BUSY $\rightarrow$ ERROR IF OVFL $\triangle$ dest SDN DBM[D0] return ERROR: CALL 'RECOVER' return

Figure 3-13: Overlapped Vector Multiply Microprogram for structure (a).

action <5 for 32 bit data. If BUSY is also checked, as in figure 3-13, an extra cycle is required.

For structure (b), loop performance with individual action routines is the same as that of structure (a). If DMU EXEC's the action syllable, a general vector action microprogram can be used, in which case an extra cycle is needed. This saves microstore space and limits device specific actions to fewer action microprograms.

Matrix multiply was implemented using algorithm (a). Size specific versions were used to reduce the loop overhead found in the generic version in system 1. Performance without overlapping is similar to that on system 1, except that multiplication time is decreased. Overlapped performance will be considered next.

The use of slave action processors solved implementation problems for matrix multiply that occurred with a single processor DMU. With structure 3-11(a) there was no register contention since each unit has its own set of registers. There is still some overhead since results must be moved between units. Innerloop time was 16 cycles for 16 bit data if add and multiply time were less than 11 cycles and 24 cycles for 32 bit data if actions < 19 cycles.

Structure (b) is unable to support\_overlapping of multiplication with addition. Register contention is also a problem, so DS was used to hold intermediate results. Innerloop time for 16 bit data was 15 cycles if add time < 5 cycles and multiply time < 3 cycles.

Matrix multiply using algorithm (b) was also implemented using size specific microprograms. Structure (a) results in an innerloop time of 13 cycles for 16 bit data and 22 cycles for 32 bit data.

### 3.2.2 Analysis

System 2 is not much faster than system 1 for simple actions. This is due to synchronization overhead, which requires 2 or 3 cycles to initiate actions and copy SFU status to SR for testing. This is a great amount of overhead for short vector loops with simple actions and even more significant with memory streaming. A way to eliminate the overhead of testing the APU flags in (b) is to implement specific DMU control algorithms for

each action as in structure (a) and use knowledge of the APU performance to avoid testing for busy by assumming that the results are available after a fixed time. However, this links DMU algorithms to APU hardware reducing independence.

While slave processors relieved register contention problems for matrix multiply, some overhead was still incurred. The SFU addressing convention caused the overhead of data transfers in structure 10 (a) to be greater than necessary, since indirect data movement was necessary if differently numbered device registers were selected. This overhead could be reduced if inputs and outputs were addressed as separate SFUs. With structure (b), there is a register contention problem unless function control includes the ability to use any register for input or output to any functional unit. Then different registers can be used for the two functions. This would require a minimum of 4 interface registers (DB) for the benchmarks investigated in this thesis.

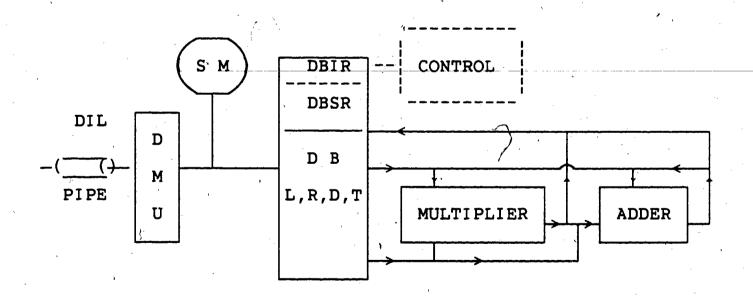

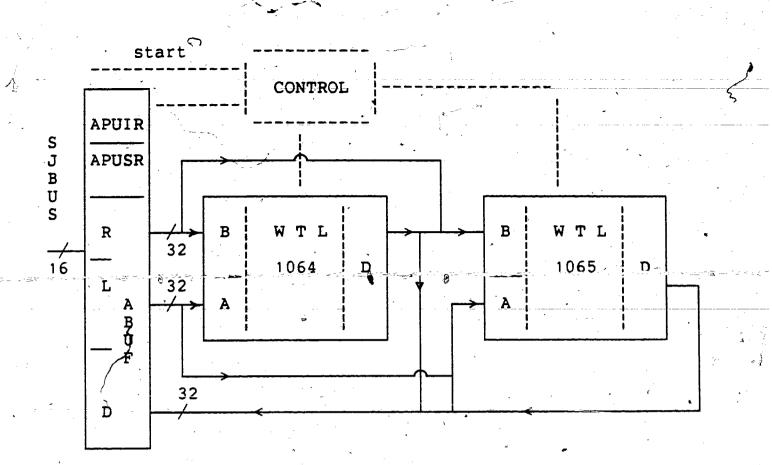

# 3.3 System 3

System 2 (b) can be enhanced to provide a pipelined multiply accumulate action, cf. figure 3-14. More complex control and extra data paths allow chaining of arithmetic units. DMU starts APU by loading an operation code into the APU instruction register. It can then test the APU status register to determine if the results are ready. APU should be able to perform all arithmetic primitives. Otherwise, actions need to be executed by DMU or special. Vector actions must be decoded during setup. For this study, only ADD, MUL, MULACC actions need be defined in pipelined and nonpipelined versions. A 2 stage pipeline is used to support overlapped vector processing.

# Figure 3-14: System 3 Architecture.

Performance of a general VLOOP16 microprogram, cf. figure 3-15, is 10 cycles for actions less than 2 cycles and 12 cycles for actions of 3 or 4 cycles. The destination address cycle is overlapped with APU operation. While this is adequate for short actions such as integer add (although there is little speedup over figure 3-5), there is very little overlap of DMU execution with APU action. An interesting observation of this microprogram is that performance can be optimized for short actions by adding NOP's before the statement labeled WAIT. For example, if a 16 bit addition took 2 cycles, an extra NOP before the WAIT would enable the loop to perform in 11 cycles instead of 13. Overlapping reduces loop time to 9 cycles for actions < 5. Memory streaming can reduce this to a 7 cycle loop with wait on action >4, cf. figure 3-16.

VLOOP16

| С | DMU vector control loop for int16 diadic Actions                   |   |

|---|--------------------------------------------------------------------|---|

| С | R[CNT] is loaded by calling program                                |   |

| , | LOOP:                                                              | f |

|   | R[LINDX]<-INC2 SRW R[LINDX]                                        |   |