### **Fault-Tolerance in Multi-Computer Networks**

by

### CHAU, Siu-Cheung

### B.Ed., University of Lethbridge, 1983 M.Sc., Simon Fraser University, 1984

### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

### Doctor of Philosophy

### in the School

#### of

### Computing Science

### © CHAU, Siu-Cheung 1989 SIMON FRASER UNIVERSITY August 1989

All rights reserved. This thesis may not be reproduced in whole or in part, by photocopy or other means, without the permission of the author.

# Approval

Name:

Siu-Cheung Chau

Degree:

Doctor of Philosophy

Title of Thesis:

Fault-Tolerance in Multi-Computer Networks

Dr. Pavol Hell, Chairman

Dr. Artnur L. Liestman, Senior Supervisor

Dr. Jøseph Peters, Supervisor

Dr. Ramesh Krishnamurti, Supervisor

Dr. Slawomir Pilarski

Dr. Frank Ruskey, External Examiner

18/7/89 Date Approved

#### PARTIAL COPYRIGHT LICENSE

I hereby grant to Simon Fraser University the right to lend my thesis, project or extended essay (the title of which is shown below) to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its users. I further agree that permission for multiple copying of this work for scholarly purposes may be granted by me or the Dean of Graduate Studies. It is understood that copying or publication of this work for financial gain shall not be allowed without my written permission.

#### Title of Thesis/Project/Extended Essay

Fault-Tolerance in Multi-Computer Networks.

Author:

| ( | S   | 1 | n | n | а | t |   | r | A | ١. |

|---|-----|---|---|---|---|---|---|---|---|----|

| • | . Э |   | ч |   | a |   | u |   | 0 |    |

Siu-Cheung Chau

(name)

Tuly 25, 198

### Abstract

Multi-computers connected in various architectures are now commercially available and are being used for a variety of applications. Some of the most commonly used architectures are the binary hypercube, the binary tree, cube-connected cycles, the mesh, and multistage interconnection networks. All of these architectures have the major drawback that a single processor or edge failure may render the entire network unusable if the algorithm running on the network requires that the topology of the network is maintained. The failure of a single processor or a link between two processors would destroy the topology of these architectures. Thus, some form of fault-tolerance must be incorporated into these architectures in order to make the network of processors more reliable.

While several fault-tolerance schemes have been proposed for specific architectures, these schemes are not general enough to provide fault-tolerance for other architectures. The goal of this thesis is to provide a more general approach that can be applied to several of these multi-computer network architectures with only minor modifications.

A general scheme for constructing fault-tolerant multi-computer networks is proposed which uses switching networks to inter-connect the processors of the network. Two such switching networks are described in the thesis. The scheme can be used to provide k fault-tolerance with k spare processors. It compares favorably with other proposed schemes for fault-tolerant multi-computer networks, achieving higher reliability while using at most the same amount of extra hardware.

A fault-tolerant multi-computer network constructed using the proposed scheme functions as if it was a non-redundant network. No extra control information is needed to ensure the fault-tolerant network functions properly. When a processor fails, the reconfiguring process can be initiated distributively. Fast context switching is provided to speed up reconfiguration. These properties together with the ability to provide high level of reliability for a long period of time make our scheme suitable for long-life unmaintained applications.

### To my wife Lily and my daughter Lilian

# **Table of Contents**

| Approval<br>Abstract<br>Dedication<br>Table of Contents<br>1. Introduction and Related Work<br>1.1. Introduction<br>1.2. Related Work<br>1.2.1. Binary Hypercube                                                                                                                                                                  | iii<br>v<br>vi<br>1 | 1<br>2<br>3<br>5<br>6            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------|

| Table of Contents         1. Introduction and Related Work         1.1. Introduction         1.2. Related Work                                                                                                                                                                                                                    | vi<br>1             | 2<br>2<br>3<br>5                 |

| 1. Introduction and Related Work<br>1.1. Introduction<br>1.2. Related Work                                                                                                                                                                                                                                                        | 1                   | 2<br>2<br>3<br>5                 |

| 1.1. Introduction<br>1.2. Related Work                                                                                                                                                                                                                                                                                            |                     | 2<br>2<br>3<br>5                 |

| 1.2. Related Work                                                                                                                                                                                                                                                                                                                 | 9                   | 2<br>2<br>3<br>5                 |

| <ul><li>1.2.2. Binary Tree</li><li>1.2.3. Cube-Connected Cycles</li><li>1.2.4. Multistage Interconnection Networks</li></ul>                                                                                                                                                                                                      | 9                   | •                                |

| 2. A General Fault-Tolerant Scheme for Multi-Computer Networks                                                                                                                                                                                                                                                                    | -                   |                                  |

| <ul> <li>2.1. Introduction</li> <li>2.2. Using Switching Networks to Construct Fault-Tolerant Networks</li> <li>2.3. Estimation of the Reliability of the Scheme</li> <li>2.4. Type A Switching Network Design</li> <li>2.5. Type B Switching Network Design</li> <li>2.6. Distributed Reconfiguration</li> </ul>                 |                     | 9<br>10<br>15<br>16<br>21<br>26  |

| 3. Binary Hypercube Architecture                                                                                                                                                                                                                                                                                                  | 30                  |                                  |

| <ul> <li>3.1. Introduction</li> <li>3.2. Fault-Tolerant Scheme For Binary Hypercubes</li> <li>3.3. Generalized Scheme for Binary Hypercubes</li> <li>3.4. Reliability</li> <li>3.5. Global Sparing</li> </ul>                                                                                                                     |                     | 30<br>31<br>32<br>36<br>37       |

| 4. Binary Tree Architecture                                                                                                                                                                                                                                                                                                       | 44                  |                                  |

| <ul> <li>4.1. Introduction</li> <li>4.2. New Fault-Tolerant Scheme For Binary Trees</li> <li>4.3. Extension to <i>m</i>-ary Trees</li> <li>4.4. Comparison with Previous Schemes</li> <li>4.5. Modular Sparing</li> </ul>                                                                                                         |                     | 44<br>44<br>47<br>49<br>55       |

| 5. Cube-Connected-Cycles Architecture                                                                                                                                                                                                                                                                                             | 58                  |                                  |

| <ul> <li>5.1. Introduction</li> <li>5.2. New Fault-Tolerant Scheme for Cube-Connected-Cycles</li> <li>5.3. Reliability Estimate of the Scheme</li> <li>5.4. Comparison with Previous Schemes</li> <li>5.5. Global Sparing for Cube-Connected Cycles</li> <li>5.6. Comparing Global Sparing with other Proposed Schemes</li> </ul> |                     | 58<br>58<br>59<br>60<br>62<br>65 |

| 6. Multistage Interconnection Networks                                 | 68 |    |

|------------------------------------------------------------------------|----|----|

| 6.1, Introduction                                                      |    | 68 |

| 6.2. New Fault-Tolerant Scheme For Multistage Interconnection Networks |    | 69 |

| 6.3. Reliability Estimation of the Scheme                              |    | 70 |

| 6.4. Extension to Cover Switching Element Failures                     |    | 72 |

| 6.5. Reliability of the Extended Scheme                                |    | 75 |

| 6.6. Modular Sparing                                                   |    | 78 |

| 7. Conclusion                                                          | 83 |    |

| References                                                             | 85 |    |

|                                                                        |    |    |

# List of Tables

| Table 3-1: | Number of spares required for Rennels' basic scheme and our scheme to achieve the same level of reliability at time $t=0.05$ and $c=1$                                                                                                      | 39 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3-2: | Number of spares required for Rennels' hierarchical scheme and our scheme to achieve the same level of reliability at time $t=1$ and $c=1$                                                                                                  | 39 |

| Table 3-3: | Extra hardware required for global sparing and modular sparing with 2 fault-<br>tolerant modules having a reliability of at least 0.98 at $t=0.1$ and $c=1$                                                                                 | 42 |

| Table 3-4: | Extra hardware required for modular sparing with 4, 8, and 16 fault-tolerant modules having a reliability of at least 0.98 at $t=0.1$ and $c=1$                                                                                             | 43 |

| Table 4-1: | Hardware requirements for Lowrie and Fuch's SOFT scheme and our new scheme to achieve the same level of reliability at $t=0.2$                                                                                                              | 53 |

| Table 4-2: | Hardware requirements for Singh's scheme and our new scheme to achieve the same level of reliability at $t=0.2$                                                                                                                             | 53 |

| Table 4-3: | Hardware requirements for Howell and Agarwal's scheme and our new scheme to achieve the same level of reliability at $t=0.2$                                                                                                                | 54 |

| Table 4-4: | Hardware requirements for Howell and Agarwal's scheme and our new scheme to achieve a reliability of at least 0.98 at $t=0.4$                                                                                                               | 55 |

|            | The amount of extra hardware required to achieve the same level of reliability for the modular and for the global scheme at $t=0.4$                                                                                                         | 56 |

| Table 5-1: | The number of spares required to achieve the same level of system reliability<br>for Banerjee's modular sparing scheme and the global sparing scheme using<br>$\lambda=0.1$ , $t=0.1$ , $c=1$ and $h=d$ if d is even or $h=d+1$ if d is odd | 66 |

| Table 5-2: | The number of spares required to achieve the same level of system reliability for the new modular sparing scheme and the global sparing scheme at $t=0.2$ and $h=d$                                                                         | 67 |

| Table 6-1: | The system reliability of Jeng and Siegel's DR scheme and our new scheme with $k=2$                                                                                                                                                         | 73 |

| Table 6-2: | The system reliability of Jeng and Siegel's DR scheme and our new scheme<br>with one spare processor and one spare switching element per stage                                                                                              | 76 |

| Table 6-3: | The system reliability of our new scheme with different values of $k$ and $f$                                                                                                                                                               | 78 |

|            | The number of spare processors, $k$ , and spare switching element, $f$ , per stage                                                                                                                                                          | 79 |

|            | required to achieve a reliability of at least 0.98                                                                                                                                                                                          | ., |

| Table 6-5: | Extra hardware required for global sparing and modular sparing with 2, and                                                                                                                                                                  | 80 |

|            | 4 modules having the same level of reliability at $t=0.01$ and $c=1$                                                                                                                                                                        |    |

| Table 6-6: | Extra hardware required for global sparing and modular sparing using the                                                                                                                                                                    | 81 |

|            | extended scheme at $t=0.01$ and $c=1$                                                                                                                                                                                                       |    |

| Table 6-7: | Extra hardware required for global sparing and modular sparing using the extended scheme at $t=0.1$ and $c=1$                                                                                                                               | 82 |

# List of Figures

| Figure 1-1:         | A 3-dimensional binary hypercube                                                | 2  |

|---------------------|---------------------------------------------------------------------------------|----|

|                     | A cube-connected cycles with $h=4$ and $d=2$                                    | 6  |

|                     | A shuffle exchange network with 8 processors                                    | 7  |

| Figure 2-1:         | A switching network with <i>n</i> incoming links and $n+k$ outgoing links       | 10 |

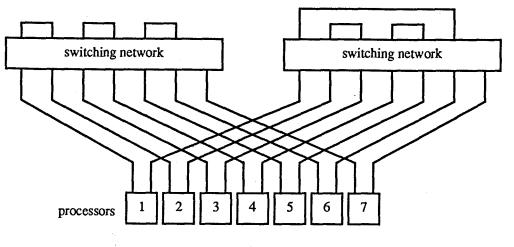

| Figure 2-2:         | Using switching networks to connect two fault-tolerant modules                  | 11 |

|                     | Using direct connection to construct a fault-tolerant cycle of six processors   | 12 |

| Figure 2-4:         | Connecting a cycle with 6 active processors and 1 spare processor using         | 13 |

|                     | two switching networks                                                          |    |

| Figure 2-5:         | Connecting a network with two cycles of six processors and two spare            | 15 |

|                     | processors using three switching networks                                       |    |

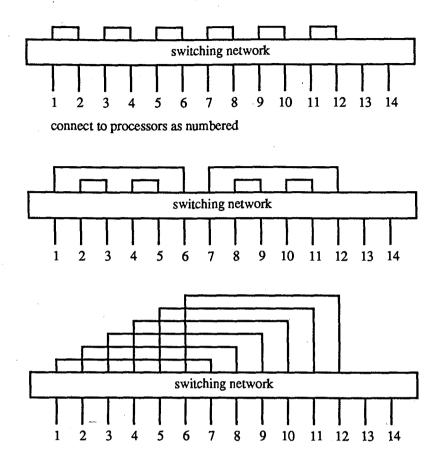

|                     | 3 decoupling networks arranged in 3 levels                                      | 17 |

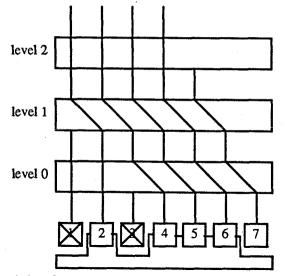

|                     | Connections after processor 3 has failed                                        | 18 |

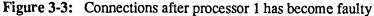

|                     | Connections after processor 1 and 3 have failed                                 | 19 |

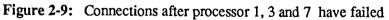

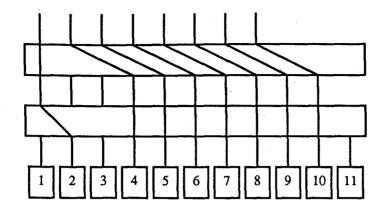

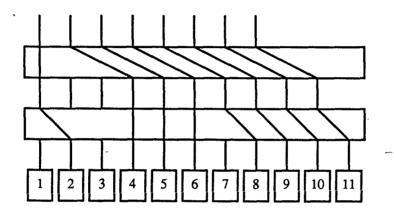

|                     | Connections after processor 1, 3 and 7 have failed                              | 19 |

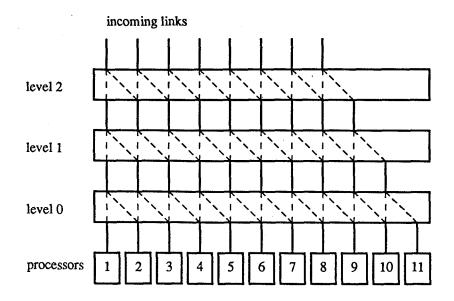

| <b>Figure 2-10:</b> | Connections after processor 3 has become faulty                                 | 22 |

| <b>Figure 2-11:</b> | Connections after processor 3 and 7 have become faulty                          | 23 |

| <b>Figure 2-12:</b> | Connections after processor 1, 3 and 7 have become faulty                       | 23 |

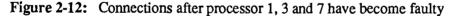

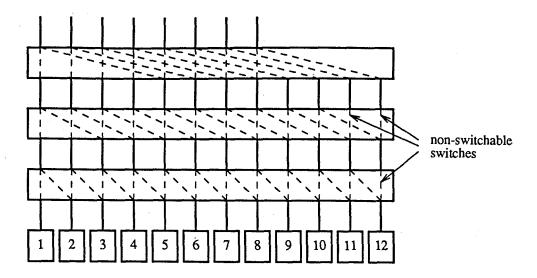

| <b>Figure 2-13:</b> | For $n=8$ and $k=4$ , some switches do not have to be switchable                | 27 |

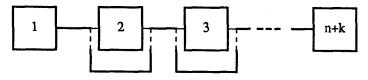

|                     | Connections between the processors                                              | 27 |

|                     | A fault-tolerant module with k spares                                           | 31 |

|                     | Connections after processor 3 has become faulty                                 | 33 |

|                     | Connections after processor 1 has become faulty                                 | 33 |

|                     | Connections after processor 5 has become faulty                                 | 34 |

| Figure 3-5:         | Using 2 Type A switching networks to form a fault-tolerant 2-dimensional        | 34 |

| _                   | binary hypercube                                                                |    |

| Figure 3-6:         | Using 3 Type A switching networks to form a fault-tolerant 3-dimensional        | 35 |

|                     | binary hypercube                                                                |    |

| Figure 3-7:         | System reliability of Rennels' scheme with 369 spares and our scheme with       | 40 |

|                     | 43 spares for $n=8$                                                             |    |

|                     | A fault-tolerant 3-level binary tree with 1 spare                               | 45 |

|                     | A 2-fault-tolerant 3-level binary tree                                          | 46 |

| Figure 4-3:         | Connections in the fault-tolerant 3-level binary tree with 2 spares after       | 47 |

|                     | processor 3 has become faulty                                                   |    |

| Figure 4-4:         | Connections in the fault-tolerant 3-level binary tree with 2 spares after       | 48 |

|                     | processors 3 and 7 have failed                                                  |    |

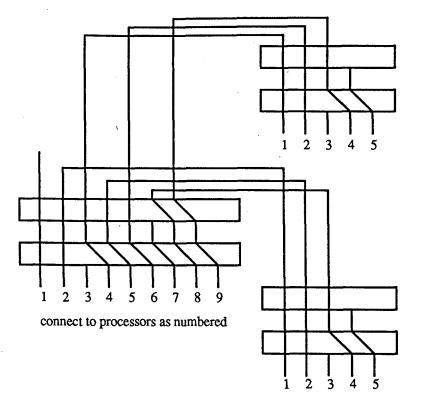

|                     | A fault-tolerant 2-level 3-ary tree with 1 spare                                | 49 |

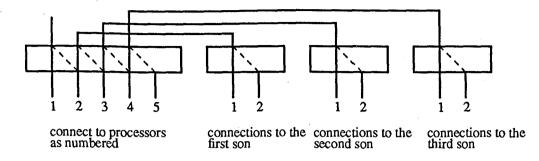

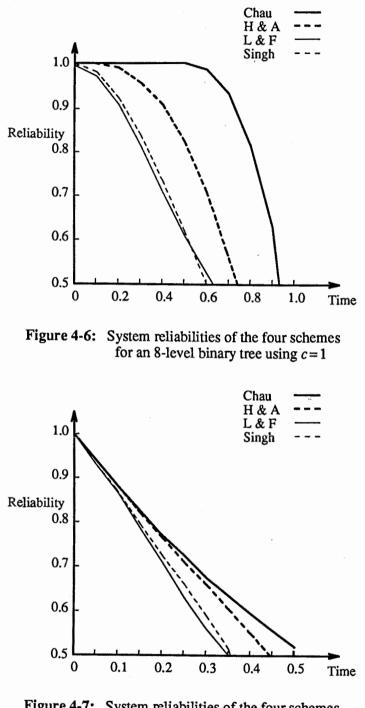

| Figure 4-6:         | System reliabilities of the four schemes for an 8-level binary tree using $c=1$ | 51 |

| Figure 4-7:         | System reliabilities of the four schemes for an 8-level binary tree using       | 51 |

|                     | c=0.95                                                                          | 51 |

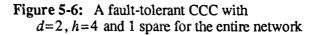

| Figure 5-1:         | A fault-tolerant cycle with k spares                                            | 59 |

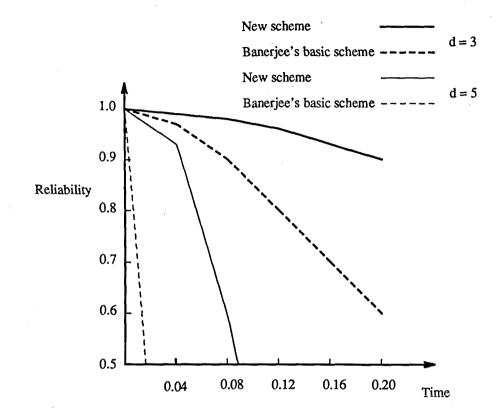

|                     | Comparing system reliability of Banerjee's basic scheme and our scheme          | 61 |

|                     | with $d=3$ and $h=8$ , and $d=5$ and $h=32$                                     | ~  |

|                     |                                                                                 |    |

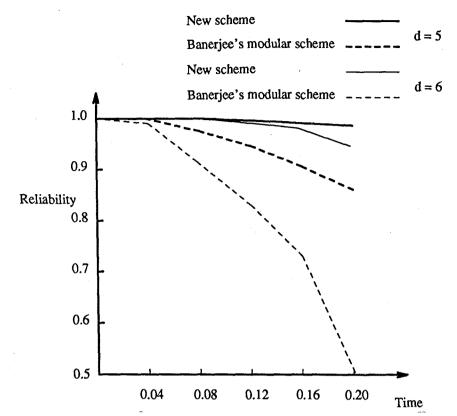

| Figure 5-3: | Comparing system reliability of Banerjee's modular scheme using $g=h/2$<br>and our scheme with $d=5$ and $h=6$ , and $d=6$ and $h=8$ | 62 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5-4: | Using 2 Type A switching networks to connect 4 processors together to form a cycle                                                   | 63 |

| Figure 5-5: | Connecting 10 processors into 2 cycles with 5 processors each using 3 switching networks                                             | 64 |

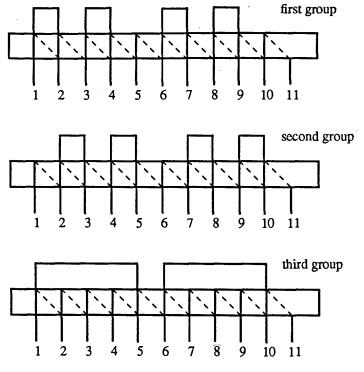

| Figure 5-6: | A fault-tolerant CCC with $d=2$ , $h=4$ and 1 spare for the entire network                                                           | 65 |

|             | A multistage interconnection network                                                                                                 | 69 |

| Figure 6-2: | A fault-tolerant multistage interconnection network                                                                                  | 70 |

| Figure 6-3: | A shuffle exchange network with 8 processors                                                                                         | 74 |

| Figure 6-4: | The connection between 4 groups of switching networks                                                                                | 74 |

x

# Chapter 1

### **Introduction and Related Work**

### **1.1. Introduction**

Multi-computers connected in various architectures are now commercially available and are being used for a variety of applications. Some of the most commonly used architectures are the binary hypercube, binary tree, cube-connected cycles, mesh, and multistage interconnection networks. All of these architectures have the major drawback that a single processor or edge failure may render the entire network unusable if the algorithm running on the network requires that the topology of the network does not change. The failure of a single processor or the failure of a link between two processors would destroy the topology of these architectures. Thus, some form of fault-tolerance must be incorporated into these architectures in order to make the network of processors more reliable.

Several fault-tolerance schemes have been proposed which can only be applied to a particular architecture. These proposed schemes are not general enough to provide fault-tolerance for any architecture. The goal of this thesis is to propose a more general fault-tolerant approach that can be applied to several of these multi-computer network architectures with only minor modifications. This scheme described in Chapter 2, provides higher reliability than the previously proposed schemes using at most the same amount of hardware. The scheme also allows distributed reconfiguration. Chapters 3 through 6 describe how the scheme can be used to produce fault-tolerant versions of particular topologies. Chapter 3 shows how the scheme can be applied to binary hypercubes. Chapter 4 describes how to apply the scheme to binary trees. Chapter 5 describes how to apply the scheme to cube-connected cycles networks. Finally, Chapter 7 is a brief summary of the results.

#### **1.2. Related Work**

#### 1.2.1. Binary Hypercube

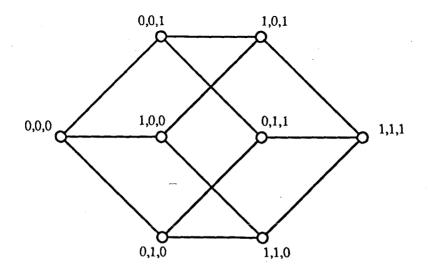

A d-dimensional binary hypercube contains  $n=2^d$  processors with each processor connected to d other processors. Each processor can be represented by a d-tuple  $(b_{d-1},...,b_0)$  where the  $b_i$ 's are either 0 or 1. Two processors are connected together if their tuples differ in exactly one position. Figure 1-1 shows a 3-dimensional binary hypercube with each processor in the hypercube being labeled by its 3-tuple.

Figure 1-1: A 3-dimensional binary hypercube

Hastad, Leighton and Newman [8] proposed a scheme that allows degradation and does not require the use of redundant spare processors. This scheme includes a distributed reconfiguration algorithm. With high probability, this algorithm can reconfigure a *d*-dimensional binary hypercube to a (*d*-1)-dimensional binary hypercube provided that processors are faulty with probability  $p \le 0.5$  and that the faults are independently distributed. However, communication between neighboring processors in the *d*-1-dimensional binary hypercube may require routing through other active or non-active processors. That is, the communication time between "neighboring" processors in the cube may be increased. Furthermore, there may be congestion since a particular link may be used for communication between many pairs of "neighboring" processors.

Rennels [15] proposed a scheme that uses spare processors for the reconfiguration. For systems that do not require very high reliability, he proposed a basic scheme which divides a *d*-dimensional binary hypercube with  $2^d$  processors into  $2^s$  subcubes. Each subcube has  $2^m$  processors where d=s+m. A spare processor is used to back up the processors in each subcube. Since the spare processor may be required to replace any processor in the subcube, the spare processor is connected to every processor in the subcube and each of their neighbors in the other subcubes. Two crossbar switches are employed for each spare processor to realize the necessary connections. The first crossbar has  $2^m + s$  inputs and *d* outputs. The second one has  $2^m$  inputs and *s* outputs. Each crossbar requires a few thousand gates to implement. Each processor also requires an extra port in order to connect to the crossbar switches. For long-life unmaintained systems where very high reliability is required, Rennels proposed a second, hierarchical approach. In this scheme, a spare processor is hooked up to each subcube of four processors via a high speed bus. The approach is applied recursively. For example, a spare group of five processors (one spare and four active) is used to back up four groups of five processors via a high bandwidth bus. This multi-level redundancy method provides high reliability.

In Chapter 3, new fault-tolerant binary hypercube architectures are proposed. In Section 3.1, we propose a new modular fault-tolerant scheme for binary hypercubes where each module has 4 active processors and k spare processors. The scheme is generalized in Section 3.2 so that each fault-tolerant module has  $2^m$  active processors where  $0 \le m \le d$  and d is the dimension of the binary hypercube. In Section 3.3, we calculate the reliability of the proposed scheme. In Section 3.4, we compare the reliability of our generalized scheme with those of previously proposed schemes.

#### 1.2.2. Binary Tree

Raghavendra, Avizienis and Ercegovac [14] proposed a level oriented scheme which uses one spare processor per level of the binary tree and can tolerate one fault per level. This scheme uses a structure which is very similar to the optimal one fault-tolerant binary tree constructed by Kwan and Toida [11]. Instead of using direct connections between the spares and the other active

processors, they use two decoupling networks as switches to provide the appropriate connections. The lower levels of a large tree will have many nodes. In order to increase the reliability of the lower levels, this level oriented scheme can be applied to modules consisting of  $k=2^i$  nodes of a given level. A single spare is provided for each module and the switches in the decoupling networks are controlled centrally through a host computer that uses the binary tree.

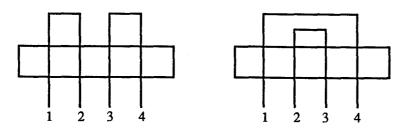

Hassan and Agarwal [7] also proposed a modular scheme for fault-tolerant binary trees. Their approach uses fault-tolerant modules as building blocks to construct a complete binary tree. Each fault-tolerant module consists of four processors, three active and one spare. Soft switches provide connections between the active processors, the spare, and the rest of the tree. A distributed approach to reconfiguration is used in that the soft switches can be set locally in each module when failure occurs.

Both the level oriented scheme (with or without modules at the lower level) and the modular approach provide only one spare per level (or module). Thus, the reliability that can be achieved by these schemes is insufficient for systems requiring very high reliability. Singh [16] suggested an improvement to Hassan and Agarwal's modular scheme by allowing the sharing of spares across module boundaries and allowing more than one spare per module. He showed that his scheme is best suited for binary trees having 31 to 255 nodes.

For larger binary trees, Howells and Agarwal [9] devised a modular scheme that allows more than one spare per module. Each module in their scheme is a subtree. For example, a 10-level binary tree may be split into one 5-level subtree containing the root and 32 5-level subtrees. Each nonroot subtree is a fault-tolerant module with its own spares. Each spare in a module may replace any active processor in the entire module. Each spare is connected to every processor in the subtree through direct links to each processor, soft switches, and three buses. Two of these buses are used to connect to the children of the processor being replaced and the last bus is used to connect to the parent. This technique cannot be used for the subtree containing the root node since its leaf nodes must be connected to the root nodes of the other fault-tolerant non-root subtrees. Fortunately, the subtree containing the root node can employ other schemes to provide fault-tolerance. Besides

improving reliability, both Singh's and Howells and Agarwal's schemes also improve the yield for binary trees implemented in a single chip.

Lowrie and Fuchs [12] also proposed a subtree oriented fault-tolerance (SOFT) scheme which they show to be better than the schemes of Raghavendra, Avizienis and Ercegovac and of Hassan and Agarwal. In their scheme, up to  $2^t$  spares, where  $0 \le t \le d-2$ , are connected to the leaf nodes of a *d*-level binary tree. The number of connections between a spare and the leaf nodes depends on *t*. An extra link is also used to connect the two children of a non-leaf node together. When a node becomes faulty, one of its children, *s*, will take over its task through the use of soft switches. The task of *s* will be taken over in turn by one of its children. This process is repeated until a spare takes over the task of a leaf node. The subtree oriented fault-tolerance scheme can also be extended to an *m*-ary tree.

Chapter 4 concentrates on the binary tree architecture. In Section 4.2, we propose a new scheme for binary trees which is extended in Section 4.3 for m-ary trees. In Section 4.4, we compare the reliability and hardware costs of our proposed scheme with those of previous schemes. In Section 4.5, we compare both the reliability and hardware costs of variants of our scheme.

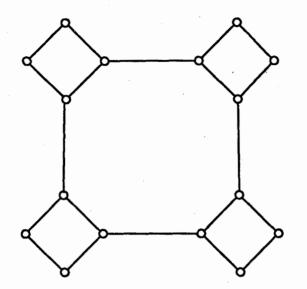

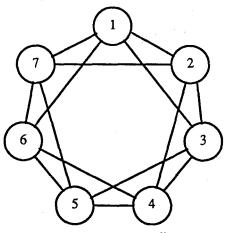

#### **1.2.3.** Cube-Connected Cycles

Cube-connected cycles, proposed by Preparata and Vuillemin [13], consist of  $n=h2^d$  processors with  $h \ge d$ . This structure is easily obtained by replacing each vertex of an *d*-dimensional binary hypercube with a cycle of *h* processors, distributing the *d* edges incident on each vertex of the hypercube among the vertices of the corresponding *h* cycles. Figure 1-2 shows a cube connected cycle with h=4 and d=2.

Banerjee, Kuo and Fuchs [2], and Banerjee [3] proposed two fault-tolerant schemes for cubeconnected cycles. The basic scheme uses one redundant cycle to back up all of the cycles in the network. In this scheme, an extra port is required for every processor in order to connect the spare cycle to the rest of the network. For systems requiring higher reliability, they proposed a modular scheme which provides spares for each cycle and uses a local reconfiguration scheme to tolerate

Figure 1-2: A cube-connected cycles with h=4 and d=2

multiple faults within a cycle. The processors in each cycle are divided into subgroups and a spare is provided for each subgroup. Soft switches are used to provide connections between the spares and the rest of the cycle.

Chapter 5 presents new fault-tolerant cube-connected cycles architectures. In Section 5.2, we propose a new modular scheme for cube-connected cycles. This scheme is extended in Section 5.3 so that the entire cube-connected-cycles network can be regarded as a single fault-tolerant module. In Section 5.4, we calculate the reliability of the proposed schemes. In Section 5.5, we compare both the reliability and hardware costs of our proposed schemes with those of previous schemes. In Section 5.6, we compare the two variants of our scheme.

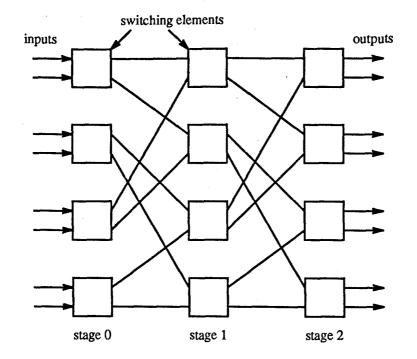

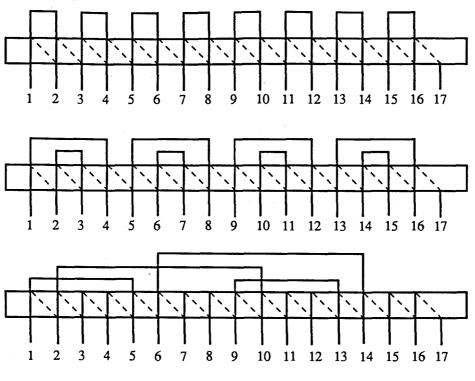

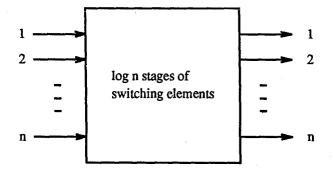

#### **1.2.4.** Multistage Interconnection Networks

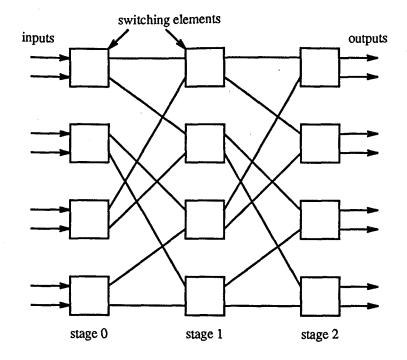

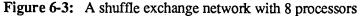

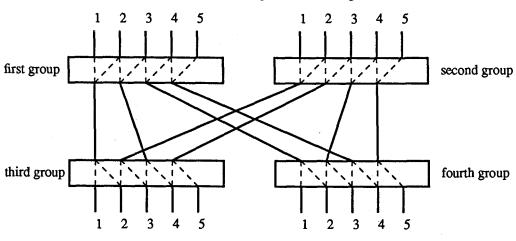

A multistage interconnection network (MIN) architecture can be characterized as having  $n=2^m$  processors connected together by *m* stages of switching elements such that a processor in a MIN can be connected to any other processor through the *m* stages of switching elements. Some of the common multistage interconnection networks are the shuffle exchange network, the baseline network, the Omega network and the generalized cube. Figure 1-3 shows a shuffle exchange network with 8 processors.

Figure 1-3: A shuffle exchange network with 8 processors

Most previous work (see [1]) in the area of fault-tolerant multistage interconnection network architectures has been based on increasing the reliability of the network connections, ignoring processing element failures and concentrating only on the switching element failures. For systems with a large number of processing elements, it is also important to consider processing element failures in order to achieve high reliability for the entire system. Jeng and Siegel [10] proposed a fault-tolerant multistage interconnection network architecture called the Dynamic Redundant (DR) network that can tolerate processing element failures as well as switching element failures by using spare processors and switches. The DR network is based on a generalized cube network. A generalized cube network with  $n=2^m$  processors uses  $\log_2 n$  stages where each stage consists of n switching elements connected by n links to the previous stage. The DR network with n active processors and k spares has the same number of stages, however each stage has n+k switching elements rather than n. Each stage is connected to the previous stage using 3(n+k) links. A DR network can tolerate any single processor failure or any single switching element failure. It can, in fact, tolerate k faults provided that the faults all occur in adjacent rows. Jeng and Siegel show that

a DR network with more than one spare is no better than a DR network with one spare due to the limited coverage on multiple faults.

In Chapter 6, new multistage interconnection network architectures are proposed. In Section 6.2, we propose a new fault-tolerant scheme for multistage interconnection networks with k spare processors which can tolerate any k processor failures. In Section 6.3, we compare our scheme with Jeng and Siegel's DR scheme. The scheme is extended in Section 6.4 so that it can cover both processor failures and switching element failures. In Section 6.5, the extended scheme is compared to Jeng and Siegel's DR scheme. In Section 6.6, we compare the reliability and hardware requirements of two variants of the extended scheme.

# Chapter 2

# A General Fault-Tolerant Scheme for Multi-Computer Networks

### **2.1.** Introduction

Our goal is to provide fault-tolerance in a multi-computer network by adding spare processors which can be used to replace failed processors. In particular, we want to design a method to connect spare processors to an existing network in such a way that the network topology can be maintained when a spare processor replaces a failed processor. One obvious approach is to connect each spare to all the processors in the network using large cross-bar switches. This is not feasible for large networks. In order to overcome this problem, the entire network can be divided into modules such that each spare is used to back up the processors within a particular module. The fault-tolerant modules are then connected together to form the network. Since a spare can be used to back up any processor in the module which may be connected to processors outside of the module, the spare must be able to connect to those external processors. These connections may be realized with smaller cross-bar switches. Although large cross-bar switches are not needed in this scheme, the number of spares required to provide the same level of system reliability increases as the number of processors in a module decreases. Thus, there is a trade off between the module size and the size of the cross-bar switches required by this approach.

Rather than using spares to back up an entire module, we can use the spares to back up only a very small number of processors. These processors, in turn, can be used to back up other active processors in the module. This process can be repeated until every processor is backed up. With this approach, cross-bar switches can be avoided entirely.

We propose a new interconnection method in Section 2.2 which uses switching networks instead

of cross-bar switches to connect fault-tolerant modules together. These networks can also be used to provide connections within a module. The approach can also be used so that the entire network is realized as a single fault-tolerant module. In Section 2.3, reliability estimates for our schemes are given. The switching networks used in our interconnection method are described in Sections 2.4 and 2.5. Finally, a distributed reconfiguration scheme is given in Section 2.6.

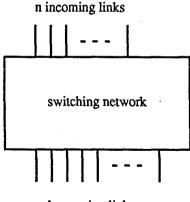

### 2.2. Using Switching Networks to Construct Fault-Tolerant Networks

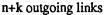

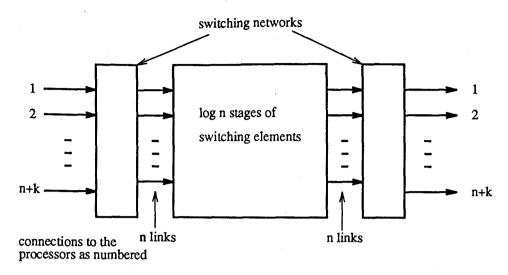

In constructing fault-tolerant networks, we will require a switching network with *n* incoming and n+k outgoing links as shown in Figure 2-1. In particular, let  $\alpha_1, \alpha_2, ..., \alpha_n$  be a sequence such that  $1 \le \alpha_1 < \alpha_2 < ... < \alpha_n \le n+k$ . We want to design a switching network which allows the *n* incoming links to be connected to any such sequence  $\alpha_1, \alpha_2, ..., \alpha_n$  of outgoing links so that incoming link *i* is connected to outgoing link  $\alpha_i$ . The detailed design of such switching networks is described in Sections 2.4 and 2.5.

### Figure 2-1: A switching network with *n* incoming links and n+k outgoing links

In describing the construction of fault-tolerant networks, we use the term **active processor** to denote all the processors that participate in the execution of tasks.

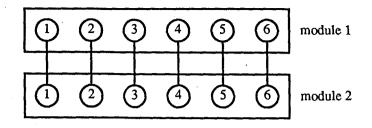

Let us, for the moment, assume that we can construct a fault-tolerant module with n active processors and k spare processors which functions correctly provided that no more than k processors fail within the module. Consider a network consisting of two fault-tolerant modules.

Conceptual network - 6 processors in module 1 connected to 6 processors in module 2

fault-tolerant network - 6 active processors in module 1 connected to 6 active processors in module 2

Figure 2-2: Using switching networks to connect two fault-tolerant modules

Each module initially contains 6 active processors (numbered 1 through 6) and one spare processor (numbered 7) and the *i*<sup>th</sup> active processors of each module are connected by a link. We now describe how to connect one module to the other using switching networks. Let  $\alpha_1, \alpha_2, ..., \alpha_6$  be the numbers of the active processors in a module, ordered so that  $1 \le \alpha_1 < \alpha_2 < ... < \alpha_6 \le 7$ . Incoming links 1, 2, 3, ..., 6 can be routed to any such sequence of processors  $\alpha_1, \alpha_2, ..., \alpha_6$ , respectively by using a switching network with 6 incoming links and 7 outgoing links (see Figure 2-2). Each outgoing link of the switching network is connected to a processor in the module. Each incoming link is connected to a communication line that leads to the other module. Initially, these 6 communication lines are connected to processors 1 through 6. When one of these processors

fails, the switching network resets the connections so that the failed processor is disconnected and the 6 communication lines are routed to 6 non-faulty processors. For example, if processor 5 fails, processor 6 will be connected to communication line 5 and the spare processor (7) will be connected to communication line 6. In this simple example, each processor is connected to only one processor in another module. Additional switching networks could be utilized to allow multiple external connections.

Figure 2-3: Using direct connection to construct a fault-tolerant cycle of six processors

Now, we turn our attention to the connections within a given fault-tolerant module. Continuing with our example, we would like to construct a fault-tolerant 6 cycle. In particular, the 6 initially active processors must form a cycle by connecting processor *i* to processor i+1, for  $1 \le i < 6$  and processor 6 to processor 1. The fault-tolerant module is designed so that processor  $i(1 \le i \le 6)$  is "backed up" by processor i+1. That is, if processor *i* fails (or is called upon to replace yet another processor) then processor i+1 can replace processor *i*. To allow for these processors to replace each other in the event of a failure, additional connections must be added. One method to do this, which we call *direct connection*, is to connect processor *i* to i+2 for  $1 \le i \le 5$  and processor 7 to processor 1, 2 and 6 (see Figure 2-3). One drawback of this method is that the number of ports per processor must increase with the number of spares. A second method is to use two cross-bar switches to connect the spare processor(s) to the cycle. As the number of spares becomes large, this method also becomes infeasible. A third approach which uses switching networks does not require the number of ports to increase with the number of spares and is described below.

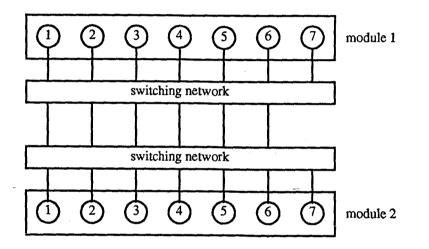

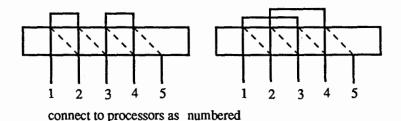

The connections between the processors in a module can be provided by connecting the incoming links of several groups of switching network. In our particular example, the connections between the processors within a module can be provided by two switching networks with 6 "incoming" and 7 "outgoing" links. In this case, the 7 processors of the module are connected to the "outgoing" links while the "incoming" links are connected to each other. One switching network is used to connect processor i to processor i+1 for  $1 \le i \le 6$  where i is odd. The second connects processor i to processor i+1 for  $1 \le i \le 5$  where i is even and processor 6 to processor 1. With these connections, the processors connected to the 6 "incoming" links form a cycle of six processors. The connections are shown in Figure 2-4. If processor 5 fails, processor 6 will take over the task of faulty processor 5 and the spare processor 7 will take over the task of processor 6. The switching networks can be set to bypass processor 5. In particular, "incoming" links 5 and 6 are reset to connect to "outgoing" links 6 and 7, disconnecting "outgoing" link 5. The details of this process are explained in Sections 2.4 and 2.5. After reseting the switching network, processors 1, 2, 3, 4, 6, and 7 form a cycle of six processors, connected through the switching networks. This same technique can be used to form different structures within the module as illustrated in Chapters 3, 4, 5, and 6.

Figure 2-4: Connecting a cycle with 6 active processors and 1 spare processor using two switching networks

By using switching networks to provide connections between processors within a module and

connections between modules, a fault-tolerant multi-computer network can be constructed as described above. We call this scheme modular sparing. In the above example, each spare can be used to replace any of 6 processors within its own module. Thus, the system can tolerate any single failure. It can also tolerate two failures if they occur in different modules. In order to tolerate any two failures in the network, we could use the above techniques to construct a single module containing 12 active processors (divided into 2 cycles of 6 processors each) and 2 spare processors. We call this scheme global sparing.

As an example of global sparing, we show in Figure 2-5 an alternate implementation of the above example. As before, we want 2 cycles of 6 active processors and we allow 2 spare processors. Three switching networks are required to provide the connections. The first two switching networks are used to connect the processors to form two cycles of six processors using the same connection scheme as described above for providing connections for a cycle of six processors. The processors connected to "incoming" links 1 to 6 and 7 to 12 of both switching networks form two cycles of six processors respectively. Finally, the third switching network is used to connect the two cycles together.

Using global sparing, k spares in the network can tolerate any k faults. Thus, it is optimal in the number of faults that any network with a given number of spares can tolerate. With global sparing, it is possible to achieve the same level of reliability as with modular sparing and other proposed schemes for various multi-computer network architectures as shown in Chapters 3, 4, 5, and 6 while using significantly fewer spares. However, for networks with a large number of active processors, it may not be possible to implement the entire network on a single wafer. Smaller modules may be used to split a large network into fault-tolerant modules which can each be implemented on a wafer.

Figure 2-5: Connecting a network with two cycles of six processors and two spare processors using three switching networks

### 2.3. Estimation of the Reliability of the Scheme

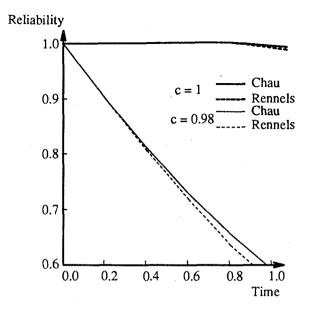

Consider a fault-tolerant multi-computer network constructed using global sparing which contains n active processors and k spares. In our reliability analysis, we consider only processor failure. We do not consider the failures in the switching networks. These failures could be covered by duplicating the switching networks. Other types of failures, such as fault-detection failures and recovery failures, are accounted for by the coverage factor [17] which is defined to be the probability that a failure is detected and the recovery is successful. If reconfiguration fails due to one of these failure types, the entire system is considered to be unreconfigurable.

Let c be the coverage factor, k the number of spare processors in the network, n the number of

active processors in the network,  $r=e^{-\lambda t}$  the reliability of a single processor (where  $\lambda$  is a constant representing the failure rate of a processor over time t and t is time expressed in millions of hours), and  $R_k$  the reliability of a fault-tolerant network with k spare processors using global sparing. The reliability of a non-redundant network  $R_0$  is  $r^n$ . For k=1, the probability that the spare is needed is equal to the probability that an initially active processor has failed which is  $\binom{n}{1}r^{n-1}(1-r)$ . The probability that a particular spare processor is reliable and can be switched successfully is rc. Thus, the additional reliability with one spare is  $rc\binom{n}{1}r^{n-1}(1-r)$  and the reliability  $R_1$  is  $R_1 = r^n + \binom{n}{1}r^n(1-r)c = R_0 + \binom{n}{1}r^n(1-r)c$ . For k=2, the second spare is only used when there are exactly two faulty processors among the n initial active processors and the first spare. The probability that this occurs is  $\binom{n+1}{2}r^{n-1}(1-r)^2c$ . Thus, the reliability with two spares is  $R_2 = R_1 + \binom{n+1}{2}r^n(1-r)^2c^2$ .

For arbitrary k,

$$R_{k} = R_{k-1} + \binom{n+k-1}{k} r^{n} (1-r)^{k} c^{k} = \sum_{i=0}^{k} \binom{n+i-1}{i} r^{n} (1-r)^{i} c^{i}.$$

The reliability of a network using modular sparing can be calculated similarly. Let m be the number of active processors in each module,  $RM_{m,k}$  be the reliability of a module with k spares in each module, and  $R_{p,m,k}$  be the reliability of a network with p modules each having m active processors and k spares.

$$RM_{m,k} = RM_{mk-1} + {\binom{m+k-1}{k}} r^m (1-r)^k c^k = \sum_{i=0}^k {\binom{m+i-1}{i}} r^m (1-r)^i c^i.$$

$$R_{p,m,k} = (RM_{m,k})^p.$$

### 2.4. Type A Switching Network Design

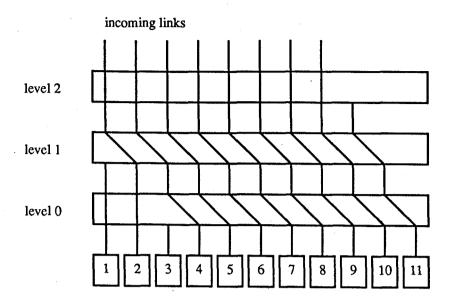

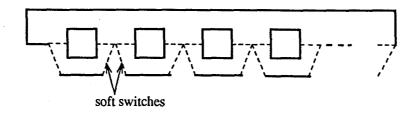

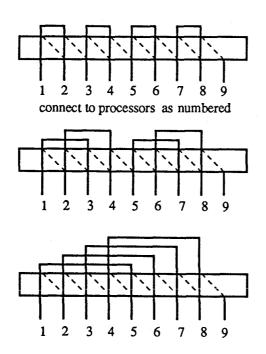

A Type A switching network can be implemented using a group of decoupling networks. The group of decoupling networks maps n incoming links (numbered 1 to n) to n+k outgoing links (numbered 1 to n+k). Each outgoing link is connected to a processor. The use of decoupling networks has previously been proposed for other fault-tolerant multi-computer network architectures [14, 4, 5, 6]. Figure 2-6 shows the connections for a group of 3 decoupling networks arranged in three levels as a Type A switching network.

Figure 2-6: 3 decoupling networks arranged in 3 levels

The levels of each group of decoupling networks are numbered from 0 to l-1 with level 0 connecting to the outgoing links and level l-1 connecting to the incoming links. Each level contains at most n+k-1 switches numbered from 1 to n+k-1. The j<sup>th</sup> switch in level l-1 connects to the j<sup>th</sup> incoming link. It can be set to connect the j<sup>th</sup> incoming link to either the j<sup>th</sup> switch on level l-2 or to the (j+1)<sup>st</sup> switch on level l-2. In general, the j<sup>th</sup> switch on the i<sup>th</sup> level can be set so that it is connected to either the j<sup>th</sup> switch on level i-1 or to the (j+1)<sup>st</sup> switch on level i-1 or to the (j+1)<sup>st</sup> switch on level i-1 or to the (j+1)<sup>st</sup> switch on level i-1. The j<sup>th</sup> switch on level 0 can connect to either the j<sup>th</sup> outgoing link or the (j+1)<sup>st</sup> switch j on level i>0 is set to connect to switch j on level i-1. Switch j on level 0 is initially set to connect to outgoing link j.

Outgoing link *i* is connected to processor *i*. At any given time, *n* processors are active. We denote the active processors as  $\alpha_1, ..., \alpha_n$  with  $\alpha_1 < \alpha_2 < ... < \alpha_n$  such that  $\alpha_1$  is the number of the lowest numbered active processor and  $\alpha_n$  is the number of the highest numbered active processor. In particular,  $\alpha_i = j$  indicates that processor *j* is the *i*<sup>th</sup> active processor.

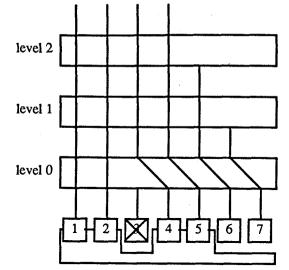

When a processor fails, the failed processor has to be disconnected from the network and the spare has to be connected. As an example of the reconfiguration process, consider a module with 8

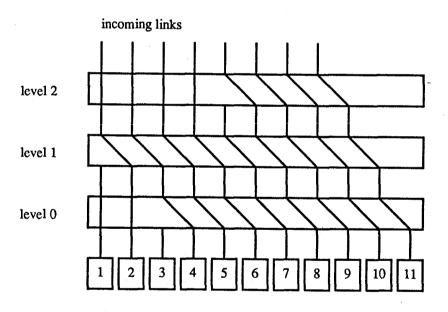

active processors and 3 spare processors. If processor 3 fails, the switch in level 0 of the decoupling network that connects to processor 3 and all the switches to the right of it are switched to the right. In this way, processor 3 is disconnected and the first spare processor (9) is activated. Processor i+1 assumes processor i's previous role where  $3 \le i \le 8$ . At this point,  $\alpha_1=1$ ,  $\alpha_2=2$ , and  $\alpha_i=i+1$ , for  $3 \le i \le 8$ . The new connection for one group of decoupling networks is shown in Figure 2-7. If another processor fails subsequently, another reconfiguration must occur. The switch in level 1 of the decoupling network that connects to the failed processor and all the switches to the right of it are switched to the right. Figure 2-8 shows the structure as further modified after processor 1 becomes faulty and is replaced. In this figure,  $\alpha_1=2$ , and  $\alpha_i=i+2$ , for  $2 \le i \le 8$ . Finally, Figure 2-9 shows the result of processor 7 failing subsequently and is replaced. After reconfiguration,  $\alpha_1=2$ ,  $\alpha_2=4$ ,  $\alpha_3=5$ ,  $\alpha_4=6$ , and  $\alpha_i=i+3$ , for  $5 \le i \le 8$ .

Figure 2-7: Connections after processor 3 has failed

Consider one such k level decoupling network connected to n active processors and k spares. Let *i* be the number of processors that have failed previously, where  $0 \le i \le k$ . If another active processor fails, the reconfiguring is done by switching the switch in level *i* that connects to the failed processor and all switches of the same level to the right of it one position to the right. For example, if the switches in level *i* are numbered 1 to n+k-i-1 from left to right and switch *j*

Figure 2-8: Connections after processor 1 and 3 have failed

connects to the newly failed processor, then the reconfiguration consists of switching the switches from j to n+k-i-1 at level i to the right. By doing so, the faulty processor is disconnected from the network, the spare processor immediately to the right of the rightmost active processor becomes an active processor, and the structure is re-established.

A Type A switching network consists of k decoupling network arranged in k levels. Incoming link i can be connected to any outgoing link j if  $j-i \le k$  as shown in Lemma 1. Lemma 1 and other subsequent Lemmas described below are used to establish that a Type A switching network can be used to replace up to k faulty processors with spares.

Lemma 1: In a Type A switching network, incoming link i  $(1 \le i \le n)$  can be connected to any outgoing link j where  $(i \le j \le i+k)$

**Proof:** Let m=j-i. At each level  $l, 0 \le l \le m$ , set switch number i+m-l-1 and all switches in that level to the right of switch i+m-l-1 to the right. This connects incoming link *i* to outgoing link *j*.  $\Box$

Let  $\alpha_1, \alpha_2, ..., \alpha_n$  be a sequence such that  $1 \le \alpha_1 < \alpha_2 < ... < \alpha_n \le n+k$ . If the *n* incoming links can be connected to any such sequence  $\alpha_1, \alpha_2, ..., \alpha_n$  of outgoing links so that incoming link *i* is connected to outgoing link  $\alpha_i$  for  $0 \le i \le n$ , a Type A switching network can be used to replace any group of up to *k* faulty processors with spares. In order to show that this is the case, we first prove Lemma 2 which shows that a Type A switching network can be used to connect incoming links *i* and p (p > i) to outgoing links *j* and q ( $q > j, q-p \ge j-i$ ), respectively so that the paths do not intersect.

Lemma 2: In a Type A switching network, if incoming link *i* is connected to outgoing link *j* and incoming link p (p > i) is connected to outgoing link q (q > j), and  $q-p \ge j-i$ , the switches used to connect *i* to *j*, and the switches used to connect *p* to *q* are all different.

**Proof:** Let  $s_l$  be the switch used in level l to connect i to j and let  $t_l$  be the switch used in level l to connect p to q. Since p > i, in level k-1,  $t_{k-1} > s_{k-1}$ . If  $s_{k-1}$  is switched to the right, then  $t_{k-1}$  is also switched due to the reconfiguration scheme. Thus, in level k-2,  $t_{k-2} > s_{k-2}$ . The same argument can be repeated until level 0 is reached. Hence,  $t_l > s_l$  for  $0 \le l \le k-1$ .

Theorem 3: Let  $\alpha_1, \alpha_2, ..., \alpha_n$  be a sequence such that  $1 \le \alpha_1 < \alpha_2 < ... < \alpha_n \le n+k$ . The *n* incoming links of a Type A switching network can be connected to any such sequence  $\alpha_1, \alpha_2, ..., \alpha_n$  of outgoing links so that incoming link *i* is connected to outgoing link  $\alpha_i$  for  $0 \le i \le n$ .

**Proof:** From Lemma 1, incoming link *i* can be connected to  $\alpha_i$  for  $1 \le i \le n$ . From Lemma 2, there will be no common switch used to connect incoming link *i* to outgoing link  $\alpha_i$  and incoming link i+1 to outgoing link  $\alpha_{i+1}$  for  $1 \le i \le n-1$ . Thus, the theorem is proved.

For a Type A switching network with *n* incoming links and n+k outgoing links, a level *i* decoupling network must have n+k-i-1 switches. Thus, a Type A switching network has a total of  $\sum_{j=1}^{k} (n+k-i) = k(2n+k-1)/2$  switches. For large *k*, the number of switches required for a Type A switching network increases rapidly. The hardware required to implement the switches may make this design infeasible. Furthermore, *k* levels of decoupling networks are used to add *k* spares. When *k* is large, the switching delay may be significant. Hence, a Type A switching network is not suitable when *k* is large. The next section presents a different design which requires a lot fewer switches and introduces less switching delays when *k* is large. However, when *k* is small, the simplicity of a Type A switching network makes it easier to implement than other more complicated designs.

### 2.5. Type B Switching Network Design

For large k, we propose a different switching network design called Type B that uses fewer decoupling networks and switches than Type A. Instead of allowing the  $j^{\text{th}}$  switch of level i to be connected to the  $j^{\text{th}}$  switch or the  $(j+1)^{\text{st}}$  switch of level i-1, the  $j^{\text{th}}$  switch of level i may be connected to the  $j^{\text{th}}$  or the  $(j+2^{i})^{\text{th}}$  switch of level i-1. The  $j^{\text{th}}$  switch on level 0 can connect to either the  $j^{\text{th}}$  outgoing link or the  $(j+1)^{\text{st}}$  outgoing link. Initially, every switch j on level i > 0 is set to connect to switch j on level i-1. Switch j on level 0 is initially set to connect to outgoing link j. With this design, only  $l = \lceil \log_2(k+1) \rceil$  levels of decoupling networks are required to incorporate k spares.

The reconfiguring process of this design is slightly more complicated than for Type A. Consider

one such *l* level decoupling network connected to *n* active processors and *k* spares. As before, we number the levels from 0 to l-1, the processors from 1 to n+k, and the active processors from  $\alpha_1$  to  $\alpha_n$ .  $\alpha_i = j$  indicates processor *j* is the *i*<sup>th</sup> active processor. Initially  $\alpha_i = i$  for  $1 \le i \le n$ . When the first active processor fails, the reconfiguration process is the same as for Type A. The switch in level 0 that is connected to the failed processor and all the switches to the right of it are switched one position to the right. However, when subsequent failures occur, each remaining active processor and the spares used to replace the failed processors must determine which switches to use.

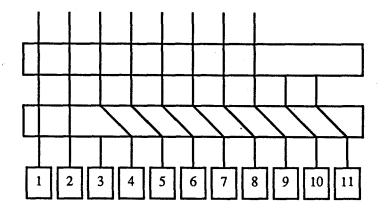

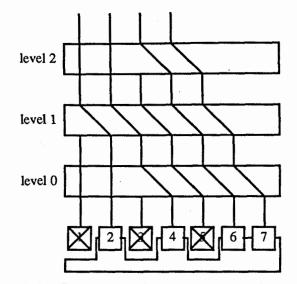

As an example, consider a module with 8 active processors and 3 spares. If processor 3 fails, the level 0 switch that connects to processor 3 and all the switches to the right of it are switched to the right. Processor 3 is disconnected from the incoming communication link to the decoupling networks. Processor *i* takes over the task of processor i-1, for i=4,...,9. Figure 2-10 shows the connections of the Type B switching network after processor 3 has failed. Figure 2-11 shows the structure as further modified after processor 1 fails and is replaced. Figure 2-12 shows the structure after processor 7 fails subsequently and is replaced.

Figure 2-10: Connections after processor 3 has become faulty

Suppose  $\alpha_i = j$ , the *i*<sup>th</sup> incoming link of the decoupling network should be connected to the *j*<sup>th</sup> outgoing link, that is, to the *j*<sup>th</sup> processor. In level l-1, the highest level, the *i*<sup>th</sup> switch connects to the *i*<sup>th</sup> incoming link. If  $j-i \ge 2^{l-1}$ , switch *i* will have to connect to the  $(i+2^{l-1})$ <sup>th</sup> switch of

Figure 2-11: Connections after processor 3 and 7 have become faulty

level l-2. Otherwise, no change is required and it remains connected to the  $i^{\text{th}}$  switch of level l-1. Let  $j-i=\sum_{m=0}^{l-1}a_m2^m$  where  $a_m$  is either 0 or 1 and  $l=\lceil \log_2(k+1) \rceil$ . If  $j-i \ge 2^{l-1}$ ,  $a_{l-1}=1$ . Otherwise,  $a_{l-1}=0$ . For level l-2, the switch used in the connection from incoming link i to processor j depends on whether the switch used in level l-1 is switched or not. This information can be obtained from the value of  $a_{l-1}$ . If  $a_{l-1}=1$ , the  $(i+2^{l-1})^{\text{th}}$  switch is used. Otherwise, the  $i^{\text{th}}$  one is used. That is, the switch used in level l-2 is the  $(i+a_{l-1}2^{l-1})^{\text{th}}$  switch. This switch is switch is switched to connect to the  $(i+a_{l-1}2^{l-1}+2^{l-2})^{\text{th}}$  switch in level l-3 if  $(j-i)-a_{l-1}2^{l-1} \ge 2^{l-2}$ . That is, if  $a_{l-2}=1$ . Otherwise, switching is not necessary. Hence, the switches used in the connection and the status of the switches used can be obtained from the equation  $j-i=\sum_{m=0}^{l-1}a_m2^m$  with  $a_l=0$  to simplify the formulas below. In particular,  $i+\sum_{m=u+1}^{l}a_m2^m$  switch in level u is

used to connect incoming link *i* to outgoing link *j* of the decoupling network. This switch is set to connect to the  $(i + \sum_{m=u}^{l} a_m 2^m)^{\text{th}}$  switch of level u-1 (or the  $(i + \sum_{m=u}^{l} a_m 2^m)^{\text{th}}$  outgoing link if u=0). With this switching scheme, the *n* incoming links of the  $l = \lceil \log_2(k+1) \rceil$  levels of decoupling networks can be connected to *n* non-faulty processors if the number of faulty processors is less than or equal to *k*. Furthermore, no two connections between an incoming link and an active processor share a common link or common switch.

In order to prove that the  $\lceil \log_2(k+1) \rceil$  levels of decoupling networks can be configured to handle any k processor faults, let  $\alpha_1, \alpha_2, ..., \alpha_n$  be a sequence such that  $1 \le \alpha_1 < \alpha_2 < ... < \alpha_n \le n+k$ . If the n incoming links can be connected to any such sequence  $\alpha_1, \alpha_2, ..., \alpha_n$  of outgoing links such that incoming link i is connected to outgoing link  $\alpha_i$  for  $0 \le i \le n$ , a Type B switching network can be used to replace any of up to k faulty processors with spares. In particular, incoming link i must be able to connect to any outgoing link j in the range  $i \le j \le i+k$ . This is proved in Lemma 4 below.

Lemma 4: In a Type B switching network incoming link i  $(1 \le i \le n)$  can be connected to outgoing link j for any j where  $i \le j \le i+k$ .

Proof: Since  $i \leq j \leq i+k$  and  $\sum_{m=0}^{l-1} 2^m \geq k$ , j-i can be expressed as  $\sum_{u=0}^{l-1} a_u 2^u$ , where the *a*'s are either 0 or 1 and  $\sum_{m=0}^{l-1} 2^m \geq \sum_{u=0}^{l-1} a_u 2^u$ . Using the connection scheme described above, incoming link *i* to the decoupling network is connected to outgoing link  $j=i+\sum_{u=0}^{l-1} a_u 2^u$ . Since  $i+\sum_{u=0}^{l-1} a_u 2^u \leq i+\sum_{m=0}^{l-1} 2^m$ , incoming link *i* can be connected to outgoing link *j*.  $\Box$

Lemmas 5 and 6 establish that if any incoming link *i* is connected to outgoing link *j*, where  $i \le j \le i+k$ , incoming link i+1 must be able to connect to any outgoing link *t* in the range  $j+1 \le t \le i+k+1$  with no sharing of switches and no sharing of links between these two connections. Lemma 5 is a technical lemma useful in proving Lemma 6.

Lemma 5: If  $\sum_{m=s}^{l} a_m 2^m > \sum_{m=s}^{l} b_m 2^m$  then  $\sum_{m=s}^{l} a_m 2^m - \sum_{m=s}^{l} b_m 2^m \ge 2^s$  where the *a*'s and *b*'s are either 0 or 1.

**Proof:** Let *l'* be the largest value  $l \ge l' \ge s$  such that  $a_{l'} \ne b_{l'}$ . Since we have assumed that  $\sum_{m=s}^{l} a_m 2^m > \sum_{m=s}^{l} b_m 2^m$  and all the *a*'s and *b*'s are either 0 or 1, it must be the case that  $a_{l'} = 1$  and  $b_{l'} = 0$ .

$$\begin{split} \Sigma_{m=s}^{l} a_{m} 2^{m} - \Sigma_{m=s}^{l} b_{m} 2^{m} &= \Sigma_{m=s}^{l'} a_{m} 2^{m} - \Sigma_{m=s}^{l'} b_{m} 2^{m}.\\ \Sigma_{m=s}^{l'} a_{m} 2^{m} - \Sigma_{m=s}^{l'} b_{m} 2^{m} &= 2^{l'} + \Sigma_{m=s}^{l'-1} a_{m} 2^{m} - \Sigma_{m=s}^{l'-1} b_{m} 2^{m}.\\ \text{Since } \Sigma_{m=s}^{l'-1} a_{m} 2^{m} &\ge 0 \text{ and } \Sigma_{m=s}^{l'-1} b_{m} 2^{m} &\le 2^{l'} - 2^{s}, \end{split}$$

$\sum_{m=s}^{l'} a_m 2^m - \sum_{m=s}^{l'} b_m 2^m \ge 2^s. \square$

Lemma 6: For a Type B switching network, if incoming link *i* is connected to outgoing link *j* and incoming link *p* (p > i) is connected to outgoing link *q*, where q > j $(q-p \ge j-i)$ , the switches used to connect *i* to *j*, and the switches used to connect *p* to *q* are all different.

**Proof:** Let  $j-i=\sum_{m=0}^{l-1} b_m 2^m$  and  $q-p=\sum_{m=0}^{l-1} a_m 2^m$ , where the *a*'s and *b*'s are either 0 or 1 and  $l=\lceil \log_2 k+1 \rceil$ . Thus,  $\sum_{m=0}^{l-1} a_m 2^m \ge \sum_{m=0}^{l-1} b_m 2^m$ . At each level *s*, the connection from *i* to *j* utilizes switch  $i+\sum_{m=s}^{l-1} b_m 2^m$  while the connection from *p* to *q* uses switch  $p+\sum_{m=s}^{l-1} a_m 2^m$ . These switches are clearly distinct if  $\sum_{m=s}^{l-1} a_m 2^m \ge \sum_{m=s}^{l-1} b_m 2^m$ .

Suppose that for a particular s,  $\sum_{m=s}^{l-1} b_m 2^m > \sum_{m=s}^{l-1} a_m 2^m$ . Since,  $\sum_{m=0}^{l-1} a_m 2^m \ge \sum_{m=0}^{l-1} b_m 2^m$ , therefore,  $\sum_{m=0}^{s-1} a_m 2^m - \sum_{m=0}^{s-1} b_m 2^m > \sum_{m=s}^{l-1} b_m 2^m - \sum_{m=s}^{l-1} a_m 2^m$ .  $\sum_{m=0}^{s-1} a_m 2^m - \sum_{m=0}^{s-1} b_m 2^m$  is at most equal to  $\sum_{m=0}^{s-1} 2^m = 2^s - 1$ . From Lemma 5,  $\sum_{m=s}^{l-1} b_m 2^m - \sum_{m=s}^{l-1} a_m 2^m$  is at least 2<sup>s</sup>. A contradiction occurs and hence the lemma is proved.  $\square$

Theorem 7: Let  $\alpha_1, \alpha_2, ..., \alpha_n$  be a sequence such that  $1 \le \alpha_1 < \alpha_2 < ... < \alpha_n \le n+k$ . The *n* incoming links of a Type B switching network can be connected to any such sequence  $\alpha_1, \alpha_2, ..., \alpha_n$  of outgoing links such that incoming link *i* is connected to outgoing link  $\alpha_i$  for  $0 \le i \le n$ .

**Proof:** The proof follows from Lemmas 4 and 6.  $\Box$

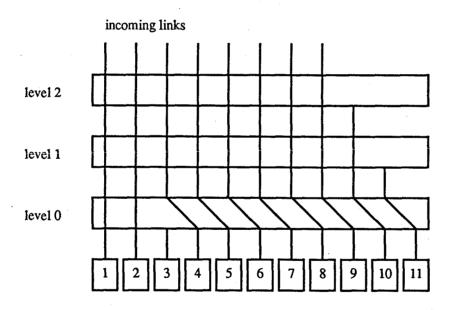

The number of switches required in each level of a Type B switching network depends on n and k. If processor n+k, the last spare, can be connected to the  $n^{\text{th}}$  incoming link of the decoupling networks, the switches in the decoupling networks are sufficient to connect any incoming link i,  $1 \le i \le n$ , to any outgoing link j,  $i \le j \le i+k$ . With this observation, the total number of switches in a group of decoupling network can be obtained. Let  $k = \sum_{m=0}^{l-1} a_m 2^m$ , where the  $a_m$ 's are either 0 or 1 and  $a_{l-1}=1$ . The level l-1 decoupling network has n switches which are connected to the n incoming links to the group of decoupling networks. The  $n^{\text{th}}$  switch can connect to either the  $n^{\text{th}}$  switch or the  $n+2^{l-1}$  switch in level l-2. Thus, the number of switches in level l-2 is  $n+a_{l-1}2^{l-1}$ . The last switch  $(n+a_{l-1}2^{l-1})$  in level l-2 is not required to connect to the  $n+2^{l-1}+2^{l-2}$  switch in level l-3 when  $a_{l-2}=0$ . In this case, not all of the switches have to be switchable. Figure 2-13 shows an example in which some switches do not have to be switchable. Hence, for level l-3, the number of switches is  $n+\sum_{m=l-2}^{l-1} a_m 2^m$ . Similarly, for level i, the number of switches is  $n+\sum_{m=l+1}^{l-1} a_m 2^m$ . With this number of switches, the  $n^{\text{th}}$  incoming link is able to connect to the last spare processor because  $k=\sum_{m=0}^{l-1} a_m 2^m$ . Thus, for a Type B switching network with  $l=\lceil \log_2 k+1 \rceil$  levels, the total number of switches is  $n+\sum_{m=1}^{l-1} ma_m 2^m$ .

# 2.6. Distributed Reconfiguration

Consider a module with *n* active processors and *k* spare processors. The n+k processors are connected to the n+k outgoing links of a switching network and are numbered 1 to n+k corresponding to the numbers of the outgoing links. The active processors are denoted by  $\alpha_i$ , for  $1 \le i \le n$ .  $\alpha_i = j$  indicates that processor *j* is the *i*<sup>th</sup> active processor. Initially,  $\alpha_i = i$  for  $1 \le i \le n$ .

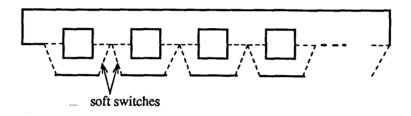

In order to provide fast context switching and distributed reconfiguration, processor *i* is connected to processor i+1, where  $1 \le i \le n+k-1$ , with soft switches used to bypass faulty

processors. Figure 2-14 shows the connections and soft switches between the processors. When a processor is non-faulty, a signal is sent to its switches to keep them open. We assume that the fault detection of each processor is concurrently performed by means of some on-line self-testing circuits. Thus, when a processor fails, it stops sending this signal and the processor to its right will be able to detect the failure and start the reconfiguration process.

Figure 2-14: Connections between the processors

When a processor  $\alpha_i = j$  fails, the network must be reconfigured to disconnect the faulty processor, connect a spare one and reassign tasks among the active processors. The non-faulty active processor  $\alpha_{i+1}$  immediately to the right of the faulty one initiates the reconfiguring process upon detecting that  $\alpha_i$  has failed. (If i=n, the lowest numbered spare processor *m* initiates the reconfiguration process.) It starts by taking over the task of the faulty one and informs the nonfaulty processor to its right about the starting of the reconfiguring process. Processor  $\alpha_{i+1}$ 's task is then taken over in turn by the non-faulty processor immediately to its right. This process is repeated until the spare processor *m* immediately to the right of the rightmost active processor  $(\alpha_n)$  becomes an active processor and takes over the task of its predecessor. That is, when processor  $\alpha_j$  fails, a sequence of task reassignments are performed until a non-faulty spare processor *m* which is connected to the processor  $\alpha_n$  is activated. First,  $\alpha_j$ 's task is taken over by  $\alpha_{j+1}$  and  $\alpha_{j+1}$  becomes active processor  $\alpha_j$ . This processor's old task is given to  $\alpha_{j+2}$  and  $\alpha_{j+2}$  becomes active processor  $\alpha_{j+1}$ . This continues until  $\alpha_n$  becomes active processor  $\alpha_{n-1}$ . Finally,  $\alpha_n$ 's old task is taken over by the spare processor *m* and *m* becomes  $\alpha_n$ .

The reassignment of tasks can be carried out efficiently through the connections between the processors if a parent-child relationship [18] is assumed between any two neighboring processors. The processor on the right assumes the role of the parent and keeps track of the state of its child. When a child fails, its parent can take over its task and can in turn inform its own parent of the reconfiguring process without any delay or rollback. For example, assuming that n=8, k=2 and  $\alpha_i=i$ , processor 10 is the parent of processor 9 initially and processor 9 is the parent of processor 8 and so on. That is, processor i+1 is the parent of processor 6 already has the current state of processor 5. The new child (processor 4) of processor 6 sends its current state to processor 6 and processor 6 informs its parent (processor 7) of the reconfiguration and sends its current state to its parent. This process is repeated until processor 9 takes over the task of processor 8 and sends its current state to its parent, processor 10. The above reconfiguring process can be carried out efficiently using the links between the non-faulty processors. The transfer of state information between the processors can be done almost simultaneously.

This scheme can only handle either a single fault at a time or multiple faults at the same time if the faults are not adjacent to each other. For multiple faults not adjacent to each other, the reassignment process is still quite efficient although the state of more than one processor may be transferred between the non-faulty processors. If adjacent faults occur simultaneously, the reassignment of tasks will take more time since the entire system may have to restart at the previous check point instead of being able to continue its operation without rollback. After the reassignment of tasks is completed, the switching networks must also be reset as described in Section 2.4 or Section 2.5 to replace the failed processors with spares. For a Type A switching network, the control of the decoupling networks can be implemented at each spare processor. The first spare controls the level 0 decoupling network and the *i*<sup>th</sup> spare controls the level *i*-1 decoupling network. For a Type B switching network, when processor *j* is required to take over the task of another processor to its right, it knows which active processor  $\alpha_i$  it will become and it also knows its own position. Thus, the values *i* and *j* are both known to processor *j*. Processor *j* calculates the coefficients  $a_m$  from the equation  $j-i=\sum_{m=0}^{l-1} a_m 2^m$  and determines which switches are used and which must be switched for the connection. This information is sent to the decoupling networks to establish the connection from incoming link *i* to processor *j*. This switching scheme can be carried out distributively by each affected processor. After both steps of the reconfiguration process (reassignment of tasks and reseting the switching network) have been completed, the network can resume its normal operation.

# Chapter 3

# **Binary Hypercube Architecture**

#### **3.1.** Introduction

In this chapter, fault-tolerant binary hypercube architectures are proposed. In Section 3.2, a fault-tolerant binary hypercube architecture is proposed which uses fault-tolerant modules as building blocks to realize a binary hypercube. The use of fault-tolerant modules has previously been proposed for use in fault-tolerant binary tree architectures [5, 7, 9, 16]. A fault-tolerant module contains four active processors and k spare processors configured so that each module can tolerate up to k faults. Let d be the dimension of a binary hypercube. In Section 3.3, we generalize the scheme so that each fault-tolerant module has  $2^m$  active processors,  $0 \le m \le d$ , and k spare processors. In Section 3.4, we calculate the reliability of the proposed scheme. With m=d, the entire binary hypercube is a single fault-tolerant module in which the k spare processors can be used to tolerate any k processor failures. In Section 3.5, we show that with this special case, it is possible to achieve the same level of reliability as with smaller modules while using significantly fewer spares. We compare this special case with Rennels' schemes. The new scheme is more reliable than Rennels' basic scheme since the latter can tolerate only a single fault within a given module. Even with fewer spare processors, our scheme achieves higher reliability than does Rennels' hierarchical approach. Furthermore, the amount of extra hardware required for our scheme to achieve the same level of reliability as Rennels' scheme is much less than that required by Rennels' scheme.

30

## **3.2.** Fault-Tolerant Scheme For Binary Hypercubes

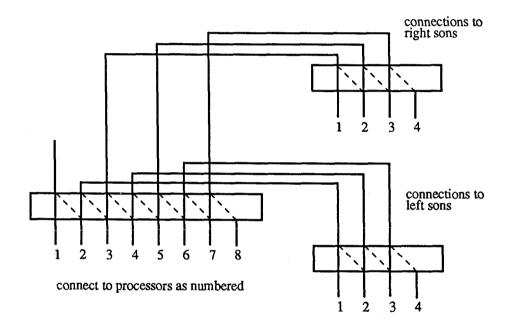

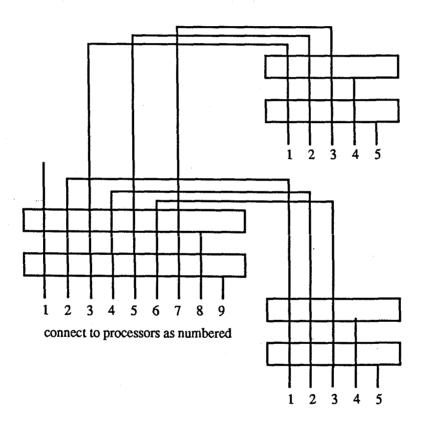

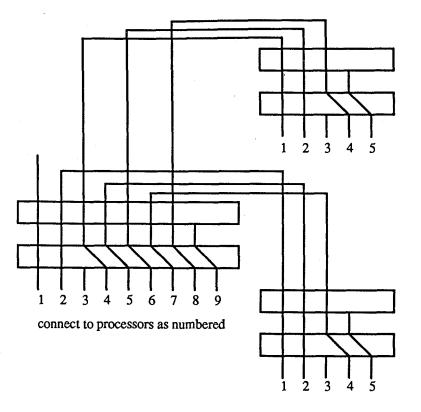

A fault-tolerant binary hypercube can be constructed by using a number of fault-tolerant modules. We assume initially that each fault-tolerant module consists of 4 active processors and k spares, connected in a cycle to model a 2-dimensional binary hypercube. Since only four processors are active at any given time within each 2-dimensional binary hypercube, the spare and faulty processors must be bypassed. This can be done using soft switches in the cycle as shown in Figure 3-1. These 2-dimensional hypercubes are connected together to form a *d*-dimensional binary hypercube. An alternative to the use of soft switches within each module is discussed in Section 3.3 along with the generalization of this construction. The connections between the 2-dimensional binary hypercubes are realized by either a Type A or Type B switching network such that only those active processors in the 2-dimensional binary hypercubes are connected.

Figure 3-1: A fault-tolerant module with k spares

For a d-dimensional binary hypercube, d-2 groups of switching networks are required for each 2-dimensional hypercube in the network. A group of switching networks is used for each dimension beyond the second dimension. The first group is used to connect a 2-dimensional binary hypercube to another 2-dimensional binary hypercube to form a 3-dimensional binary hypercube. The second group for each 2-dimensional hypercube in a 3-dimensional hypercube is used to connect to a 2-dimensional hypercube in another 3-dimensional hypercube, forming a 4-dimensional hypercube. Similarly, the  $i^{\text{th}}$  ( $1 \le i \le d-2$ ) group for each 2-dimensional hypercube in another 3-dimensional hypercube in another i+1-dimensional hypercube, forming an i+2-dimensional hypercube. Hence, a d-dimensional binary hypercube can be formed using  $2^{d-2}$  2-dimensional hypercubes and  $2^{d-2}(d-2)$  switching networks.