### IDISA+: A PORTABLE MODEL FOR HIGH PERFORMANCE SIMD PROGRAMMING

by

Hua Huang

B.Eng., Beijing University of Posts and Telecommunications, 2009

A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE in the School of Computing Science Faculty of Applied Science

> © Hua Huang 2011 SIMON FRASER UNIVERSITY Fall 2011

All rights reserved. However, in accordance with the Copyright Act of Canada, this work may be reproduced without authorization under the conditions for Fair Dealing. Therefore, limited reproduction of this work for the purposes of private study, research, criticism, review and news reporting is likely to be in accordance with the law, particularly if cited appropriately.

#### APPROVAL

| Name:                | Hua Huang                                                                                                   |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Degree:              | Master of Science                                                                                           |  |  |  |  |

| Title of Thesis:     | IDISA+: A Portable Model for High Performance SIMD Pro-<br>gramming                                         |  |  |  |  |

| Examining Committee: | Dr. Kay C. Wiese<br>Associate Professor, Computing Science<br>Simon Fraser University<br>Chair              |  |  |  |  |

|                      | Dr. Robert D. Cameron<br>Professor, Computing Science<br>Simon Fraser University<br>Senior Supervisor       |  |  |  |  |

|                      | Dr. Thomas C. Shermer<br>Professor, Computing Science<br>Simon Fraser University<br>Supervisor              |  |  |  |  |

|                      | Dr. Arrvindh Shriraman<br>Assistant Professor, Computing Science<br>Simon Fraser University<br>SFU Examiner |  |  |  |  |

| Date Approved:       | 7 December 2011                                                                                             |  |  |  |  |

ii

# U SIMON FRASER UNIVERSITY

### Declaration of Partial Copyright Licence

The author, whose copyright is declared on the title page of this work, has granted to Simon Fraser University the right to lend this thesis, project or extended essay to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its users.

The author has further granted permission to Simon Fraser University to keep or make a digital copy for use in its circulating collection (currently available to the public at the "Institutional Repository" link of the SFU Library website <www.lib.sfu.ca> at: <a href="http://ir.lib.sfu.ca/handle/1892/112>">http://ir.lib.sfu.ca/handle/1892/112></a>) and, without changing the content, to translate the thesis/project or extended essays, if technically possible, to any medium or format for the purpose of preservation of the digital work.

The author has further agreed that permission for multiple copying of this work for scholarly purposes may be granted by either the author or the Dean of Graduate Studies.

It is understood that copying or publication of this work for financial gain shall not be allowed without the author's written permission.

Permission for public performance, or limited permission for private scholarly use, of any multimedia materials forming part of this work, may have been granted by the author. This information may be found on the separately catalogued multimedia material and in the signed Partial Copyright Licence.

While licensing SFU to permit the above uses, the author retains copyright in the thesis, project or extended essays, including the right to change the work for subsequent purposes, including editing and publishing the work in whole or in part, and licensing other parties, as the author may desire.

The original Partial Copyright Licence attesting to these terms, and signed by this author, may be found in the original bound copy of this work, retained in the Simon Fraser University Archive.

Simon Fraser University Library Burnaby, BC, Canada

### Abstract

Most of today's commodity processors have single-instruction multiple-data(SIMD) instructions built in and provide SIMD within a register. However, different processor vendors tend to have different SIMD instruction sets which poses significant challenges to cross-platform SIMD programming. This thesis proposes a model called IDISA+ to overcome the compatibility issues and enable portable SIMD programming. There are more than 60 well-selected SIMD operations defined in the model, which are believed to support a broad range of applications. We have implemented the model as a toolkit with two components, a code generator for producing portable libraries and a test suite for both correctness and performance analysis on the libraries. For performance concerns, our model uses a least instruction count mechanism to select the best among implementation alternatives of library routines. The experimental results demonstrate the effectiveness of the generator and show that generated libraries in our model perform better than hand-tuned libraries.

## Acknowledgments

It is a great honor and pleasure for me to have had my Master study at School of Computing Science, Simon Fraser University. I would like to thank all the people who helped and supported me during my graduate study, without whom completing this thesis would be impossible.

Foremost, I am truly indebted and thankful to my senior supervisor Dr. Robert D. Cameron for his invaluable guidance and support. Dr. Cameron helped me to complete this research with patience and numerous efforts, and he also provided me a free academic environment which makes me enjoy doing research with him. This thesis would not have been possible without him.

I would like to express my gratefulness to Dr. Thomas C. Shermer for being my supervisor and spending plenty of time to discuss with me on my research. I would also like to thank my thesis examiner Dr. Arrvindh Shriraman for reviewing this thesis and providing in-depth comments about it. I thank Dr. Kay C. Wiese for serving the chair of my defense.

I am obliged to many of my colleagues in Dr. Cameron's lab for their help and encouragement. They are Ken Herdy, Dan Lin, Vera Lukman, Nigel Medforth, Rui Yang and Shiyang Yang. I specially thank Ken Herdy, Dan Lin and Nigel Medforth for their insightful ideas and suggestions regarding my research.

Last but not least, I thank my parents and family for their love, care and encouragement. This thesis is dedicated to them.

## Contents

| $\mathbf{A}_{]}$ | ppro  | al ii                            |

|------------------|-------|----------------------------------|

| $\mathbf{A}$     | bstra | et iii                           |

| A                | cknov | vledgments iv                    |

| C                | onter | ts                               |

| Li               | st of | Tables viii                      |

| Li               | st of | Figures xi                       |

| 1                | Intr  | oduction 1                       |

| <b>2</b>         | Bac   | zground 5                        |

|                  | 2.1   | SIMD Basics                      |

|                  | 2.2   | SIMD Within A Register           |

|                  | 2.3   | Commercial SIMD Instruction Sets |

|                  |       | 2.3.1 Intel MMX                  |

|                  |       | 2.3.2 SSE Series                 |

|                  |       | 2.3.3 ARM NEON                   |

|                  |       | 2.3.4 AltiVec                    |

|                  |       | 2.3.5 Intel AVX                  |

|                  |       | 2.3.6 Others                     |

|                  | 2.4   | Related Work                     |

|                  |       |                                  |

| 3 | Mo  | del Definition                                               | <b>21</b> |

|---|-----|--------------------------------------------------------------|-----------|

|   | 3.1 | Objectives                                                   | 21        |

|   | 3.2 | Inductive Doubling Principle                                 | 22        |

|   | 3.3 | Integer Operations or Floating Point Operations              | 23        |

|   | 3.4 | Defined Operations                                           | 25        |

|   |     | 3.4.1 Logic Operations                                       | 25        |

|   |     | 3.4.2 Vertical Operations                                    | 27        |

|   |     | 3.4.3 Horizontal Operations                                  | 31        |

|   |     | 3.4.4 Expansion Operations                                   | 32        |

|   |     | 3.4.5 Field Movement Operations                              | 35        |

|   |     | 3.4.6 Bitblock Operations                                    | 39        |

|   | 3.5 | Chapter Summary                                              | 40        |

| 4 | Mo  | del Implementation                                           | 41        |

|   | 4.1 | Programming Interfaces                                       | 41        |

|   |     | 4.1.1 Class Declaration                                      |           |

|   |     | 4.1.2 Data Type                                              |           |

|   |     | 4.1.3 Function Declaration                                   | 44        |

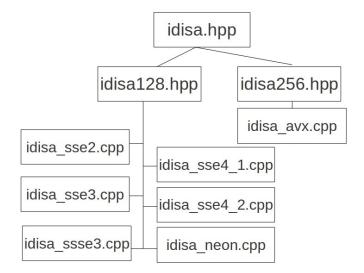

|   |     | 4.1.4 Library Layout and Usage                               | 45        |

|   | 4.2 | Generator of IDISA+                                          |           |

|   |     | 4.2.1 System Architecture                                    | 46        |

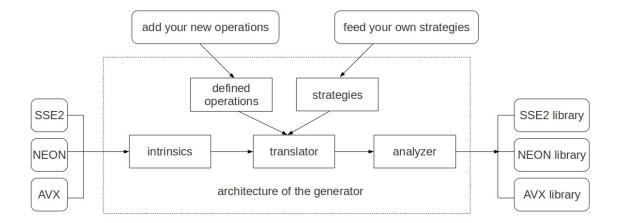

|   |     | 4.2.2 Description of Modules                                 | 47        |

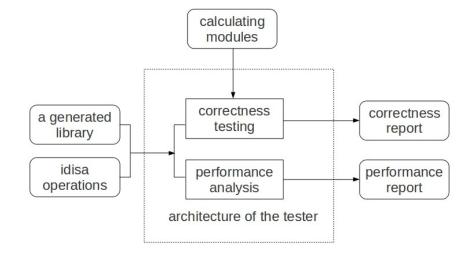

|   | 4.3 | Tester of IDISA+                                             | 56        |

|   |     | 4.3.1 Correctness Testing                                    | 56        |

|   |     | 4.3.2 Performance Analysis                                   | 58        |

|   | 4.4 | Chapter Summary                                              | 58        |

| 5 | Eva | luation                                                      | 59        |

|   | 5.1 | Overview                                                     | 59        |

|   | 5.2 |                                                              | 60        |

|   |     | -                                                            | 61        |

|   |     |                                                              | 64        |

|   | 5.3 | The Generated IDISA+ Libraries for Higher Level Applications | 68        |

| 6  | Conclusion                  | 70  |

|----|-----------------------------|-----|

|    | 6.1 Thesis Summary          | 70  |

|    | 6.2 Future Work             | 71  |

| Aŗ | ppendix A IDISA+ Functions  | 73  |

| Aŗ | ppendix B Strategy Count    | 81  |

| Aŗ | ppendix C Instruction Count | 89  |

| Bi | bliography                  | 103 |

## List of Tables

| 3.1  | Virtual Functions Used to Better Explain the Operations' Functionalities | 26 |

|------|--------------------------------------------------------------------------|----|

| 3.2  | The Logic Operations                                                     | 27 |

| 3.3  | The Vertical Bitmask Operations                                          | 28 |

| 3.4  | The Vertical Unary Operations                                            | 28 |

| 3.5  | The Vertical Binary Operations Part I                                    | 29 |

| 3.6  | The Vertical Binary Operations Part II                                   | 30 |

| 3.7  | The Vertical Ternary Operations                                          | 30 |

| 3.8  | The Horizontal Unary Operations                                          | 31 |

| 3.9  | The Horizontal Binary Operations Part I                                  | 33 |

| 3.10 | The Horizontal Binary Operations Part II                                 | 34 |

| 3.11 | The Expansion Unary Operations                                           | 35 |

| 3.12 | The Expansion Binary Operations                                          | 36 |

| 3.13 | The Field Movement Binary Operations                                     | 37 |

| 3.14 | The Field Movement Ternary Operations                                    | 38 |

| 3.15 | The Field Movement Pattern Fill Operations                               | 38 |

| 3.16 | The Bitblock Unary Operations                                            | 39 |

| 3.17 | The Bitblock Memory Operations                                           | 40 |

| 4.1  | The General C++ Class Declaration for IDISA+ Operations                  | 42 |

| 4.2  | The Specific C++ Class Declaration for IDISA+ Operations Depending on    |    |

|      | Register Size                                                            | 43 |

| 4.3  | Data Types Used in the Libraries                                         | 44 |

| 4.4  | An Example on Intrinsics                                                 | 48 |

| 4.5  | Examples of IDISA+ Operations                                            | 49 |

| 4.6  | The Reserved Types for Defining IDISA+ Operations                        | 49 |

| 4.7 | The Algorithms for Vertical Binary Operations on 1-bit Fields                 | 52  |

|-----|-------------------------------------------------------------------------------|-----|

| 4.8 | The Function Calls in Strategies                                              | 53  |

| 4.9 | The C++ Implementations of Strategies                                         | 53  |

| 5.1 | Some Statistics on SSE2, NEON and AVX in IDISA+                               | 60  |

| 5.2 | The C++ Implementation and Assembly Code for $simd{<}4{>}::add$               | 62  |

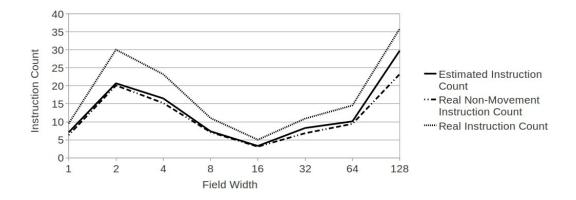

| 5.3 | The Estimated and Real Instruction Count of Several IDISA+ Operations in      |     |

|     | SSE2                                                                          | 63  |

| 5.4 | The Estimated and Real Instruction Count (IC) of Best and Second Best         |     |

|     | implementations of Several IDISA+ Functions in SSE2                           | 66  |

| 5.5 | The Best and Second Best C++ Implementation for $simd{<}4{>}::max$ in SSE2    | 66  |

| 5.6 | The Assembly Code of the Best and Second Best C++ Implementation for          |     |

|     | simd < 4 > ::max in SSE2                                                      | 67  |

| 5.7 | The Performance of Xmlwf on the Hand-written Libraries and the IDISA+         |     |

|     | Libraries (cycle per byte)                                                    | 68  |

| 5.8 | The Performance of Symbol Table on the Hand-written Libraries and the         |     |

|     | IDISA+ Libraries (cycle per byte)                                             | 69  |

| A.1 | All the SSE2 Functions in IDISA+                                              | 75  |

| A.2 | All the NEON Functions in IDISA+                                              | 78  |

| A.3 | All the AVX Functions in IDISA+                                               | 80  |

| B.1 | The Number of Applicable Strategies for each SSE2 Function in IDISA+          | 83  |

| B.2 | The Number of Applicable Strategies for each NEON Function in IDISA+          | 86  |

| B.3 | The Number of Applicable Strategies for each AVX Function in IDISA+           | 88  |

| C.1 | The Estimated Number of Instructions for Each Best SSE2 Function in IDISA+ $$ | 91  |

| C.2 | The Estimated Number of Instructions for Each Second Best SSE2 Function       |     |

|     | in IDISA+                                                                     | 94  |

| C.3 | The Real Number of Non-Movement Instructions for Each Best SSE2 Func-         |     |

|     | tion in IDISA+                                                                | 96  |

| C.4 | The Real Number of All Instructions for Each Best SSE2 Function in IDISA+     | 98  |

| C.5 | The Real Number of Non-Movement Instructions for Each Second Best $SSE2$      |     |

|     | Function in IDISA+ 1                                                          | 100 |

| C.6 | The Real | Number | of All | Instructio | ns for | Each | Second | Best | SSE2 | Function in |       |

|-----|----------|--------|--------|------------|--------|------|--------|------|------|-------------|-------|

|     | IDISA+   |        |        |            |        |      |        |      |      |             | . 102 |

## List of Figures

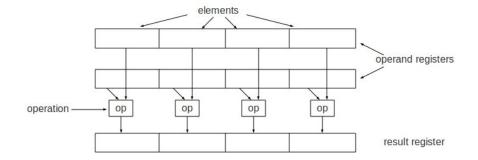

| 2.1  | An Example of SIMD Vector Processing                                           | 6  |

|------|--------------------------------------------------------------------------------|----|

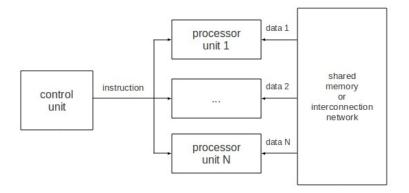

| 2.2  | An Example of SIMD Array Processing                                            | 6  |

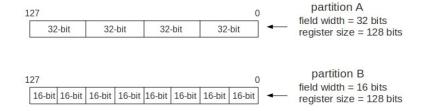

| 2.3  | Examples of Two Different Partitions on a 128-bit Register                     | 7  |

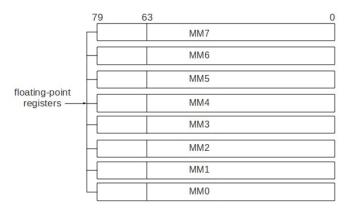

| 2.4  | The View of MMX Registers                                                      | 9  |

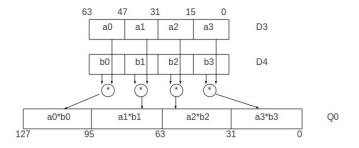

| 2.5  | An Example of Multiplication in NEON                                           | 13 |

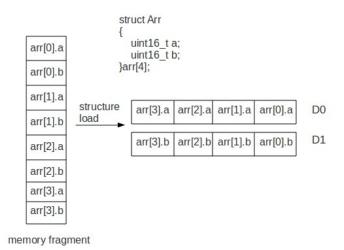

| 2.6  | An Example of Structure Load in NEON                                           | 13 |

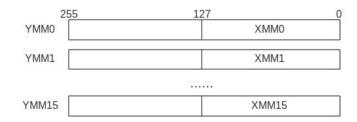

| 2.7  | The Overview of AVX Registers                                                  | 15 |

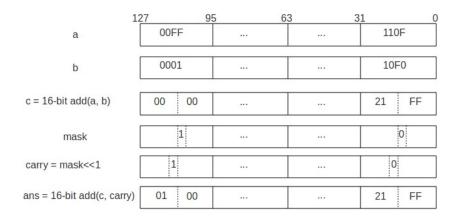

| 3.1  | An Example of Using 16-bit Addition to Emulate 32-bit Addition                 | 23 |

| 3.2  | An Example of Using 32-bit Addition to Emulate 16-bit Addition                 | 24 |

| 3.3  | The View of Field Numbering on a 128-bit Register                              | 26 |

| 3.4  | The Computing Logic of Horizontal Operations on 32-bit fields                  | 31 |

| 3.5  | The Computing Logic of Horizontal Signmask Operation                           | 31 |

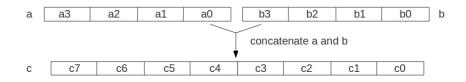

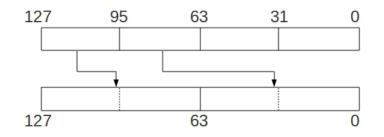

| 3.6  | The Concatenation of Two Operand Registers                                     | 32 |

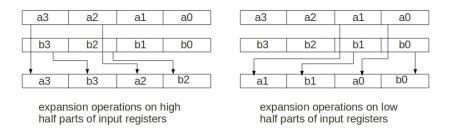

| 3.7  | The Computing Logic of Expansion Operations                                    | 32 |

| 3.8  | The Computing Logic of Expansion Unary Operations                              | 35 |

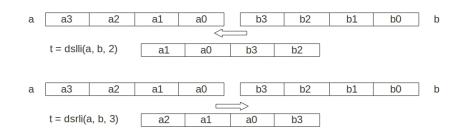

| 3.9  | The Computing Logic of Fill Movement Ternary Operations                        | 37 |

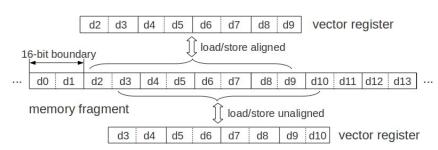

| 3.10 | Examples of Bitblock Load/Store Operations                                     | 39 |

| 4.1  | The Layout of Libraries Generated by IDISA+                                    | 46 |

| 4.2  | The Architecture of IDISA+ Generator                                           | 47 |

| 4.3  | The Architecture of IDISA+ Tester                                              | 57 |

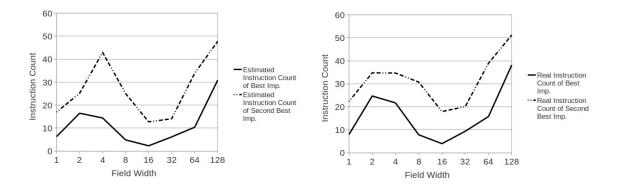

| 5.1  | Comparison Between Estimated and Real Instruction Count for SSE2 $\ . \ . \ .$ | 64 |

| 5.2  | Comparison Between Best and Second Best Implementations for SSE2               | 65 |

### Chapter 1

## Introduction

In traditional scalar processing, operands are fetched in serial fashion into the processing unit before execution. At each step, a single instruction is applied on one piece of data to produce a single result. For example, an arithmetic add instruction would add together only two operands to get an answer at a time. This sequential computing system is often referred to as Single Instruction Single Data (SISD) in Flynn's taxonomy [24], which exploits neither instruction-level parallelism nor data-level parallelism.

Desktop computers, especially personal computers (PCs), have gone through a rapid development in past decades. As a result, compute-intensive applications, like multimedia processing and digital signal processing, became more and more popular on PCs. Many improvements and expansions have been integrated into architectures to meet the strong demand for this particular type of computing and improve the performance over traditional SISD systems of which one of the most important features is Single Instruction Multiple Data (SIMD).

SIMD is a parallel processing technology which is able to perform the same instruction on multiple data simultaneously. Compared to SISD, SIMD mainly has two advantages. First of all, when the data is stored in blocks, SIMD can load one block of data at a time in only a single instruction [48] instead of a series of instructions fetching the data one by one in SISD. Another advantage is that instructions in SIMD can be applied to all the data of a block in one operation. More specifically, for the arithmetic add operation, SIMD would perform the addition on eight pairs of values to produce eight sums in a register. Thus, from the computer architecture's point of view, SIMD systems exploit data-level parallelism, and are being used to improve the performance of today's many software applications. Nowadays, commodity processor manufacturers including Intel, AMD, ARM and IBM have expanded their instruction set architectures with SIMD extensions to accelerate algorithms used in gaming and multimedia related processing. Some of the SIMD extensions have even evolved for many generations, such as the Streaming SIMD Extensions (SSE) series on Intel platform [56]. However, each processor vendor develops and maintains his own versions of SIMD instruction sets due to the lack of a unified commercial standard. That being said, although most commodity processors support SIMD techniques natively, challenges still exist for creating SIMD applications over different platforms. Detailed reasons are listed as follows.

- Because of the high diversity of design and associated algorithms in architectures, the instructions, field widths and the size of registers differ substantially between different SIMD instruction sets. An application written in a source-level language is often implemented based on the current hardware details, such as the available SIMD operations and memory access restrictions. Such implementations are unlikely to work properly if the underlying platform is changed. For example, there is an instruction called *pcmpgtq* in Intel SSE4 instruction set [30] which is to compare two pairs of packed quadword (64-bit) data for "greater than" simultaneously, however, no such instruction existed in PowerPC AltiVec instruction set [47]. Hence, an application built on Intel platform. This makes it difficult and time consuming to write programs which achieve good performance over various architectures, even though these architectures are fairly similar to each other in most important ways.

- A SIMD instruction set is usually designed and implemented as an expansion within an existing architecture. Due to the redesign and modification cost of the architecture, the instruction set would have a set of limited functionality and algorithms that is believed to be the most economical and effective implementation on its host platform. Thus, it is common that even within the same SIMD instruction set, the implementation of an instruction is only available on some pre-chosen data sizes. Take the Intel SSE2 instruction set [32] as an example. The instruction *pmaxsw* in SSE2 computes the maximum of packed signed word (16-bit) integers. But this instruction only works on packed 16-bit numbers, and does not provide the functionality of maximum for other data sizes. This makes it tough to use SSE2 if we have an application that

heavily relies on 32-bit integer maximum operations. Also, for those instructions under some specific data sizes and not yet implemented as built-ins, the alternative implementations should be found if the cross-platform programming is a concern.

Often, programs developed based on an early version of a SIMD instruction set continue to be used on the later versions. But, new instructions that may improve performance are usually checked in as the instruction set evolves within an architecture. It is quite difficult for programmers to tune the performance of the programs over multiple generations.

As SIMD has been incorporated into many commercial processors and is still been actively maintained and promoted by the chip vendors, it is believed that SIMD instruction sets will continue to evolve in many aspects such as new instructions, larger register size and so forth. On the other hand, developers have also used many kinds of SIMD instruction sets to build fast applications on various platforms over years. As a result, programmers might transfer their code from one platform to another with a hope of no incompatibility issues, and they would also like to make use of the capabilities of a newly released instruction set without doing too much work.

Towards addressing the cross-platform issues of SIMD programming and filling the gap between developers and underlying SIMD instruction sets, a portable and high performance SIMD programming model is presented in this thesis.

The model is based on the inductive doubling principle [19] for making in-register SIMD operation sets. Details about inductive doubling principle are provided in the Chapter 3. For implementing the model itself, the thesis has focused on building a toolkit to provide portable and high performance SIMD library support targeting kinds of commodity platforms. There are three main contributions in the thesis:

- The model defines a set of carefully selected operations as library routines which provide a uniform and clean interface for higher level development over various platforms. The operation set is well defined and is believed to capture the most important features of SIMD integer programming so that a wide range of applications could be built upon it.

- The model is built in a way that the implementations of SIMD operation are automatically generated according to the current architecture information and compiler flags.

It is also designed to be very flexible that it allows users to define new operations and add support for new architectures. In fact, the process of defining a new operation or adding support of a entire new architecture into the model is easy and fast. More details about this will be explained in later chapters.

• Performance concerns are considered in the model as well. Normally speaking, a model with more portability maybe expected to sacrifice performance. However, this is not true in our model. In the experiments of the thesis, it shows that the implementations generated by the model achieve slightly better performance than the hand-tuned implementations.

The remainder of this thesis is organized as follows. Chapter 2 reviews the background of SIMD implementations on various architectures and the related work on portable SIMD programming. The detailed definition of the model is given in Chapter 3. In Chapter 4, the algorithm for implementing the model is presented. Chapter 5 collects all the evaluation results and gives some related analysis. At last, Chapter 6 concludes the thesis with a summary of results and directions for future work.

### Chapter 2

## Background

#### 2.1 SIMD Basics

SIMD is a parallel computing concept which describes computers with processing units that perform the same operation on multiple data elements simultaneously. The first use of SIMD instructions was in vector supercomputers of the early 1970s, which could operate on a vector of data with a single instruction [7]. In contrast to scalar computing, SIMD computing is able to apply instructions to each of the vector's elements independently or cumulatively. Unlike other parallel computing systems such as multi-core computing or distributed computing, the development of SIMD is a relatively cheap way of exploiting parallelism with emphasis on data-level parallelism. Generally speaking, SIMD systems can be divided into two types, vector-based and array-based systems.

In the vector-based system, it usually has one processor with a set of vector registers. When executing an instruction, data is loaded into one register which can store some fixed number of elements, and then the instruction is performed on some or all of the elements simultaneously. With the help of vector processing, it allows the processor to achieve better performance than traditional scalar processing. If the SIMD register size is 128-bit, it could get 4 times faster compared to the non-parallel processing when doing 4 pairs of 32-bit integer addition. Figure 2.1 shows the general idea about SIMD vector processing.

However, the vector-based SIMD processors are not well suitable for solving problems involving two or more dimensions. In the array-based system, the SIMD processors are used to deal with the data in large multi-dimensional arrays. Such a system would have a single control unit and a bunch of multiple processing elements (PEs) which are connected

Figure 2.1: An Example of SIMD Vector Processing

Figure 2.2: An Example of SIMD Array Processing

in shapes of multi-dimension. The instructions are distributed by the control unit to the PEs, and each PE receives the instructions and applies them on its own data stream. An example of SIMD array system is shown in Figure 2.2.

Historically, the early SIMD machines were array-based systems and mostly characterized by massively parallel processing-style supercomputers. The most important reason is that supercomputers are normally used to process and analyze a very large amount of data as in meteorological applications and physics simulations, hence, the SIMD on arraybased processors with capability of processing multi-dimensional data efficiently were the best choice to accomplish the jobs. As the inexpensive Multiple Instruction Multiple Data (MIMD) approaches became more powerful later, the interest in SIMD array-based systems waned [7]. However, since desktop processors have become powerful enough in terms of high CPU clock rates, large register complements and advanced system bus designs to support real-time multimedia applications, the SIMD approach is now widely used in machines from

Figure 2.3: Examples of Two Different Partitions on a 128-bit Register

the desktop-computer market in a form of vector-based processing.

#### 2.2 SIMD Within A Register

In this thesis, we target our portable SIMD programming model on the systems which support SIMD within a register (SWAR). Almost all of today's PCs and workstations are the SWAR-capable systems, in which SIMD instructions are executed across sections of a register.

The SWAR model has a very unique property that every register in it can be partitioned into fields and each field is independent from any other field. However, the partition is not a real physical partition but a logical view of partition on registers. For example, a register with 128 bits could be viewed as four 32-bit fields (in Figure 2.3) or eight 16-bit fields (in Figure 2.3) or other possible partitions. Each partition is independent and a SIMD operation in SWAR requires corresponding operand fields to be manipulated without interfering with adjacent fields.

As you see, this property of partition matches perfectly with the SIMD processing idea that an operation is applied on many data simultaneously, hence, the SWAR model is very suitable for supporting SIMD operations with a minimal requirement of hardware enhancements. Since SWAR doesn't restrict the size of each field in a register, we can explicitly set the precision for the field widths as desired when applying operations. More importantly, SWAR systems are designed in a way that there is no penalty for data crossing the logical boundaries inside a register, which provides room for inductive algorithms on emulating SIMD operations.

Unfortunately, the implementations of SWAR systems strongly depend on the architectures and the target services of the systems. Available operations are determined according to the needs of applications especially the multimedia related programs, so the instruction sets are different between architectures, and even within the same architecture some operations are not supported or supported on just a few field widths.

In summary, the SWAR model with the feature of logical partition on registers and its diverse implementations over platforms, is the target for which our high performance and portable SIMD programming model is built.

#### 2.3 Commercial SIMD Instruction Sets

Having a comprehensive understanding about current mainstream SWAR families in IT industry is very important for developing a good SIMD programming model over different kinds of platforms. In the past, the SWAR instruction sets were made to improve the performance of multimedia programs and were usually integrated into the existing architectures as new instruction sets using the SIMD processing paradigm.

Each instruction set was customized by individual microprocessor vendor for the sake of better supporting compute-intensive algorithms and applications on its host platform. Given the variety of microprocessors, each SWAR extension has a unique set of instructions and the supported SIMD operations vary widely. But, this doesn't mean SWAR instruction sets are totally different from each other. In fact, the underlying algorithms of many SWAR operations are equivalent for different platforms although the operations might differ in available field widths or performance. So it turns out that every SWAR instruction set has implementations which are similar or even identical to those of others.

Early SWAR instruction sets on a platform were normally limited to a few of instructions which only serve the most frequently used operations and applications for this particular architecture. Later extensions were often created to address some issues in previous versions and provide a wider range of SWAR related instructions. Thus, one SWAR instruction set might evolve for many generations and ultimately become more complete and powerful.

In this section, several typical SWAR instruction sets in current commodity processors are reviewed to show their capabilities and limitations and also to provide the guidance for designing and implementing our portable SIMD programming model.

Figure 2.4: The View of MMX Registers

#### 2.3.1 Intel MMX

MultiMedia eXtension (MMX) is a SWAR instruction set designed by Intel in 1996 to improve performance of multimedia and communication algorithms. It was the first major addition to the Intel Architecture-32 (IA-32) since the Intel 386<sup>TM</sup> architecture [29]. The definition of MMX technology evolved from the Intel i860<sup>TM</sup> architecture which was the industry's first general purpose processor for graphics rendering with the functionality of parallel computing on multiple adjacent data operands.

MMX adapts to SIMD approach by defining the packed data format for data representation which allows the input data to be processed simultaneously in small data fields such as 8-bit or 16-bit. There are eight 64-bit registers defined in MMX, known as MM0 through MM7. To maintain the compatibility with the IA-32 architecture of that time, those registers were not defined as a new set of registers but aliases of the existing IA-32 Floating-Point Unit (FPU) stack registers. MMX only uses the low 64 bits of each FPU register and sets the unused bits to be all ones to reduce confusion between a MMX data value and a valid floating-point value. Figure 2.4 shows the overview of MMX registers in the FPU registers. However, because the dual usage of the FPU registers doesn't allow the concurrent execution of both MMX code and floating-point code (meaning that the MMX code and floating-point code must be in separate code sequences), there is a mode switch cost if an application uses both codes.

However, MMX only provides integer operations to meet the requirement of integer math used in early graphical applications. The set of operations provides a relatively wide range of support for the SIMD programming, which includes arithmetic logic operations, saturating arithmetic, fixed-point arithmetic and repositioning of data elements within a register. The design of MMX had limited it to contain new instructions specifically designed for audio, graphics and other multimedia applications. Although there were 57 new instructions added in MMX [45], the implementations are not available over consistent field widths and also lack full support for many types of operations, such as comparison operations. Moreover, many of the instructions have little application outside the multimedia domain. Thus, MMX is not a general purpose instruction set for a high level SIMD programming model.

For further information about MMX, readers can refer to [50] which provides an overview of the MMX instruction sets and also [32] which has detailed information about the MMX instructions including intrinsics and programming convention.

#### 2.3.2 SSE Series

A few years after MMX was released, Intel introduced Streaming SIMD Extensions (SSE) in their Pentium III series processors in 1999. SSE instruction sets were subsequently extended in a series of versions including SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4a and SSE4.2. Intel was the main contributor designing all SSE generations except SSE4a which was created by AMD.

#### SSE

In contrast to the MMX extension, SSE added 70 new instructions, primarily dedicated to support single-precision floating-point data [56]. It also added a few integer instructions such as minimum or maximum instructions that work on MMX registers. In addition, SSE added a set of eight new independent registers named XMM0 through XMM7 which are 128-bit SIMD floating-point registers. In short, MMX instructions are still available in SSE using the 80-bit floating-point stack registers to process integer data while SSE operations process the XMM registers with four 32-bit single-precision floating-point values as its data representation.

#### SSE2

In 2001, SSE2 was released by Intel along with the initial version of Pentium 4 to extend the earlier SSE instruction set [32]. It migrated all the MMX instructions to operate on XMM registers allowing an application to work on both SIMD and scalar floating-point data without the switch cost required between MMX instructions and floating-point operations. More importantly, SSE2 added a rich set of integer instructions which extends MMX functionality to 128-bit XMM registers. This gives SSE2 a significant advantage that it could execute instructions twice as fast as MMX in theory due to the doubled register size.

AMD soon added support for SSE2 in its Athlon 64 processors based on the AMD64 architecture. In AMD's implementation, it doubled the number of XMM registers to sixteen as XMM0 through XMM15. In 2004, Intel adopted these additional registers as part of their SSE2 implementation for the IA-64 architecture [2].

#### SSE3

The third iteration of SSE instruction sets of Intel is the SSE3, which was introduced with the Prescott revision of the Pentium 4 processors in 2004. In SSE3, the major improvement is that some instructions working horizontally in a register with floating-point values were added to simplify certain DSP and 3D graphics related algorithms [9]. A new instruction which does misaligned integer vector load was also included to achieve better performance on loading data across cache-line boundaries.

#### SSSE3

SSSE3, the fourth generation of the SSE series, was included with Core micro-architecture based Intel processors in 2006. It contains 16 new instructions compared to its precursor, most of which are signed magnitude arithmetical instructions and instructions working horizontally on XMM registers with packed integer data.

#### SSE4

As the last iteration in SSE family, SSE4 was officially announced in 2006, and became available in hardware in early 2007 for both Intel and AMD processors. SSE4 now has three variation, SSE4.1, SSE4a and SSE4.2 which contribute more than 50 instructions all together.

SSE4.1 is the major extension of SSE4 with 47 instructions added including some instructions that are not specific to the multimedia domain such as conditional copying or shuffle of elements from one location to another based on the bits in an immediate operand or a XMM register. Some other instructions are mainly about arithmetic operations on packed integer data and memory related operations. SSE4.2 completed the SSE4 instruction set by adding 7 new instructions, most of which are comparison operations on packed explicit length strings.

SSE4a, introduced by AMD on the AMD K10 micro-architecture in 2007 [10], implements part of SSE4.1 instructions from Intel and adds its own 6 instructions for bit manipulation as well.

Evolving for years and reaching five generations in total, the series of SSE instruction sets have formed a powerful SWAR extension in the microprocessor industry. However, SIMD operations supported in SSE series are still limited to a few field widths, and there are only a few instructions which are outside multimedia applications. Although the SSE series is fully upward compatible with MMX, there are two different sets of programming intrinsics for MMX and SSE. This poses a challenge for developers to migrate MMX based programs to SSE based programs, which might require them to make significant revision to source code in order to adopt the SSE programming convention.

The initial goal and design of SSE instruction sets is given in [56]. Full descriptions of SSE instructions and programming model can be found in the IA-64 and IA-32 architecture software developer's manual [32]. Some detailed information about SSE4a was posted at the online AMD developer central [10].

#### 2.3.3 ARM NEON

An advanced SIMD extension named NEON was introduced by ARM in their Cortex-A series processors to improve the performance of multimedia and signal processing algorithms such as 3D graphics, gaming and audio/speech processing. It has a comprehensive set of instructions and some of the instructions are shared with the ARM Vector Floating Point (VFP) extension. NEON supports 8-bit, 16-bit, 32-bit and 64-bit signed and unsigned integers and also 32-bit single precision floating point values naturally.

There are 32 featured 64-bit registers associated with NEON implementation, which can be accessed by both NEON and VFP processing units. Interestingly, NEON can view its register set in two different ways, one way is thirty-two 64-bit doubleword registers (D0-D31), the other is sixteen 128-bit quadword registers (Q0-Q15). In fact, the doubleworld registers and the quadword registers alias each other with the 64-bit registers  $D_{2*i}$  and  $D_{2*i+1}$  mapping against the same physical location of the register  $Q_i$ .

NEON can utilize both register views to process data, which means that data from

Figure 2.5: An Example of Multiplication in NEON

Figure 2.6: An Example of Structure Load in NEON

registers in different views could be accessed in the same instruction. With this particular property, instructions in NEON could have different size input and output registers and be able to promote or demote data elements in an operation. For example, in Figure 2.5, " $VMULL.S16\ Q0, D3, D4$ " multiplies four pairs of 16-bit values from doubleworld registers D3 and D4 at a time and produces four 32-bit products in the 128-bit quadworld register Q0.

Another notable property of NEON is that, it not only has instructions which can load and store multiple data from or to a SIMD register, but also includes some instructions that can transfer complete data structures between several SIMD registers and memory location with interleaving and de-interleaving options. An example is shown in Figure 2.6.

There are many references about ARM NEON available. Some introduction on NEON

can be found in [16, 51]. The white paper titled "ARM NEON support in the ARM compiler" [15] discusses the compiler support for SIMD from the automatic recognition approach and also the perspective of the use of intrinsic functions. The assembler guide [14] describes all the instructions and the underlying assembly programming of NEON in detail.

#### 2.3.4 AltiVec

AltiVec is a SIMD extension to the PowerPC architecture [6], developed by Motorola, Apple and IBM in late 90s. Apple was the main consumer of AltiVec until they switched to Intel x86 based processors in 2006 while Motorola had been the main manufacturer for providing AltiVec chips. IBM declined to be involved in AltiVec, instead, they have made the VMX which is similar to AltiVec out of their Power processors. AltiVec is now a trademark owned solely by Freescale, the former semiconductor products division of Motorola.

AltiVec expands the PowerPC architecture through the addition of a vector processing unit with thirty-two 128-bit registers built in. It supports 8-bit, 16-bit and 32-bit integers and also 32-bit floating point data. There are 164 new instructions added in AltiVec, providing a general set of instructions including intra and inter-element arithmetic instructions, intra and inter-element conditional instructions and some powerful repositioning instructions. Unlike the SSE series instructions that store results back into a source operand register, each instruction in AltiVec is a non-destructive instruction which can preserve the content of source operand after the instruction is executed. Furthermore, AltiVec has a powerful and flexible vector permute instruction which can extract the data elements from either of two operand registers and reposition them in the resulting register according to the parameters in yet another register. This allows for sophisticated manipulations on ordering data in a single instruction.

An introduction on AltiVec and the ways to vectorize code using AltiVec are shown in [26]. The programming environment manual of AltiVec technology [46] contains guide for assembler programmers and has detailed information about instructions. High-level programmers should refer to [47] which provides C/C++ programming interface for using the AltiVec instruction set.

Figure 2.7: The Overview of AVX Registers

#### 2.3.5 Intel AVX

In 2008, a new SIMD extension to Intel x86 architecture named Advanced Vector Extensions (AVX) was announced. AVX extends the previous Intel SIMD instruction sets such as MMX and SSE series by adding many new features to provide even better performance on multimedia applications and vector processing. The actual implementation came with Intel Sandy Bridge processors [3] in early 2011.

Compared to SSE series, AVX increases the size of its SIMD registers from 128 bits to 256 bits. The AVX registers named YMM0 through YMM15 are aliased over the initial 128-bit XMM registers of SSE series with the XMM registers as the lower 128-bit of the corresponding YMM registers, shown in Figure 2.7. Hence, AVX fully supports legacy SSE instructions including the SIMD data type used in SSE as well. AVX instructions operate on 8-bit, 16-bit, 32-bit, 64-bit and 128-bit integers as well as 32-bit and 64-bit floating point values.

One of the most important improvements made in AVX is that instructions are nondestructive, mostly with two source operands and a separate destination operand. Thus, the AVX instructions enable the preservation of the content in source operand after execution so that potential movements between registers as in the SSE series could be reduced. Besides, there are a few of four-operand instructions added to allow smaller and faster code written in AVX.

As another significant change made in AVX, a new extension coding scheme (VEX) has been designed to encode instructions and make future additions easier. The VEX is a prefix encoding with space of two or three bytes, which was designed to simplify the current and future Intel x86 based instruction encoding and allow more instructions to be included and encoded. It extends the older SSE instructions by adding a VEX prefix for accessing the new 256-bit registers and three-operand forms. Unfortunately, the current implementation of AVX only allows the integer instructions to operate on the lower half of YMM registers with options to zero or retain the higher half parts. However, there are some instructions which can move or extract data of either the high or low 128 bits of the YMM registers, making it possible to achieve parallel processing on 256 bits.

According to Intel's documentation [31], it is believed that AVX is designed to support registers with 512 or 1024 bits in the future. AVX2, the next immediate generation of AVX, will ensure every legacy SSE instruction has a VEX form to operate on the entire 256 bits of the YMM registers naturally. In [43], it introduces the overall design and goal of AVX. The Intel AVX programming reference [31] contains specific information about instructions and programming model in AVX and AVX2. Besides, a AVX C/C++ intrinsics emulation provided by Intel [1] enables developers to program with Intel AVX intrinsics on the machines which do not support AVX.

#### 2.3.6 Others

Because of their wide usage and comprehensive support of instructions, several representative SIMD extensions on various commodity microprocessors are reviewed in above sections. Nevertheless, there are also other extensions which play important roles in the parallel processing area, which either contribute as the basis of the recent SIMD extensions or provide functionality for some specific applications beside multimedia.

Intel i860, also known as 80860, was the first microprocessor having vector processing instructions, introduced by Intel in 1989. It has a graphics unit using FPU registers as SIMD registers to process instructions for 3D graphical applications. The development of i860 was the groundwork for Intel x86 based system to support SIMD instructions, and it influenced the MMX functionality heavily in Intel Pentium processors later [50].

In 1994, HP developed its initial version of Multimedia Acceleration Extension named MAX-1 on 32-bit PA-RISC 1.1 architecture PA-7100LC processors [42, 40]. It uses a very small set of SIMD instructions and enables real-time video decompression without the need of special hardware enhancements [41]. Two years later, with the 64-bit PA-RISC 2.0 architecture introduced, HP extended the earlier MAX-1 instruction set to create a new set of SIMD extension called MAX-2 which could operate on the 64-bit registers with more instructions available.

Sun Microsystems developed a SIMD extension called Visual Instruction Set (VIS) for

SPARC V9 microprocessors, and the first implementation of VIS was released along with UltraSPARC microprocessor in 1995 [55, 54]. The second generation, VIS-2 was implemented in the UltraSPARC III later as an enhancement. VIS uses the 64-bit floating point registers to hold data which is similar to the Intel MMX design. The instructions of VIS are primarily for visual and graphical applications such as format conversions between pixel data and 16/32-bit values and some arithmetic operations on data with small bits.

Since Intel MMX doesn't support SIMD instructions on floating point values, AMD added a new extension named 3DNow! on AMD K6-2 processors in 1998 to enable arithmetic operations on single precision floating point values. In the first generation of Athlon processors, AMD introduced the enhanced 3DNow! as the extension to the older 3DNow! by adding many new 3DNow! and MMX instructions [12]. Couple years after enhanced 3DNow! was released, starting from the AMD Athlon XP, 3DNow! Professional has been used as the name for a combination of 3DNow! technology and SSE instructions sets.

#### 2.4 Related Work

With the rapid growth of SIMD instruction sets on commodity microprocessors, quite a bit of research has been done on these SIMD extensions, expanding from building a portable SIMD programming model over platforms to using SIMD instructions to auto-vectorize or optimize the sequential programs [11, 49]. To my knowledge, the research can be divided into two categories, the compiler technology for SIMD instructions and the library support for SIMD programming.

#### Compiler Technology for SIMD Instructions

Fisher's work on compiling for SIMD within a register [22] proposed a general-purpose SIMD programming model with a C-like module language and an associated compiler named Scc. Based on the C language, the module language adopted many base data types from C and also added a vector type to support SIMD programming. Thus, it allows programmers to describe the SWAR data types and algorithms in a portable manner. The associated compiler Scc supports parsing the code written in the module language and implementing the specified algorithms into C code based on the capabilities of the target architecture. According to Fisher's PhD thesis [23], this model supports code generation on AltiVec, 3DNow!, MMX and SSE.

While Fisher's work was the groundwork for portable SIMD programming, the implementations generated by his model did not achieve good performance in some circumstances, particularly when the application relied on many non-built-in operations. As shown in his thesis [23], the code generated by Scc targeting MMX did not gain any speedup but slowed down the performance at a ratio between 0.4 and 0.8. Although there were many compiler techniques added into the model to optimize the generated implementations for non-built-in operations, the study on emulation techniques for non-built-in operations was still insufficient which limits the further use of the model for a general-purpose SIMD programming.

Bocchino and Adve presented a virtual vector instruction set called Vector LLVA for media processing [34]. The Vector LLVA supports arbitrary-length vectors for streaming processors and also fixed-length vectors for processors equipped with multimedia/SWAR extensions like AlitVec and SSE. It defines a relatively rich set of instructions covering general arithmetic operations, vector-memory operations and data movement operations. This vector programming model was also attached with translators which are able to translate the Vector LLVA code into C code that use the intrinsics and programming conversions of three target architectures (Motorola RSVP, AltiVec and Intel SSE2) individually.

However, Vector LLVA model requires developers to write and tune applications at an instruction level which is challenging work for source-language level programmers. And the performance of implementations generated by Vector LLVA was not well balanced, sometimes slightly better than hand-tuned implementations while sometimes worse. Besides, the Vector LLVA has a fixed set of instructions and its translators only support those built-in instructions, hence, it is not likely to allow people to add new instructions or operations for their own purpose.

Liquid SIMD [20] is another compiler technology for supporting programming and applications on multiple SIMD extensions. It has both compiler support and dynamic translation to decouple the instruction set architecture from the implementation of a SIMD accelerator. The way it achieves portability relies on two stages. First, it identifies SIMD instructions and compiles them into a virtualized SIMD schema using the scalar instruction set of a processor. Then, during program execution, it uses a light-weight dynamic translation engine to convert these scalar instructions back into SIMD instructions that can be executed on an arbitrary SIMD accelerator. However, more experiments on other platforms are needed to be done as Liquid SIMD was only demonstrated on the ARM platform.

In addition to the compiler technology for portable SIMD programming, there are some

other techniques which could parallelize parts of a sequential program automatically. The idea is to identify the potential parallelism spots in source codes, especially in the loops and basic blocks, and try to replace the traditional instructions by SIMD instructions so that certain speedups could be gained. In [36], Larsen and Amarasinghe presented a novel way of viewing parallelism in multimedia applications called Superword Level Parallelism (SLP). They also developed a compiler for detecting SLP targeting basic blocks rather than loop nests. In Larsen's PhD thesis [35], he worked further on SLP technology and made two major improvements, one is the effective management of memory alignment for compiling short-vector instructions, the other is a selective vectorization technique for balancing computation across scalar and vector resources in a processor based on software pipelining. Shin also proposed a compiler framework based on SLP to exploit parallelism automatically in sequential programs [53]. Shin's compiler has a number of optimizations compared to Larsen's, it extends SLP in the presence of control flow constructs to increase the applicability of SLP and treats the SIMD register file as compiler-controlled cache to avoid unnecessary memory access.

#### Library Support for SIMD Programming

In his PhD thesis [52], Rojas implemented a set of multimedia macros for portable optimized programs. Each macro has an individual implementation for each supported architecture, and all macros together provide a unique interface for high-level programming. The author developed the implementation for each macro on a certain architecture by manually trying different algorithms and picking the best one with the criteria in terms of instruction count and execution time in CPU cycles. The set of macros supports 8-bit, 16-bit and 32-bit integers and 32-bit floating point values on AltiVec, Intel MMX/SSE/SSE2 and TriMedia TM 1300. To gain the portability for SIMD programming, Rojas's macros actually slow down the performance as the experimental results in his work shown that the performance based on the portable macros lost around 12% for a certain algorithm compared to a specific hand-tuned implementation.

To encourage the development of applications in compute-intensive areas on Mac OS X or later computers, Apple has created an accelerate framework [13, 28] for high performance numerical computations. The framework's implementations are highly optimized for AltiVec and Intel SSE platforms by Apple to fully take advantage of those platforms'

capabilities especially the SIMD processing units. There are two sub-frameworks in the accelerate framework, vecLib and vImage. General numerical operations including addition, multiplication and so forth for both scalar and vector data are included in vecLib, while vImage provides a set of image processing routines. This accelerate framework provides developers a set of abstract programming interfaces in C to allow them to use the vector processing resources of the target platforms without worrying about the low level difference between platforms.

libSIMD [4] is a open-source mathematical library using SIMD processing capabilities of 3DNow! and Intel SSE processors to accelerate some commonly used algorithms. The library provides function interfaces in C for programmers and only supports 32-bit and 64bit precision floating point values. Most implementations in the libSIMD were written in assembly codes to get as much performance as possible. Similarly, SIMDx86 [8] is another optimized math library mostly written in assembly codes for graphics applications especially the 3D games engines and 3D visualizations and so on. SIMDx86 provides C function routines that can work on 3DNow!/Enhanced 3DNow!, Intel MMX and SSE/SSE2 platforms.

Instead of building a C library for high-level SIMD programming, some work has been done to provide C++ libraries using template metaprogramming mechanism. EVE [21], an object oriented SIMD library designed for AltiVec processors, which was built upon a template metaprogramming engine to support a STL-like programming interface for developers to write efficient applications compared to the traditional C libraries. Provided by pixelglow software, a C++ library called macstl [5] was distributed for generic SIMD programming to Macintosh and Windows platforms. In macstl, there is a class named vec for manipulating vector data, which supports a standard vector initialization syntax in a C++ template manner and includes a common programming interface for developers to write fast SIMD applications that work with AltiVec and Intel MMX/SSE/SSE2/SSE3 instruction sets. Due to the strong demand of fast numerical applications, Boost just announced in early 2011 that they are going to add a SIMD library [27] to support vector processing on various architecture families including Intel x86, PowerPC and ARM.

### Chapter 3

## Model Definition

#### 3.1 Objectives

As shown in the related work of Chapter 2, many compilers made for SIMD instructions have a problem that the performance usually drops off compared to a specific hand-tuned implementation. With these compilers, programmers are normally required to play with the low-level instructions directly when writing applications. In this thesis work, instead of building a virtual SIMD instruction set and an associated compiler, we decided to create a library support for the portable SIMD programming.

The goal of this library support is to enable portable programming among diverse SWAR architectures, provide a clean and uniform interface for ease of programming, and more importantly, ship the same and even better performance as the specific architecture-dependent implementations.

#### Portability

Supporting programming over platforms is a challenging task. First of all, there are many operations that have to be implemented as for a SIMD library, and even worse, an operation usually has several versions depending on the operating field width. Thus, it is impractical and very time-consuming for human-beings to develop each library for every architecture by hand. Secondly, even if hand-written libraries are acceptable, finding the best implementations of them involves lots of human efforts and expertise knowledge in computing. Besides, a library is often released as a set of fixed interfaces so that adding a new operation or function which incorporates well with the library is difficult.

The way we achieve portability mainly relies on two aspects. First and foremost, we do not want the library in our model to be hand-written because that requires huge efforts and is not flexible for further optimization. Therefore, we have developed a framework which could generate the objective libraries for various architectures automatically in C++. In the next place, the framework we have built provides an interface that allows users to add new operations easily and improve the library's implementations with a few effort.

#### Performance

Performance is a critical concern when designing libraries. In particular, a portable library should not trade too much performance out in order to support portability. However, there are many factors that affect the performance, such as cache algorithm, instruction pipeline interactions and memory access latency and so forth. Nevertheless, an optimized library must take full advantage of the target's capabilities, especially its instruction set, to keep the number of instructions of an application as less as possible. To accomplish that, our model has a mechanism to optimize the implementation of each operation in terms of minimizing instruction count. Generally speaking, it is expected our model out-performs the handoptimized libraries.

#### **3.2 Inductive Doubling Principle**

Before designing what SWAR operations our model wants to support and showing how we support them, it's better to first look at some properties of SWAR operations in general.

- Any of SWAR operations applies the same operation on partitioned fields of a register simultaneously with each field has the same width.

- The size of fields is normally 16 bits, 32 bits and other power-of-2 bit widths; these work well with the frequently used data types like *char* and *int* in most programming languages.

- In current available SWAR instruction sets on commodity processors, an operation might not have full support for all power-of-2 field widths, i.e., the operation lacks implementations for some field widths.

When it comes to implement a SWAR operation for a missing field width, it is very natural to use the implementation of the same operation on other close field widths to do the

Figure 3.1: An Example of Using 16-bit Addition to Emulate 32-bit Addition

job. In [19], Dr. Cameron has proposed an inductive doubling instruction set architecture (IDISA) which nicely captures the idea of simulating SWAR operations for missing field widths based on the observation that implementing a SWAR operation on a certain data size could use the algorithm for the operation on halved data size and vice versa.

For example, we could use an addition operation on 8 pairs of 16-bit numbers simultaneously along with some shifting and combination work to get an operation of capability to perform addition on 4 pairs of 32-bit numbers at a time. Figure 3.1 gives such an example.

Conversely, the addition on 4 pairs of 32-bit numbers can also be used to simulate the 8 pairs of 16-bit numbers addition. The idea is shown in Figure 3.2.

Overall, inductive doubling principle provides a general approach for emulating a SWAR operation for missing field widths within the same operation family. However, people could always find implementations for a SWAR operation in a totally different manner instead of the inductive doubling fashion. An extreme example would be using bit-wise xor to accomplish the 1-bit addition between two SIMD registers. That being said, inductive doubling principle is not the entire methodology of our model but a basic foundation which provides guidance for making the library support in our model.

#### 3.3 Integer Operations or Floating Point Operations

To best serve the higher level applications using our library support, we have defined a set of well-chosen operations in our model. The operations are carefully selected in order to

|                                                            | 127   | 95 | 6 | 3    | 31 | 0  |

|------------------------------------------------------------|-------|----|---|------|----|----|

| a                                                          | 10    | FF |   |      | 00 | FF |

| b                                                          | 20    | 01 |   |      | FF | 11 |

| a0 = mask out high half part<br>of each 32-bit field in a  | 00    | FF |   |      | 00 | FF |

| b0 = mask out high half part<br>of each 32-bit field in b  | 00    | 01 |   |      | 00 | 11 |

| c0 = 32-bit add(a0, b0)                                    | 01    | 00 |   |      | 01 | 10 |

| c0' = mask out high half part o<br>each 32-bit field in c0 | of 00 | 00 |   | (m.) | 00 | 10 |

| a1 = mask out low half part<br>of each 32-bit field in a   | 10    | 00 |   | []   | 00 | 00 |

| b1 = mask out low half part<br>of each 32-bit field in b   | 20    | 00 |   |      | FF | 00 |

| c1 = 32-bit add(a1, b1)                                    | 30    | 00 |   |      | FF | 00 |

| ans = c0' or c1                                            | 30    | 00 |   |      | FF | 10 |

Figure 3.2: An Example of Using 32-bit Addition to Emulate 16-bit Addition

fully exploit the features of vector parallelism and supply SIMD functionalities as well as possible.

Unlike many other portable SIMD programming models which primarily serve the fast mathematic applications and support operations on vectors of floating point values, the current operations defined in our model are intended for working on vectors of integer values. The reasons why we decided to support integer operations not floating point operations are as follows.

- A floating point data is often either single precision (32-bit) or double precision (64bit) in terms of binary representation. Usually, operations on the floating point data can not be simulated in the inductive doubling manner. For example, it is very difficult to get the result with high enough precision by using two 32-bit floating point values to act like a 64-bit floating point value when applying SIMD operations. However, that is not a problem for integer numbers as we could easily use two 32-bit integers to hold a 64-bit integer without losing any precision.

- If we want to define operations for floating point values, there would be two independent versions for each operation with one works for 32-bit floating point values while

the other works for 64-bit floating point values. This essentially requires two different SIMD data types and makes our model quite complex.

• In supporting only the SWAR integer operations, there is still an extensive application space. Not only are the traditional media processing applications based on integer operations, but also are many other applications such as high-speed XML parsing using parallel bit stream technology [17, 18].

At present, we define integer operations in the model as built-in operations because we mainly target our model on some specific applications where integer operations are the dominant operations. However, our portable model is designed as an improvable model so that users can define their own operations even like floating point operations in the model easily if they really want to.

## **3.4** Defined Operations

Every operation in our model is defined to work on a SIMD register with a number of fw-bit fields, and the width of all fields is a power-of-2, i.e.,  $fw = 2^k$  for  $0 \le k \le K$ , where the size of the SIMD register is  $sz = 2^K$  bits. Among the commercial SWAR instruction sets, the value of K is 6 for Intel MMX with 64-bit registers, 7 for Intel SSE series and ARM NEON with 128-bit registers, and 8 for the Intel AVX with 256-bit registers.

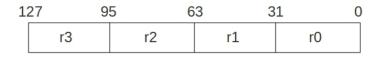

If a certain field width fw is specified, a register r can be viewed as sz/fw fields with fields indexed  $r_0$  through  $r_{sz/fw-1}$ , in which  $r_{sz/fw-1}$  is the highest field and  $r_0$  is the lowest one. In Figure 3.3, it shows the view of numbering. For an operation op working on two register a, b with fw-bit fields, we denote it as  $op_{fw}(a, b)$ .

So far, there have been more than 60 operations defined in the model with all of them can be grouped into six categories: logic operations, vertical operations, horizontal operations, expansion operations, field movement operations and bitblock operations. Before going into the detailed description of operations, we first present several virtual functions in Table 3.1 to better explain the functionalities of defined operations.

#### 3.4.1 Logic Operations

A logic operation performs bit-wise operation on one or more registers and is in the form of  $r = simd_op(a)$  or  $r = simd_op(a, b)$ , where a and b are input registers. There are six logic

Figure 3.3: The View of Field Numbering on a 128-bit Register

| Function Name                  | Description                                                   |

|--------------------------------|---------------------------------------------------------------|

| $Signed(r_i)$                  | return the i-th field of register $r$ as a signed integer     |

| $Unsigned(r_i)$                | return the i-th field of register $r$ as an unsigned integer  |

| $High_{fw}(r_i)$               | select the high half part of the i-th field of register $r$ , |

|                                | i.e., $r_i >> (fw/2)$                                         |

| $Low_{fw}(r_i)$                | select the low half part of the i-th field of register $r$ ,  |

|                                | i.e., $r_i \& ((1 << (fw/2)) - 1)$                            |

| $Number Of Field_{fw}(r)$      | return the number of fields in $r$ , i.e., $sz/fw$            |

|                                | if $r_i < 0$ , return 0                                       |

| $UnsignedSaturation_{fw}(r_i)$ | else if $r_i \leq 2^{fw/2} - 1$ , return $r_i$                |

|                                | else, return $2^{fw/2} - 1$                                   |

|                                | if $r_i < -2^{fw/2-1}$ , return $-2^{fw/2-1}$                 |

| $SignedSaturation_{fw}(r_i)$   | else if $r_i \leq 2^{fw/2-1} - 1$ , return $r_i$              |

|                                | else, return $2^{fw/2-1} - 1$                                 |

|                                | if $fieldNum = 2$ , return $1\&(mask >> i)$                   |

|                                | else if $fieldNum = 4$ , return $3\&(mask >> (i * 2))$        |

| $Index_{fieldNum}(mask,i)$     | else if $fieldNum = 8$ , return $7\&(mask >> (i * 3))$        |

|                                | else if $fieldNum = 16$ , return $15\&(mask >> (i * 4))$      |

Table 3.1: Virtual Functions Used to Better Explain the Operations' Functionalities

| Operation    | Meaning                             | Description            |

|--------------|-------------------------------------|------------------------|

| $simd_nor$   | perform bit-wise $or$ on $a, b$     | $t = \neg(a b)$        |

|              | and then perform bit-wise $not$     |                        |

|              | on the result                       |                        |

| simd_not     | perform bit-wise $not$ on $a$       | $t = \neg a$           |

| simd_andc    | perform bit-wise and on $a, \neg b$ | $t = a \land (\neg b)$ |

| $simd_{-}or$ | perform bit-wise $or$ on $a, b$     | $t = a \lor b$         |

| simd_and     | perform bit-wise $and$ on $a, b$    | $t = a \wedge b$       |

| simd_xor     | perform bit-wise $xor$ on $a, b$    | $t = a \oplus b$       |

Table 3.2: The Logic Operations

operations provided in the model, In Table 3.2, it describes all these logic operations.

#### 3.4.2 Vertical Operations

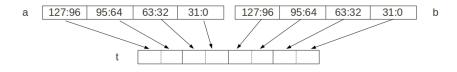

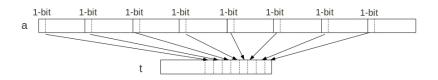

The vertical operations refer to the operations which perform on vertically aligned fields between two different registers. They operate on operand registers with fw-bit fields and produce a register with fw-bit fields as result. Many common operations fall into this category such as addition, subtraction and so on. The general computing logic of vertical operations is shown in Figure 2.1.

Depending on the number of arguments, vertical operations can be further divided into four different sub-categories, the vertical bitmask constants, the vertical unary operations, the vertical binary operations and the vertical ternary operations.

#### The Vertical Bitmask Constants

Only two bitmask operations are defined in the vertical operations, they are *himask* and *lomask* operations. Both of them do not have any argument in addition to the field width information, and they can be denoted in the form of  $t = vertical_op_{fw}()$ , where t is a register with a certain bit pattern. Table 3.3 shows the two operations.

#### The Vertical Unary Operations

These operations are in the form of  $t = vertical_op_{fw}(a)$ , where fw is the field width, a is the only argument which can be either a register or an immediate value, and t is the result register. Table 3.4 lists all the vertical unary operations with detailed description.

| Operation | Meaning                            | Description                           |

|-----------|------------------------------------|---------------------------------------|

| himask    | return a register with the high    | $t_i = ((1 << (fw/2)) - 1) << (fw/2)$ |

|           | half part of each field all set to |                                       |

|           | be 1 while the low half part of    |                                       |

|           | each field all set to be $0$       |                                       |

| lomask    | return a register with the high    | $t_i = (1 << (fw/2)) - 1$             |

|           | half part of each field all set to |                                       |

|           | be 0 while the low half part of    |                                       |

|           | each field all set to be 1         |                                       |

Table 3.3: The Vertical Bitmask Operations

| Operation   | Meaning                            | Description                                       |

|-------------|------------------------------------|---------------------------------------------------|

| abs         | calculate the absolute value of    | $t_i = -a_i$ if $Signed(a_i) < 0$ else $a_i$      |

|             | each field                         |                                                   |

| neg         | negate each field                  | $t_i = -Signed(a_i)$                              |

| $add_{-}hl$ | add the high and low half          | $t_i = High_{fw}(a_i) + Low_{fw}(a_i)$            |

|             | parts of each field                |                                                   |

| $xor_hl$    | bitwise xor the high and low       | $t_i = High_{fw}(a_i) \text{ xor } Low_{fw}(a_i)$ |

|             | half parts of each field           |                                                   |

| popcount    | bit counting in each field         | $t_i$ = the number of 1 bits in $a_i$             |

| ctz         | count trailing zeros in each       | $t_i$ = the number of consecutive 0 bits          |

|             | field                              | in $a_i$ counting from the right                  |

| constant    | return a register with every       | $t_i = a$                                         |

|             | field set to be the same value     |                                                   |

|             | specified in $a$ , where $a$ is an |                                                   |