# OPERATING SYSTEM ABSTRACTIONS OF HARDWARE ACCELERATORS ON FIELD-PROGRAMMABLE GATE ARRAYS

by

Aws Ismail B.A.Sc. EE (Hons.), University of Windsor, 2005

A THESIS SUBMITTED IN PARTIAL FULFILLMENT

OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in the

School of Engineering Science

Faculty of Applied Science

© Aws Ismail 2011

SIMON FRASER UNIVERSITY

Summer 2011

All rights reserved.

However, in accordance with the Copyright Act of Canada, this work may be reproduced without authorization under the conditions for Fair Dealing. Therefore, limited reproduction of this work for the purposes of private study, research, criticism, review and news reporting is likely to be in accordance with the law, particularly if cited appropriately.

## APPROVAL

| Name:                | Aws Ismail                                                                                                   |

|----------------------|--------------------------------------------------------------------------------------------------------------|

| Degree:              | Master of Applied Science                                                                                    |

| Title of Thesis:     | Operating System Abstractions of Hardware Accelera-<br>tors on Field-Programmable Gate Arrays                |

| Examining Committee: | <b>Dr. Carlo Menon</b><br>Assistant Professor, School of Engineering Science<br>Chair                        |

|                      | <b>Dr. Lesley Shannon, P.Eng.</b><br>Assistant Professor, School of Engineering Science<br>Senior Supervisor |

|                      | <b>Dr. Arrvindh Shriraman</b><br>Assistant Professor, School of Computing Science<br>Supervisor              |

|                      | Dr. Alexandra Fedorova<br>Assistant Professor, School of Computing Science<br>External Examiner              |

Date Approved:

August 19, 2011

## Partial Copyright Licence

SF

The author, whose copyright is declared on the title page of this work, has granted to Simon Fraser University the right to lend this thesis, project or extended essay to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its users.

The author has further granted permission to Simon Fraser University to keep or make a digital copy for use in its circulating collection (currently available to the public at the "Institutional Repository" link of the SFU Library website (www.lib.sfu.ca) at http://summit/sfu.ca and, without changing the content, to translate the thesis/project or extended essays, if technically possible, to any medium or format for the purpose of preservation of the digital work.

The author has further agreed that permission for multiple copying of this work for scholarly purposes may be granted by either the author or the Dean of Graduate Studies.

It is understood that copying or publication of this work for financial gain shall not be allowed without the author's written permission.

Permission for public performance, or limited permission for private scholarly use, of any multimedia materials forming part of this work, may have been granted by the author. This information may be found on the separately catalogued multimedia material and in the signed Partial Copyright Licence.

While licensing SFU to permit the above uses, the author retains copyright in the thesis, project or extended essays, including the right to change the work for subsequent purposes, including editing and publishing the work in whole or in part, and licensing other parties, as the author may desire.

The original Partial Copyright Licence attesting to these terms, and signed by this author, may be found in the original bound copy of this work, retained in the Simon Fraser University Archive.

Simon Fraser University Library Burnaby, British Columbia, Canada

revised Fall 2011

## Abstract

Traditionally, one of the main functions of the Operating System (OS) is to abstract the programming model from the low level details of the specific HW platform resources. However, in an FPGA-based SoC with HW accelerators, even with an OS layer, there is no unified HW/SW framework that provides: 1) transparency to the SW designer at the application level; and 2) an interface and OS support for easy HW accelerator integration by the HW designer at the platform level.

This thesis presents a *Front-end USEr* framework, called FUSE, that introduces a set of policies and mechanisms for HW accelerator abstraction. We illustrate FUSE as an API for an embedded Linux OS with POSIX threads on Xilinx's MicroBlaze on a Virtex5 FPGA. For three different applications and HW accelerators, we achieve performance speedups ranging from 5.8-9.0x.

## Contents

| $\mathbf{A}$                  | ppro  | val                                    | ii         |

|-------------------------------|-------|----------------------------------------|------------|

| A                             | bstra | ict                                    | iii        |

| C                             | onter | $\operatorname{nts}$                   | iv         |

| $\mathbf{Li}$                 | st of | Tables                                 | vii        |

| $\mathbf{Li}$                 | st of | Figures                                | <b>iii</b> |

| 1 Introduction                |       |                                        | 1          |

|                               | 1.1   | Motivation                             | 2          |

|                               | 1.2   | Objective                              | 4          |

|                               | 1.3   | Contributions                          | 5          |

|                               | 1.4   | Thesis Organization                    | 6          |

| 2 Background and Related Work |       | kground and Related Work               | 7          |

|                               | 2.1   | Modern FPGAs                           | 7          |

|                               | 2.2   | FPGA-based SoCs                        | 11         |

|                               |       | 2.2.1 Soft Processors State of the Art | 11         |

|   |     | 2.2.2  | Using HW Accelerators with Soft Processors $\hdots$ | 12        |

|---|-----|--------|-----------------------------------------------------|-----------|

|   | 2.3 | Opera  | ting Systems for FPGA-based SoCs                    | 13        |

|   |     | 2.3.1  | Traditional Role of the OS                          | 14        |

|   |     | 2.3.2  | OS support for FPGA-based SoCs                      | 15        |

|   | 2.4 | Previo | bus Work on Accelerator/OS Integration              | 18        |

| 3 | Pro | posed  | FUSE Framework                                      | <b>24</b> |

|   | 3.1 | FUSE   | Framework Overview                                  | 24        |

|   | 3.2 | FUSE   | Framework Organization                              | 26        |

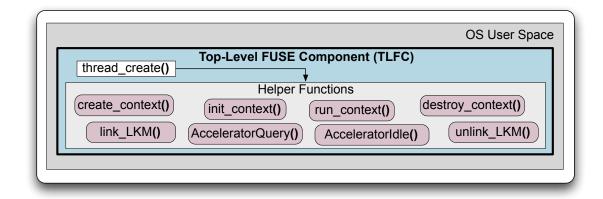

|   |     | 3.2.1  | Top-Level FUSE Component (TLFC)                     | 27        |

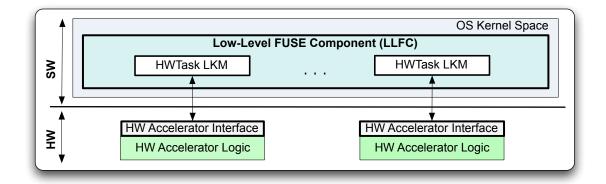

|   |     | 3.2.2  | Low-Level FUSE Component (LLFC)                     | 30        |

| 4 | FU  | SE Im  | plementation and Integration                        | 32        |

|   | 4.1 | User-s | space Implementation of TLFC                        | 33        |

|   |     | 4.1.1  | FUSE API Helper Functions                           | 35        |

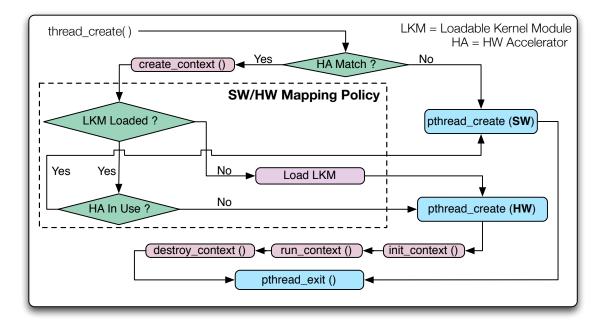

|   |     | 4.1.2  | Thread Creation                                     | 36        |

|   | 4.2 | Kerne  | l-space Implementation of LLFC                      | 40        |

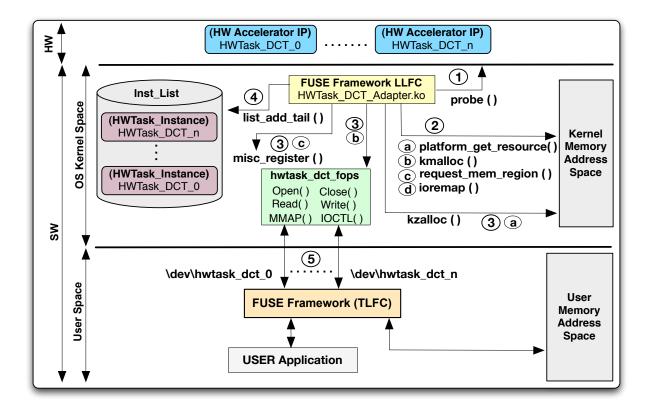

|   |     | 4.2.1  | LKM Architecture                                    | 41        |

|   |     | 4.2.2  | LKM File Operations                                 | 44        |

|   |     | 4.2.3  | LKM Registration/Initialization Procedure           | 44        |

|   | 4.3 | Hardv  | vare Accelerator Interface                          | 47        |

| 5 | Eva | luatio | n and Experimental Results                          | 50        |

|   | 5.1 | Hardv  | vare Experimental Setup                             | 51        |

|   |     | 5.1.1  | Resource Utilization                                | 52        |

|   |     | 5.1.2  | PetaLinux OS Versions                               | 53        |

| Bi | bliog | graphy |                                        | <b>74</b> |

|----|-------|--------|----------------------------------------|-----------|

|    | 6.3   | Future | e Work                                 | 72        |

|    | 6.2   | Conclu | usions                                 | 71        |

|    | 6.1   | Contri | butions                                | 70        |

| 6  | Con   | clusio | n and Future Work                      | 70        |

|    |       | 5.3.2  | Run-time Overhead                      | 64        |

|    |       | 5.3.1  | LKM loading/unloading overhead         | 62        |

|    | 5.3   | FUSE   | Overhead                               | 62        |

|    |       | 5.2.5  | Discussion of Case Studies Results     | 60        |

|    |       | 5.2.4  | Image Filtering Application            | 59        |

|    |       | 5.2.3  | 3DES Encryption/Decryption Application | 57        |

|    |       | 5.2.2  | Image Compression Application          | 55        |

|    |       | 5.2.1  | Testing Methodology                    | 54        |

|    | 5.2   | Exam   | ple Case Studies                       | 54        |

## List of Tables

| 4.1 | FUSE Helper Functions                                                    | 34 |

|-----|--------------------------------------------------------------------------|----|

| 4.2 | Overview of the key POSIX API functions vs. FUSE API $\ \ldots \ \ldots$ | 37 |

| 5.1 | System Resource Utilization on a Virtex5 FPGA                            | 52 |

| 5.2 | Utilization on a Virtex5 FPGA for the example HW Accelerator Inter-      |    |

|     | faces                                                                    | 52 |

# List of Figures

| 2.1 | A top-level block diagram of an FPGA architecture                      | 8  |

|-----|------------------------------------------------------------------------|----|

| 2.2 | Floor plan of Xilinx's Virtex 5 FPGA, consisting of configurable logic |    |

|     | blocks, BRAMs, Hard processor Blocks, DSP Blocks, etc                  | 9  |

| 3.1 | A high-level view of HW Accelerators as HW tasks                       | 25 |

| 3.2 | FUSE System Architecture                                               | 27 |

| 3.3 | FUSE Top-Level Component                                               | 28 |

| 3.4 | Decision Flow for Top-Level FUSE Component                             | 29 |

| 3.5 | FUSE Low-Level Component                                               | 31 |

| 4.1 | Partial source-code of an application using FUSE                       | 33 |

| 4.2 | Partial code showing the context structure definition                  | 36 |

| 4.3 | $thread\_create()$ definition inside $< fuse.h >$ header file          | 38 |

| 4.4 | Partial code showing part of the DCT LKM implementation                | 42 |

| 4.5 | The DCT LKM's entry/exit points functions                              | 45 |

| 4.6 | The DCT LKM's Probe() function execution procedure                     | 46 |

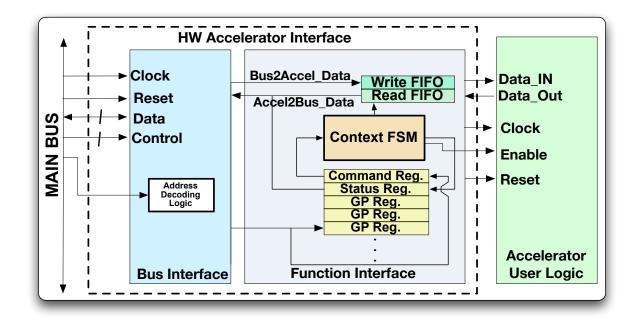

| 4.7 | HW Accelerator Interface                                               | 48 |

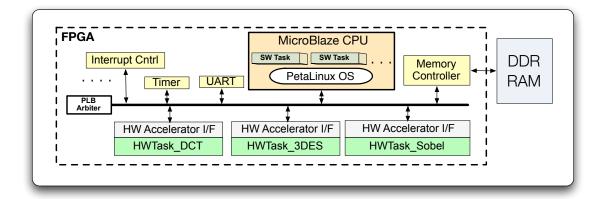

| 5.1 | Experimental System Architecture                                       | 51 |

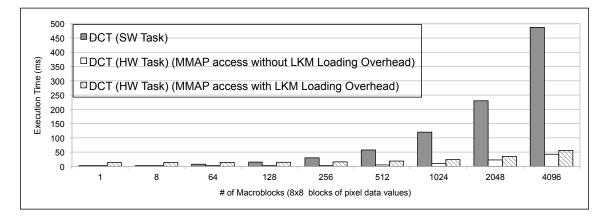

| 5.2  | Execution Time of the JPEG Encoder application with different imple-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | mentations for the DCT task (PetaLinux Ver. 0.4, SW-based timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|      | measurement)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56 |

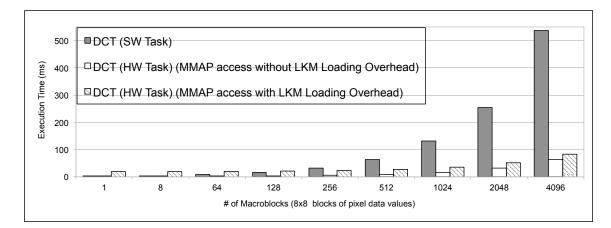

| 5.3  | Execution Time of the JPEG Encoder application with different imple-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|      | mentations for the DCT task (PetaLinux Ver. 2.1, HW-based timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|      | measurement)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56 |

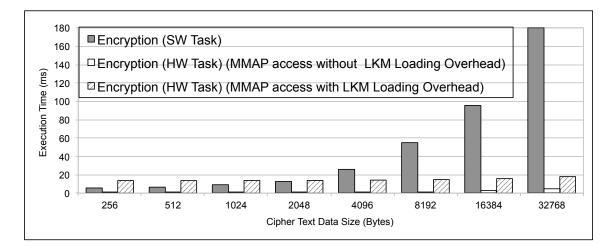

| 5.4  | Execution Time of 3DES application with different implementations for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|      | the encryption task (PetaLinux Ver. $0.4$ , SW-based timing measurement)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58 |

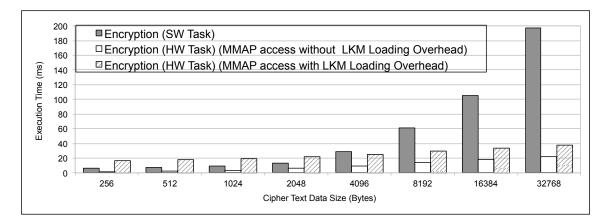

| 5.5  | Execution Time of 3DES application with different implementations for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|      | the encryption task (PetaLinux Ver. 2.1, HW-based timing measurement) $% \left( {{\left[ {{\left[ {{\left[ {\left[ {\left[ {\left[ {\left[ {\left[ {\left[ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 59 |

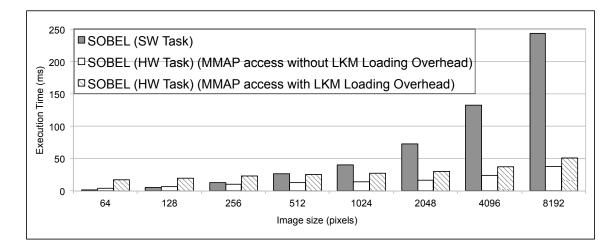

| 5.6  | Execution Time of the Image Filter application with different imple-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|      | mentations of the SOBEL task (PetaLinux Ver. 0.4, SW-based timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | measurement) $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60 |

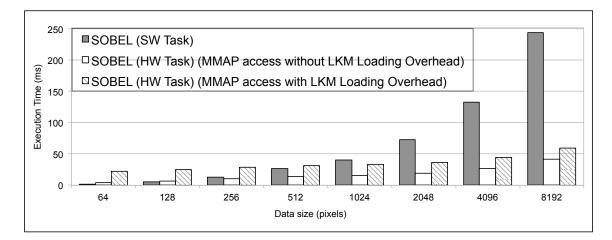

| 5.7  | Execution Time of the Image Filter application with different imple-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|      | mentations of the SOBEL task (PetaLinux Ver. 2.1, HW-based timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | measurement) $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61 |

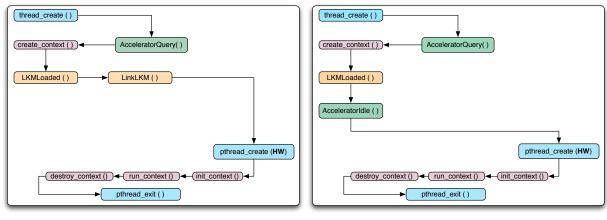

| 5.8  | TLFC mapping policy cases when loading an LKM $\ .\ .\ .\ .$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63 |

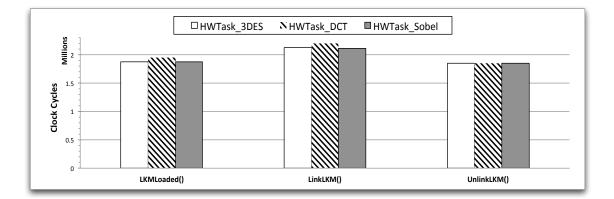

| 5.9  | Number of clock cycles incurred by the $LKMLoaded(), LinkLKM()$ and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | $\mathit{UnlinkLKM}()$ FUSE API helper functions (PetaLinux Ver. 2.1, HW-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | based timing measurement) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63 |

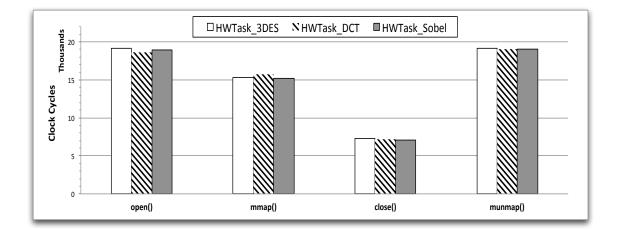

| 5.10 | Number of clock cycles when using the system calls within the $InitCon$ -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | text() (i.e. $open()$ , $mmap()$ ) and $DestroyContext()$ (i.e. $close()$ , $mun-interval destroyContext()$ (i.e. $close()$ , $mun-interval destroyContext()$ ) (i.e. $close()$ (i.e. $close()$ ) (i.e. $close()$ ) (i.e. $close()$ (i.e. $close()$ ) (i.e. $clo$ |    |

|      | map()) FUSE API helper functions (PetaLinux Ver. 2.1, HW-based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|      | timing measurement, CPU operating frequency of 125 MHz) $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64 |

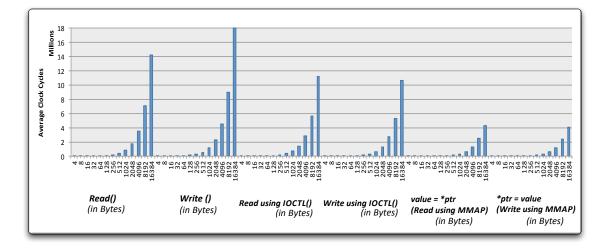

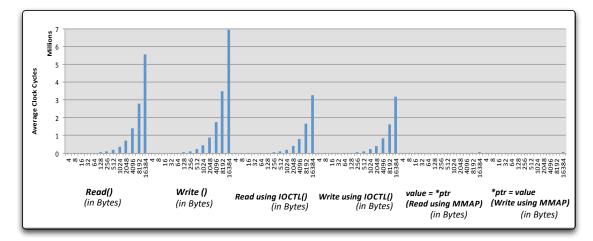

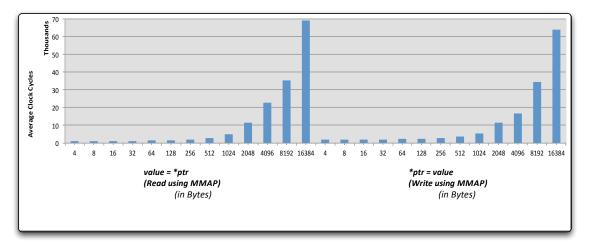

- 5.11 Average number of clock cycles for system calls for data communication when used within the *RunContext()* FUSE API helper function, when using PetaLinux version 2.1 with HW-based time measurements. . . . 65

- 5.12 Average number of clock cycles for system calls for data communication when used within the *RunContext()* FUSE API helper function, when using PetaLinux version 2.1 with SW-based time measurements . . . 69

## Chapter 1

## Introduction

In recent years, there has been a rising interest in reconfigurable devices, specifically in *Field Programmable Gate Arrays* (FPGAs) [1]. Initially, this rise in interest was due to the programmability of these devices, which is particularly useful during the development and prototyping stages of the circuit design process.

Due to their increasing density, FPGAs are able to implement complete Systemson-Chip (SoCs), like Application-Specific Integrated Circuits (ASICs), for computing solutions (e.g. embedded SoCs [2]). Furthermore, FPGA vendors now provide soft general-purpose processors (soft processors) to facilitate computing solutions that combine custom hardware (HW) Intellectual Property (IP) cores on the same FPGA device to create a heterogenous computing system. These custom HW cores are generally used to accelerate application execution time and thus are commonly called HW accelerators [3].

As FPGA-based SoCs increase in complexity and heterogeneity, there is an apparent need for improved system software (SW) support for their user applications. This support must come in the form of a middle layer, which provides transparency to hardware and software designers alike. Traditionally, this layer has been filled by the Operating System (OS), which abstracts the underlying hardware and at the same time enables portability and platform independence [1] [4]. Normally, adding an OS would help simplify the SW development process by hiding the low-level details of HW resources from the SW designer.

However, a traditional OS is challenged by the heterogeneity of computing systems implemented on FPGAs as they can combine one or more soft processor core(s) with dedicated HW processing elements (accelerators) that are intended to be used to achieve a performance speed-up compared to a SW-only solution. There is a need to extend the system software support provided in the the OS to better abstract HW accelerators as additional computing resources. This extension must be transparent to the SW designer, thus enabling efficient use of the HW accelerators.

#### 1.1 Motivation

Initially, FPGA vendors did not support an OS for their soft processors. A rather simple layer of system SW support was usually provided by the vendor to help setup an execution environment enabling user applications to run on the FPGA. However, adding an OS provides a better execution environment that: eases programming, increase portability, and releases software designers from managing and sharing system hardware resources (i.e., processors, memories, input/output peripherals). For FPGAbased SoC computing platforms, this level of abstraction, available in traditional computing workstations, does not exist. Specifically, for FPGA-based SoC computing platforms, traditional OS support is readily available but the additional complexities of abstracting HW accelerators have not been fully incorporated. Additionally, when targeting FPGA-based SoC computing platforms, software and hardware designers must face the inevitability of dealing with HW/SW co-design. HW/SW co-design [5] generally implies that an application will have software running on a CPU in conjunction with specialized hardware accelerators (i.e., hardware circuits specifically designed to speed up and parallelize the execution of performance demanding parts of the application). Although HW/SW co-design has been around for more than a decade [5], it still needs to alleviate some open problems, such as the increasing level of heterogeneity in FPGA-based SoCs. Traditional HW/SW codesign techniques normally view hardware accelerators as passive co-processors, thus, further widening the gap between software and hardware designers. This gap hinders design-space exploration and severely impairs the potential for design reuse.

As a motivation, we see that adding an OS can leverage the aforementioned gap between both sets of designers [1]. In its basic form, an OS is a software/hardware abstraction layer that abstracts a computing platform into a single virtual machine. Therefore, an OS is becoming increasingly common as it enables programming model abstractions that simplify programming by abstracting the low-level details of HW peripherals from the SW designer [4]. For an FPGA-based SoC, adding this layer is seen as a positive step, but it still lacks proper mechanisms that enable the software designer to view that computing platform as a general platform with an added benefit of achieving application performance speedup if possible [1].

The lack of proper mechanisms in current OS solutions impose limits on:

Communication between a software application and hardware accelerator(s): while writing user software & designing hardware accelerator(s), software and hardware designers have to be aware of specific interfacing details.

- 2. Available programming paradigms: advanced programming concepts such as multithreading assume unified memory space.

- 3. Portability of applications across different FPGA-based SoCs: it is burdensome for software designers to maintain their hardware-agnostic, high-level programming approaches, and it is challenging for hardware designers to design HW accelerators that can run across different platforms, without any change in the HDL code.

By extending OS support to include HW accelerators, the low-level HW interaction details can also be masked, facilitating the writing of programs that utilize HW accelerators efficiently.

### 1.2 Objective

While there has been extensive research investigating operating system support for FPGAs in general, and FPGA-based SoC computing platforms in particular, few have focused on providing an abstraction to leverage their heterogenous aspect; specifically when the system has one or more hardware accelerators. Our objective is to allow the user to customize the operating system at runtime to support existing hardware accelerators as additional computing resources for software designers, allowing the OS to automatically schedule the application(s) to leverage them.

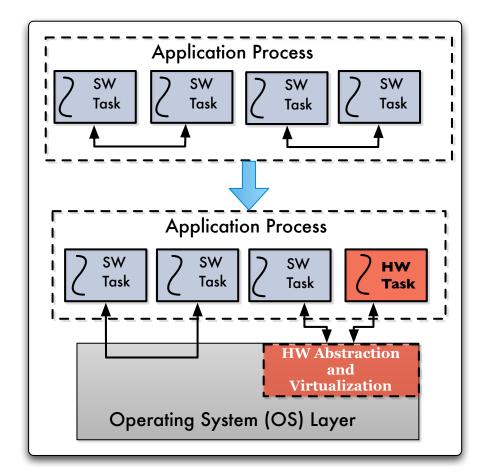

Given an FPGA-based SoC, we show the feasibility of facilitating SW designers use of HW accelerators. Our goal is to provide the same type of abstraction to HW accelerators, that is available to processors. Through a set of policies and mechanisms, the software designer is presented with a run-time framework that leverages the existence of hardware accelerators. We aim to show that programming models such as multitasking can be extended to enable software designers to view HW accelerators as possible HW tasks similar to SW tasks. We also quantify the overhead introduced by this abstraction and contrast it against the expected performance speed-up.

#### **1.3** Contributions

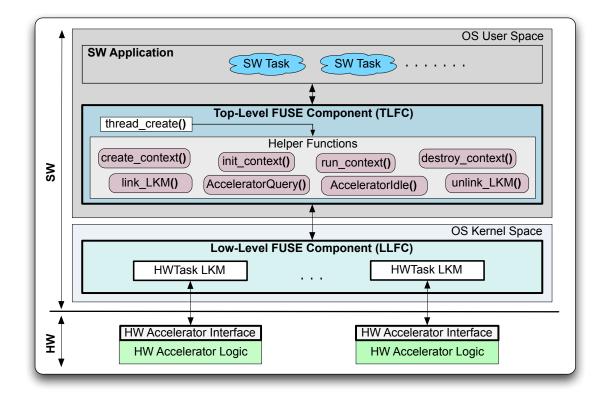

In this thesis, we demonstrate a Front-end USEr run-time framework, FUSE, for abstracting computing architectures from SW designers creating multithreaded applications. We show that using FUSE is beneficial for systems implemented on FPGAs, so HW designers can create and update HW accelerators to suit an application/user's changing requirements, independent of the SW designer. HW accelerators are virtualized from SW designers as hardware tasks (HW tasks) similar to [6] [7] in the context of a multithreading application. The contributions of this work are as follows:

- 1. A modular front-end user framework with a customizable data/control communication interface to HW accelerators.

- 2. OS Kernel support for *on-demand instantiation* of accelerators, similar to a SW dynamically linked library (DLL).

To demonstrate FUSE, we have designed a simple application programming interface (API) based on the POSIX thread standard and integrated it with the PetaLinux operating system [8] as a user library for a MicroBlaze CPU. We use a Xilinx Virtex 5 FPGA and three case studies to illustrate the overhead of loading OS support for an accelerator, along with negligible runtime overhead for the FUSE framework, resulting in performance speedups ranging from 5.8-9x.

### 1.4 Thesis Organization

The remainder of this thesis is organized as follows. Chapter 2 provides an overview of related work on OS support for systems with HW accelerators on FPGAs. Chapter 3 introduces the concepts and key ideas behind FUSE while Chapter 4 describes the implementation of FUSE components and its support for HW accelerator virtualization. Chapter 5 demonstrates the use of the FUSE framework, along with its overhead and performance speedups for a set of case studies. Finally, Chapter 6 summarizes the conclusions of the work and possible areas of future work.

## Chapter 2

## **Background and Related Work**

This chapter covers several aspects of reconfigurable computing, specifically focusing on FPGA-based, Systems-on-Chip (SoC), embedded computing platforms as an example. We also give an overview of the available OS support for such computing platforms as background for the FUSE framework presented in Chapter 3. Section 2.1 gives an overview of FPGAs. Section 2.2 gives and overview of FPGA-based SoCs by outlining the use of processors in such systems and then give an overview of hardware acceleration concepts. Finally, Section 2.3 looks at the existing research into operating system support for such systems and Section 2.4 discusses how our proposed solution relates to previous research on OS support for HW Accelerator integration.

### 2.1 Modern FPGAs

Field-programmable gate arrays (FPGAs) are integrated circuit (IC) devices that consist of an uncommitted array of logic resources, and are reprogrammable in both logic function and interconnect. Xilinx introduced the the symmetrical island-style

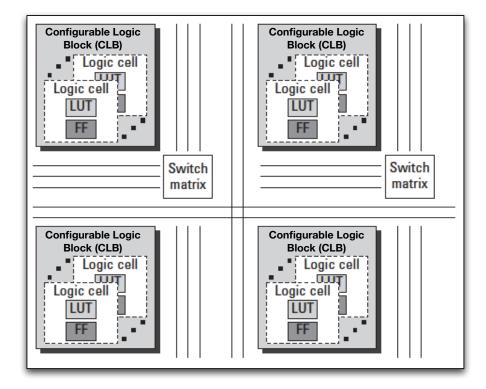

Figure 2.1: A top-level block diagram of an FPGA architecture

FPGA architecture, depicted in Figure 2.1, in the 1980s [9]. It consisted of a regular array of configurable logic blocks (CLBs), connected by interconnection networks, which were comprised of wiring channels connected by routing blocks, called *switch matrices*. The CLBs are comprised of *logic cells* containing look-up tables (LUTs) and registers or flip-flops (FFs). These logic cells allowed for flexible implementation of logic functions within the FPGA fabric, often distributed across several CLBs.

Since their inception, FPGA devices were commonly used for rapid prototyping during the ASIC system design life cycle. Many users of ASIC technologies began adding FPGAs as part of the design life cycle by switching to ASIC prototyping on FPGAs for lower cost functional verification and reduced design risks [10]. FPGAs were, and still are, used for reprogrammable implementations that allow the user to

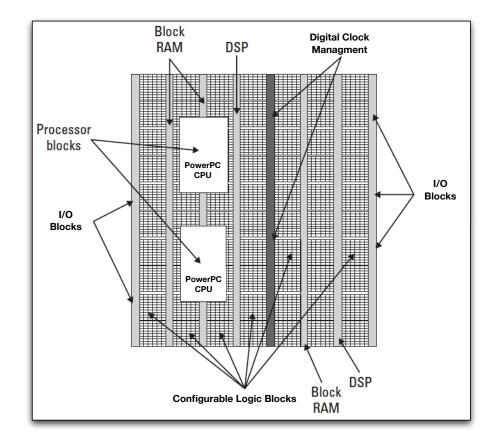

Figure 2.2: Floor plan of Xilinx's Virtex 5 FPGA, consisting of configurable logic blocks, BRAMs, Hard processor Blocks, DSP Blocks, etc.

make quick design changes for faster development time.

As FPGA densities increased, heterogenous components have been added by vendors, facilitating the implementation of complete SoCs on an FPGA similar to ASIC designs [10]. Users and researchers alike started to view FPGAs as a design platform for reconfigurable heterogenous SoCs [11] [12]. A typical SoC design uses these components as functional building blocks to improve the performance and area efficiency of the implemented circuits [2]. Most recent FPGA device families (e.g. Xilinx's Virtex 2 Pro [13], Virtex 5 [14], Virtex 7 [15], and Altera's Stratix [16] and Cyclone [17]) include such functional blocks and are marketed by vendors as implementation targets for complex SoCs.

For example, Figure 2.2 shows the floor plan of a Xilinx Virtex 5 FPGA and highlights the dedicated function blocks included within the reconfigurable fabric. Examples of these blocks include:

- Multipliers/DSP Blocks: To speed certain arithmetic functions often found in signal processing applications such as multiply-and-accumulate (MAC).

- Input/Output Blocks: The external pins of FPGAs are mapped to regularly distributed I/O Blocks (IOBs), which support a wide set of IO interface standards. Modern FPGA families also include specialized high-speed interfaces for serial communication protocols allowing the creation of multi-FPGA SoC platforms.

- Memory: Platform FPGAs now feature dedicated memory blocks called Block RAMs (BRAMs), which provide a higher density and better performance than LUT-based memory. Distributed within the FPGA chip area, these BRAMs can be used to implement read-only memories (ROMs), random-access memories (RAMs), and also storage elements such as First-In First-Out (FIFO) buffers and content-addressable memories (CAMs).

- Processor Intellectual Property (IP): They come in two forms, soft processors and hard processors. Soft processors are designed using HW description languages (e.g. VHDL) and can be synthesized onto a FPGA. Hard processors are part of the underlying FPGA fabric. Processors for FPGA-based SoC platforms are discussed in detail in Section 2.2.

In combination with integrated processor IPs and optional external memory (e.g. DDR SDRAM), the FPGA can implement an entire embedded computing system. FPGA-based Systems-on-Chip (SoCs) are now seen as a viable solution for building computing platforms for which hardware abstraction from SW designers (i.e. operating system support) becomes an important consideration [18] [19] [20]. These FPGA-based SoCs are the target implementation of the proposed framework in this thesis (see Chapter 5 for an example target platform).

#### 2.2 FPGA-based SoCs

A major advancement for FPGAs was the ability to include dedicated processors along with specialized custom HW. The combination of these two parts are key to FPGA-based SoC designs. This section deals with FPGA-based SoCs that have soft processor IPs along with custom HW blocks, called HW accelerators. In section 2.2.1 we give discuss the state of the art of processor IPs and soft processors, in particular. Section 2.2.2, gives and overview of using HW acceleration with soft processors to maximize the design performance.

#### 2.2.1 Soft Processors State of the Art

Although hard processors are available on some FPGA families (e.g. PowerPC is only available on certain devices of Xilinx's Virtex 2 Pro [13], Virtex 4, and Virtex 5 [14] families but not on Virtex 6 and Virtex 7 families [15]), it is now possible to define, build and customize a soft processor using any FPGA's available logic primitives [21].

While conventional processors were designed to be built using custom silicon or