# Data-Centric and Data-Aware Frameworks for Fundamentally Efficient Data Handling in Modern Computing Systems

by

#### Nastaran Hajinazar

M.Sc., Sharif University of Technology, 2011 B.Sc., Shahid Chamran University, 2008

Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

> in the School of Computing Science Faculty of Applied Sciences

© Nastaran Hajinazar 2021 SIMON FRASER UNIVERSITY Summer 2021

Copyright in this work is held by the author. Please ensure that any reproduction or re-use is done in accordance with the relevant national copyright legislation.

## Declaration of Committee

Name: Nastaran Hajinazar

Degree: Doctor of Philosophy

Thesis title: Data-Centric and Data-Aware Frameworks for

Fundamentally Efficient Data Handling in

Modern Computing Systems

Committee: Chair: Zhenman Fang

Assistant Professor, Engineering Science

Onur Mutlu

$\hbox{Co-Supervisor}$

Professor, Computing Science

ETH Zurich

#### Arrvindh Shriraman

Co-Supervisor

Associate Professor, Computing Science

#### Saugata Ghose

Committee Member

Assistant Professor, Computer Science University of Illinois at Urbana-Champaign

#### Vivek Seshadri

Committee Member Senior Researcher

Microsoft Research India

#### Alaa Alameldeen

Examiner

Associate Professor, Computing Science

#### Myoungsoo Jung

External Examiner

Associate Professor, Electrical Engineering

Korea Advanced Institute of Technology (KAIST)

## Abstract

There is an explosive growth in the size of the input and/or intermediate data used and generated by modern and emerging applications. Unfortunately, modern computing systems are not capable of handling large amounts of data efficiently. Major concepts and components (e.g., the virtual memory system) and predominant execution models (e.g., the processor-centric execution model) used in almost all computing systems are designed without having modern applications' overwhelming data demand in mind. As a result, accessing, moving, and processing large amounts of data faces important challenges in today's systems, making data a first-class concern and a prime performance and energy bottleneck in such systems. This thesis studies the root cause of inefficiency in modern computing systems when handling modern applications' data demand, and aims to fundamentally address such inefficiencies, with a focus on two directions.

First, we design a new framework that aids the widespread adoption of processing-using-DRAM, a data-centric computation paradigm that improves the overall performance and efficiency of the system when computing large amounts of data by minimizing the cost of data movement and enabling computation where the data resides. To this end, we introduce SIMDRAM, an end-to-end processing-using-DRAM framework that (1) efficiently computes complex operations required by modern data intensive applications, and (2) provides the ability to implement new arbitrary operations as required, all in an in-DRAM massively-parallel Single Instruction Multiple Data (SIMD) substrate that requires minimal changes to the DRAM (Dynamic Random Access Memory) architecture.

Second, we design a new, more scalable virtual memory framework that (1) eliminates the inefficiencies of the conventional virtual memory frameworks when handling the high memory demand in modern applications, and (2) is built from the ground up to understand, convey, and exploit data properties, to create opportunities for performance and efficiency improvements. To this end, we introduce the Virtual Block Interface (VBI), a novel virtual memory framework that (1) efficiently handles modern applications' high data demand, (2) conveys properties of different pieces of program data (e.g., data structures) to the hardware and exploits this knowledge for performance and efficiency optimizations, (3) better extracts performance from the wide variety of new system configurations that are designed to process large amounts of data (e.g., hybrid memory systems), and (4) provides all the key features of the conventional virtual memory frameworks, at low overhead.

Keywords: Data-centric; Data-aware; Efficient data handling; Virtual memory; Computing-

using-DRAM; Processing-in-memory

# Dedication

#### Dedicated to

my beloved parents, Ezzatollah and Homa, my wonderful brothers, Samad and Siavash, my lovely husband, Amir, and my most precious son, Nick Ray.

## Acknowledgements

Pursuing a PhD was a significant source of learning, inspiration and growth for me, to which many people have contributed in different ways. This is a humble attempt to thank them for their contribution and for helping me become who I am today.

First and foremost, I would like to express my deep and sincere gratitude to my advisor, Prof. Onur Mutlu, who believed in me, even when I did not. His unwavering support, despite the tough initial years, was my prime source of courage towards the completion of my PhD. Onur generously provided me with invaluable guidance, exceptional opportunities, incredible resources, and more importantly, extraordinary freedom to carry out my research. I also thank him for teaching me how to think critically, write thoroughly, speak clearly, and perform impactful research. His influence in shaping me certainly goes above and beyond this dissertation and extends to countless real-life lessons that I have learned from him.

I would like to thank my advisor, Prof. Arryindh Shriraman, for all his help and support. I thank him for allowing me to find and follow the research direction that interested me. I also thank him for being open to my collaborations with students and researchers from other institutions.

I would also like to thank the members of my supervisory committee, Prof. Saugata Ghose and Dr. Vivek Seshadri. I thank Prof. Ghose for providing me with incredible technical and moral support and countless pieces of critical advice throughout my PhD journey. He helped me stay focused and navigate through my research with a clear and determined mind. My earnest thanks to Dr. Seshadri for teaching me how to find the right research problem to work on and how to perform quality research. I thank him for all his help and support through the times that I needed it the most.

During my PhD, I had the chance to work alongside many wonderful fellow graduate students at the SAFARI research group whom I am grateful to. My great friend, Giray Yaglikci was always amazingly kind and selfless in helping me and listening to me during the times when graduate school felt dark and lonely. I would like to thank him for all his support, as well as the hot cups of tea and delicious food that rescued me with when working late at school. Geraldo De Oliveira was my PIM guru, whose kind presence as well as his amazing home-made cakes and cookies brightened up my days at ETH. Minesh Patel has been a great friend with whom I have also enjoyed many research collaborations and real-life conversations. Juan Gómez Luna was my mentor and collaborator who assisted me in many

ways. Kevin Hsieh was an extraordinary friend and mentor who was there to listen to me and support me when I was in need. Rachata Ausavarungnirun was a good friend who also taught me a great deal about how to conduct thorough simulations and evaluations. Damla Senol Cali was my sweet and kind friend and collaborator who was always there to support me and celebrate my achievements with me. Gagandeep Singh was a wonderful collaborator and friend who always amused me with his great sense of humor. I thank Can Firtina for his delightful friendship as well as the high-tech Tesla rides. I would also like to thank many other SAFARI members for their friendship and collaboration: Jeremie Kim, Mohammed Alser, Jawad Haj-Yahya, Lois Orosa, Jisung Park, Hasan Hassan, Tracy Ewen, and Christian Rossi.

I would also like to thank many wonderful people who made the long and at times tough journey of pursuing PhD easier for me, and I am lucky to call them my friends: Rajesh Rao, Sogol Barazandegan, Nasibeh Teimouri, Amir Shabani, and Ahmed Hamza.

And last, but not least, I would like to express my profound gratitude to my family for their unconditional and continued love and support. I am most grateful to my parents, Ezzatollah Hajinazar and Homa Golabian, for enabling me to pursue my passion for learning, and for being by my side at each and every step of this journey. I thank my mother for selflessly caring for me and for teaching me by example, the importance of hard work, perseverance, and integrity. I thank my father for always believing in me and for teaching me the important lesson that nothing is impossible if you fight for it. I thank my lovely brothers, Samad and Siavash Hajinazar, for their immense and unwavering love and support which has been a sublime source of motivation for me. I would like to give my heartfelt thanks to my wonderful husband, Amir Pourmand, for being my rock, my number one supporter, and my safe place. This thesis would have been impossible without him by my side. Finally, I thank my most precious son, Nick Ray, whose little kicks kept me motivated during the writing of this dissertation. Words will never be able to describe my love for him. He will always be the reason behind my smile and I am eternally proud and grateful to be his mother.

# Contents

| Declaration of Committee |        |                                                                           | ii   |

|--------------------------|--------|---------------------------------------------------------------------------|------|

| A                        | bstra  | act                                                                       | iii  |

| D                        | edica  | ation                                                                     | v    |

| $\mathbf{A}$             | cknov  | wledgements                                                               | vi   |

| Ta                       | able ( | of Contents                                                               | viii |

| Li                       | st of  | Tables                                                                    | xi   |

| Li                       | st of  | Figures                                                                   | xii  |

| 1                        | Intr   | roduction                                                                 | 1    |

|                          | 1.1    | Motivation: Existing Computing Systems Are Designed Without Having        |      |

|                          |        | Modern Applications' Data Demand in Mind                                  | 1    |

|                          | 1.2    | Our Approach: Data-Centric and Data-Aware Architectures for Fundamentally |      |

|                          |        | Efficient Data Handling                                                   | 3    |

|                          |        | 1.2.1 Thesis Statement                                                    | 4    |

|                          | 1.3    | Overview of Research                                                      | 4    |

|                          |        | 1.3.1 SIMDRAM: A Data-Centric Framework for Bit-Serial SIMD Process-      |      |

|                          |        | ing using DRAM (Chapter 2)                                                | 5    |

|                          |        | 1.3.2 The Virtual Block Interface: A Flexible Data-Aware Alternative to   |      |

|                          |        | the Conventional Virtual Memory Framework (Chapter 3)                     | 6    |

|                          | 1.4    | Contributions                                                             | 8    |

| <b>2</b>                 | SIM    | IDRAM                                                                     | 9    |

|                          | 2.1    | Background                                                                | 12   |

|                          |        | 2.1.1 DRAM Basics                                                         | 12   |

|                          |        | 2.1.2 Processing-using-DRAM                                               | 13   |

|                          | 2.2    | SIMDRAM Overview                                                          | 15   |

|                          |        | 2.2.1 Subarray Organization                                               | 15   |

|         | 2.2.2         | Framework Overview                                                                                                          |

|---------|---------------|-----------------------------------------------------------------------------------------------------------------------------|

|         | 2.2.3         | Integrating SIMDRAM in a System                                                                                             |

| 2.3     | SIMD          | RAM Framework                                                                                                               |

|         | 2.3.1         | Step 1: Efficient MAJ/NOT Implementation                                                                                    |

|         | 2.3.2         | Step 2: µProgram Generation                                                                                                 |

|         | 2.3.3         | Step 3: Operation Execution                                                                                                 |

|         | 2.3.4         | Supported Operations                                                                                                        |

| 2.4     | System        | m Integration of SIMDRAM                                                                                                    |

|         | 2.4.1         | Data Layout                                                                                                                 |

|         | 2.4.2         | ISA Extensions and Programming Interface                                                                                    |

|         | 2.4.3         | Handling Page Faults, Address Translation, Coherence, and Interrupts 30                                                     |

|         | 2.4.4         | Handling Limited Subarray Size                                                                                              |

|         | 2.4.5         | Security Implications                                                                                                       |

|         | 2.4.6         | SIMDRAM Limitations                                                                                                         |

| 2.5     | Metho         | odology $\dots \dots \dots$ |

| 2.6     | Evalua        | ation                                                                                                                       |

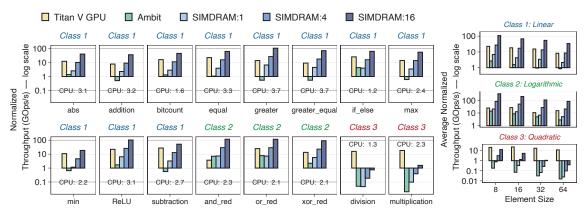

|         | 2.6.1         | Throughput Analysis                                                                                                         |

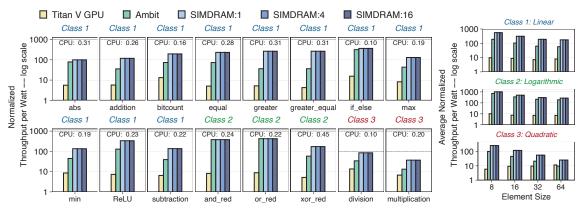

|         | 2.6.2         | Energy Analysis                                                                                                             |

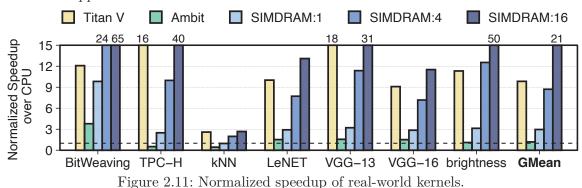

|         | 2.6.3         | Effect on Real-World Kernels                                                                                                |

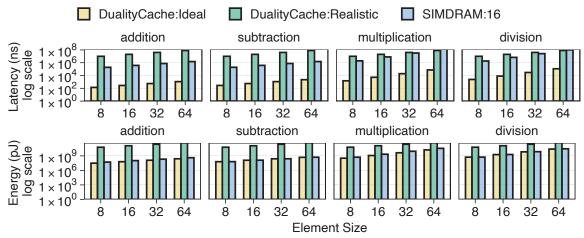

|         | 2.6.4         | Comparison to DualityCache                                                                                                  |

|         | 2.6.5         | Reliability                                                                                                                 |

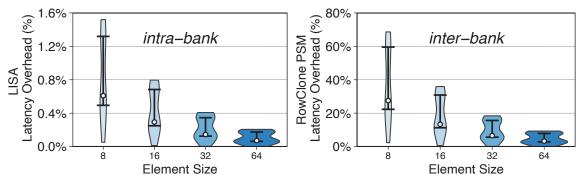

|         | 2.6.6         | Data Movement Overhead                                                                                                      |

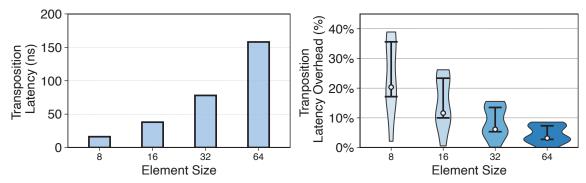

|         | 2.6.7         | Data Transposition Overhead                                                                                                 |

|         | 2.6.8         | Area Overhead                                                                                                               |

| 2.7     | Relate        | ed Work                                                                                                                     |

| 2.8     | Summ          | nary and Contributions                                                                                                      |

| (ID)    | <b>T</b> 7°   | al Dia i Tata Cara                                                                                                          |

|         |               | al Block Interface 44 Principles                                                                                            |

| 3.1 3.2 | 0             | a Principles                                                                                                                |

| ე.∠     | 3.2.1         | VBI Address Space                                                                                                           |

|         | 3.2.1 $3.2.2$ | VBI Access Permissions                                                                                                      |

|         | 3.2.3         | Memory Translation Layer                                                                                                    |

|         | 3.2.4         | Implementing Key OS Functionalities                                                                                         |

|         | 3.2.4         | Optimizations Supported by VBI                                                                                              |

| 3.3     |               | Detailed Design                                                                                                             |

| ა.ა     | 3.3.1         | Architectural Components                                                                                                    |

|         | 3.3.2         | Life Cycle of Allocated Memory                                                                                              |

|         | 3.3.3         | CVT Cache                                                                                                                   |

|         | 0.0.0         | OVI Cache                                                                                                                   |

3

|                                      |       | 3.3.4  | Processor, OS, and Process Interactions                          | 57   |

|--------------------------------------|-------|--------|------------------------------------------------------------------|------|

|                                      |       | 3.3.5  | Memory Translation Layer                                         | 59   |

|                                      | 3.4   | Alloca | ation and Translation Optimizations                              | . 61 |

|                                      |       | 3.4.1  | Delayed Physical Memory Allocation                               | . 61 |

|                                      |       | 3.4.2  | Flexible Address Translation Structures                          | . 61 |

|                                      |       | 3.4.3  | Early Reservation of Physical Memory                             | 62   |

|                                      | 3.5   | VBI in | n Other System Architectures                                     | 63   |

|                                      |       | 3.5.1  | Supporting Virtual Machines                                      | 63   |

|                                      |       | 3.5.2  | Supporting Multi-Node Systems                                    | 63   |

|                                      | 3.6   | Evalua | ation                                                            | 64   |

|                                      |       | 3.6.1  | Methodology                                                      | 64   |

|                                      |       | 3.6.2  | Use Case 1: Address Translation                                  | 65   |

|                                      |       | 3.6.3  | Use Case 2: Memory Heterogeneity                                 | 68   |

|                                      | 3.7   | Relate | ed Work                                                          | 70   |

|                                      | 3.8   | Summ   | nary and Contributions                                           | 72   |

| 4                                    | Con   | clusio | ns and Future Work                                               | 73   |

| -                                    | 4.1   |        | usions                                                           | 73   |

|                                      | 4.2   |        | e Work                                                           | 74   |

|                                      | 1.2   | 4.2.1  | Data-Aware Memory Architectures                                  | 74   |

|                                      |       | 4.2.2  | Enabling Support for Designing New Unconventional Memory Subsys- | • •  |

|                                      |       | 11212  | tems                                                             | 75   |

|                                      |       | 4.2.3  | Virtual Memory Support for Processing-Using-Memory architectures | 75   |

| 5                                    | Oth   | er Wo  | orks of the Author                                               | 76   |

| $\mathbf{B}^{\mathbf{i}}$            | bliog | graphy |                                                                  | 78   |

| $\mathbf{A}_{]}$                     | ppen  | dix A  | AIG-to-MIG Conversion                                            | 106  |

| $\mathbf{A}_{]}$                     | ppen  | dix B  | Row-to-Operand Allocation                                        | 109  |

| Appendix C Scalability of Operations |       |        |                                                                  | 112  |

| A                                    | ppen  | dix D  | Evaluated Real-World Applications                                | 113  |

# List of Tables

| Table 2.1 | SIMDRAM ISA extensions                              | 29 |

|-----------|-----------------------------------------------------|----|

| Table 2.2 | Evaluated system configurations                     | 33 |

| Table 2.3 | Process variation's effect on TRA/QRA failure rates | 38 |

| Table 3.1 | Simulation configuration                            | 64 |

| Table 3.2 | Multiprogrammed workload bundles                    | 68 |

# List of Figures

| Figure 2.1  | High-level overview of DRAM organization                            |

|-------------|---------------------------------------------------------------------|

| Figure 2.2  | SIMDRAM subarray organization [338]                                 |

| Figure 2.3  | Overview of the SIMDRAM framework                                   |

| Figure 2.4  | Data layout: horizontal vs. vertical                                |

| Figure 2.5  | (a) Optimized MIG; (b) row-to-operand allocation; (c) µProgram for  |

|             | full addition                                                       |

| Figure 2.6  | μOps and μRegisters in SIMDRAM                                      |

| Figure 2.7  | SIMDRAM control unit                                                |

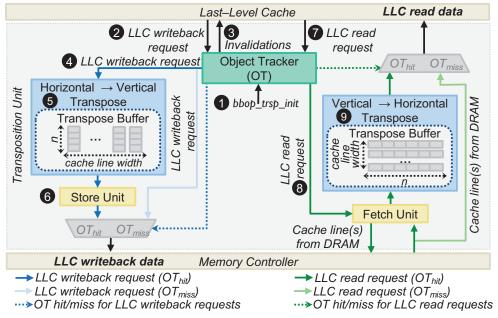

| Figure 2.8  | Major components of the data transposition unit                     |

| Figure 2.9  | Normalized throughput of 16 operations. SIMDRAM:<br>X uses X DRAM   |

|             | banks for computation                                               |

| Figure 2.10 | Normalized energy efficiency of 16 operations                       |

| Figure 2.11 | Normalized speedup of real-world kernels                            |

| Figure 2.12 | Latency and energy to execute 64M operations                        |

| Figure 2.13 | Latency overhead distribution of worst-case intra-bank (left) and   |

|             | inter-bank (right) data movement for SIMDRAM:1. Error bars depict   |

|             | the 25th and 75th percentiles                                       |

| Figure 2.14 | Worst-case latency (left) and worst-case latency overhead distribu- |

|             | tion (right) of data transposition in 16 SIMDRAM operations for     |

|             | SIMDRAM:1. Error bars depict the 25th and 75th percentiles, and a   |

|             | bubble depicts the 50th percentile                                  |

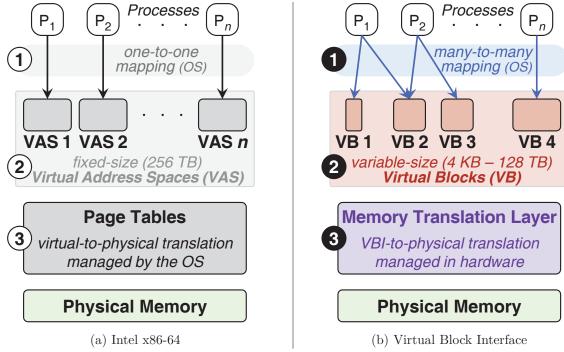

| Figure 3.1  | Virtual memory management in x86-64 and in VBI                      |

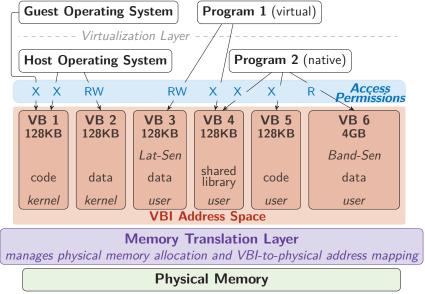

| Figure 3.2  | Overview of VBI. Lat-Sen and Band-Sen represent latency-sensitive   |

|             | and bandwidth-sensitive, respectively                               |

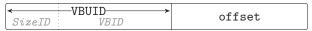

| Figure 3.3  | Components of a VBI address                                         |

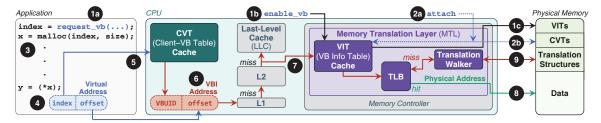

| Figure 3.4  | Reference microarchitectural implementation of the Virtual Block    |

|             | Interface                                                           |

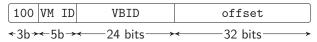

| Figure 3.5  | Partitioning the VBI address space among virtual machines, using    |

|             | the 4 GB size class (100) as an example                             |

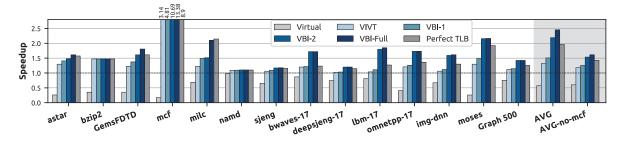

| Figure 3.6  | Performance of systems with 4KB pages (normalized to Native) 64     |

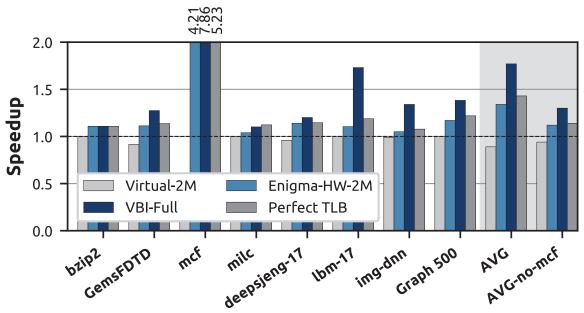

| Figure 3.7  | Performance with large pages (norm. to Native-2M)                   |

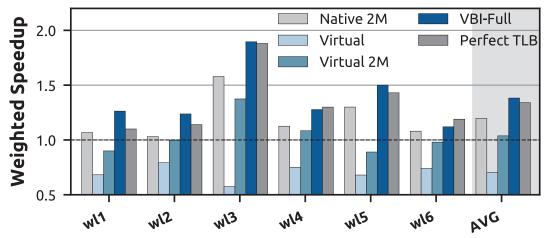

| Figure 3.8  | Multiprogrammed workload performance (normalized to Native)        | 68 |

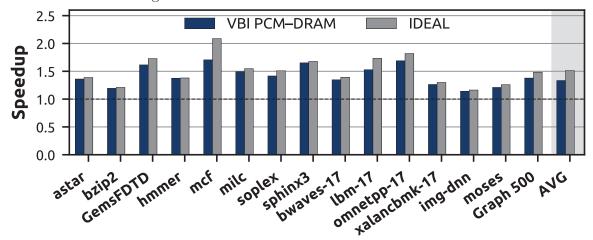

|-------------|--------------------------------------------------------------------|----|

| Figure 3.9  | Performance of VBI PCM-DRAM (normalized to data-hotness-unaware $$ |    |

|             | mapping)                                                           | 69 |

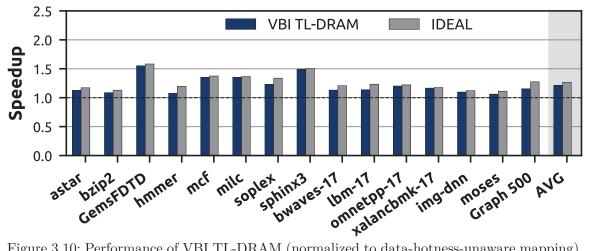

| Figure 3.10 | Performance of VBI TL-DRAM (normalized to data-hotness-unaware     |    |

|             | mapping)                                                           | 69 |

## Chapter 1

## Introduction

Modern computing systems need to process increasingly large amounts of data. Many key applications and workloads of important and wide range of domains (e.g., data mining, machine learning, graph and text analytics, databases, augmented reality applications, and genome analysis) and their potential improvement depend on fast and efficient processing of large data volumes. With the advent of such applications, computing in modern systems is primarily bottlenecked by data. In other words, by how fast and efficient we are in accessing, moving and processing data. Unfortunately, modern computing systems do not handle (i.e., store, access, and process) data well. The large amount of input and intermediate data required by modern applications overwhelms many of the key components of the modern computing systems. As a result, data has become a prime bottleneck in today's computing systems, making it challenging to efficiently support important emerging applications with high data demand.

The importance of handling the large amount of data processed by modern applications in an efficient manner has inspired a large body of research in processor design, memory and storage architectures, and key system components. However, we argue that fundamentally efficient handling of the increasing data demand in modern applications requires a holistic rethinking of the key concepts and components used in modern computing systems.

# 1.1 Motivation: Existing Computing Systems Are Designed Without Having Modern Applications' Data Demand in Mind

Today's computing systems have two important characteristics that make it significantly challenging to efficiently handle large amounts of data:

Characteristic 1: Processor-Centric Architectures. Modern computing systems follow the *processor-centric paradigm* in which computation is performed only in the processor (or compute-centric accelerators) and every piece of data needs to be transferred to/from main memory to enable the computation. The increasing prevalence and growing size of data in modern applications has made data movement between memory devices (e.g., DRAM)

and the processor across bandwidth-limited memory channels a first-class performance and energy bottleneck. For example, a recent work [51] shows that the energy and performance costs of data movement across the memory hierarchy are significantly higher than that of computation, consuming more than 60% of the total system energy, when executing four major commonly-used consumer workloads, including machine learning inference, video processing and playback, and web browsing. Furthermore, in a processor-centric configuration, every component in the system except the processor is designed to serve the processor by storing and accessing the data or moving it to the processor for computation. This leads to about 80-95% of the chip area to be consumed by the components that are solely responsible for storing, accessing and moving the data to the processor [270]. Spending the majority of the chip resources on elements that are not able to process data or understand and take advantage of the properties of the data is not the right mindset considering the advent of applications that require fast, efficient, and intelligent computation of significantly large volumes of data.

We conclude that the processor-centric paradigm as the predominant execution model used in almost all computing systems is designed without having modern applications' overwhelming data demand in mind, causing significant waste in terms of energy and performance by requiring frequent data movement across the entire system. This causes data to become a first-class concern and a prime performance and energy bottleneck in the system, which makes it challenging to efficiently support important emerging applications with high data demand in today's computing systems.

Characteristic 2: Data-Oblivious Policies. In order to cater to the high and diverse memory requirements of modern applications, today's computing systems employ increasingly larger main memories [56,165,211,212,261,266–268,273,277,318,346] and heterogeneous main memory architectures (e.g., [56,61,62,64,195,214,216,218,219,232,258,311,315,318,358,392, 393). Efficiently exploiting the significantly larger main memory capacities and the increasing heterogeneity in the main memory architectures requires careful memory management that is conventionally performed using virtual memory. However, conventional virtual memory frameworks are designed without considering modern applications' overwhelmingly high memory demand, and thus, without considering the new larger more complex main memory designs. Therefore, continuing to adopt the conventional approach to virtual memory with the increasing capacity and heterogeneity in today's main memory architectures requires a lot of effort and often leads to important challenges and inefficiencies. Furthermore, in addition to the growth in the size of data that modern applications process, prior works [201, 225, 226, 249, 375, 377] show that different pieces of program data have different performance characteristics (latency/bandwidth/parallelism sensitivity), and other inherent properties (e.g., compressibility, persistence, approximability). As highlighted by recent works [201, 249, 375, 377], conveying semantic information about application's data to the hardware that manages the physical memory resources can enable vastly more intelligent dataaware management of the underlying hardware resources (e.g., better address translation, data mapping, migration, and scheduling decisions) and a host of new optimization opportunities.

Unfortunately, conventional virtual memory frameworks [37,38,74,78,79,98,182,183,366] as the key interface between the software stack and the hardware are not capable of conveying any insights regarding the properties and memory behaviour of different pieces of program data. Instead, programs are traditionally conveyed to the hardware in the form of ISA instructions and a set of memory accesses to virtual addresses. This semantic gap leads to hardware treating all data as the same, thereby being unable to exploit data's semantics properties to employ more intelligent management or optimization policies. Accordingly, the management and optimization policies used in existing systems are data-oblivious and mainly component-aware [271], i.e., designed according to the characteristics of the system component as apposed to the properties of the data that it handles (e.g., tuning tile size to fit a specific cache size). By ignoring the valuable memory characteristics and semantic properties of application's data, each component of the system is required to predict the application's data behaviour in order to optimize its policies. Such a strategy is quite challenging and often not very effective due to three main problems. First, each component in the system has a *limited* and *localized* view of the data and is not aware of the overall behaviour of the application. Therefore, its decisions may not be ideal when considering the big picture. Second, each component requires separate resources for inferring and predicting the behaviour of the data. This leads to repeated overhead in every component that can be avoided using a unified and expressive interface that connects different layers of the computing stack. Third, the optimizations made by different components mainly react to the behaviour of the data as the overall application's behaviour is not available or predictable. This makes it challenging to make timely optimization/management decisions.

Data-oblivious policies in modern systems are a direct result of how poor today's systems are at exploiting the valuable properties of different pieces of application's data, which results in ineffective policies and lost performance optimization opportunities that can be achieved by exploiting data properties to improve the computing systems policies. We posit that conventional virtual memory frameworks, as a critical component of the existing computing systems cannot efficiently support the high data demand and diversity in modern applications, as well as the diversity in today's system configurations that have evolved in response to the modern application's memory needs.

### 1.2 Our Approach: Data-Centric and Data-Aware Architectures for Fundamentally Efficient Data Handling

In this thesis, we argue that, moving forward, computing systems need to consider large amounts of data and the efficient computation of data as the ultimate priority of the system. In particular, modern computing systems should follow two main directions. (1) data-centric architectures, and (2) data-aware architectures.

Data-Centric Architectures. In contrast to the dominant processor-centric design paradigm, we believe that, in order to efficiently handle large amounts of data, modern computing systems need to be *data-centric*, meaning that they should (1) minimize data movement, and (2) compute data in or near where the data resides. The data-centric approach to computing is highly effective as (1) it improves performance by reducing/eliminating the need to move data to the processor for computation, and (2) provides the ability to take advantage of the large internal bandwidth in the main memory to increase the efficiency of the computation. For example, we show that a processing-using-DRAM architecture that efficiently implements and computes complex operations in DRAM, and provides the ability to support new arbitrary operations can significantly improve the overall performance and efficiency of the system (Chapter 2).

Data-Aware Architectures. In contrast to the dominant data-oblivious policies in existing systems, we believe that modern computing systems should enable data-aware policies, by allowing the software to easily communicate properties and semantic information about each application's and system's data to the hardware. A data-aware architecture (1) understands what it can do with and to each piece of data, and (2) makes use of different properties of data (e.g., compressibility, approximability, locality, sparsity, access semantics) to improve performance, efficiency and other metrics. For example, we show that a more scalable data-aware virtual memory framework that (1) is fundamentally designed to handle large amounts of data more efficiently, and (2) understands, conveys and exploits the properties of program's data to enable more intelligent memory management and optimizations, can significantly improve performance for both native execution and virtual machine environments, and significantly improve the effectiveness of heterogeneous main memory architectures (Chapter 3).

#### 1.2.1 Thesis Statement

This thesis, hence, provides evidence for the following thesis statement:

The performance and energy efficiency of computing systems can improve significantly when handling the increasingly large amounts of data in modern applications by employing data-centric and data-aware architectures that can (1) remove the overheads associated with data movement by processing data where it resides, (2) efficiently adapting to the diversity in today's system configurations and memory architectures that are designed to process large amounts of data, and (3) understand, convey, and exploit the characteristics of the data to make more intelligent memory management decisions.

#### 1.3 Overview of Research

In this thesis, we propose a novel data-centric processing-using-memory framework and a novel data-aware virtual memory framework, which we briefly describe next. We also put

these contributions in the context of relevant prior work in Sections 1.3.1 and 1.3.2. We provide detailed discussions of and comparisons to prior work in Chapters 2 and 3.

# 1.3.1 SIMDRAM: A Data-Centric Framework for Bit-Serial SIMD Processing using DRAM (Chapter 2)

In order to provide processing capability in or near where data resides, many prior works have explored DRAM designs (as well as other memory technologies) that are capable of performing computation using memory [4,11,19–22,66,71,77,82,85,94,103,108,141,157,172,188,197,227–229,286,292,333,335,336,338,340–343,345,347,359,360,364,380,389]. However, these works suffer from three major shortcoming. First, they support only basic operations and fall short on efficiently supporting more complex operations, which limits their applicability [11,18–22,77,108,141,157,229,337,338,389]. Second, they support only a limited and specific set of operations, lacking the flexibility to support new operations and cater to the wide variety of applications that can potentially benefit from processing-using-DRAM [77,228]. Third, they often require significant changes to the DRAM subarray, which makes them costly [77,228]. These shortcomings highlight the need for a framework that aids the general adoption of processing-using-DRAM by efficiently implementing complex operations and providing the flexibility to support new desired operations, while requiring minimal changes to the DRAM architecture.

To this end, this thesis introduces SIMDRAM, a flexible general-purpose processingusing-DRAM framework that (1) enables the efficient implementation of complex operations, (2) provides a flexible mechanism to support the implementation of arbitrary user-defined operations, and (3) uses an in-DRAM massively-parallel SIMD substrate that requires minimal changes to the DRAM architecture. We build the in-DRAM substrate used in the SIMDRAM framework around two key techniques. The first key technique is vertical data layout in DRAM. Prior works show that employing a vertical layout for the data in DRAM [11, 35, 85, 103, 108, 144, 145, 170, 350, 373] eliminates the need for adding extra logic in DRAM to implement the bit-shift operation [77, 228] which is essential for many complex operations. Employing vertical data layout provides SIMDRAM with two key benefits: (1) implicit shift operation, and (2) massive parallelism, wherein each DRAM column operates as a SIMD lane by placing the source and destination operands of an operation on top of each other in the same DRAM column. The second key technique used in SIMDRAM substrate is majority-based computation. As opposed to using basic logic operations such as AND/OR/NOT as building blocks to implement in-DRAM computation [108, 228, 335, 338], SIMDRAM uses logically complete set of majority (MAJ) and NOT operations to implement in-DRAM computation. Majority-based computation enables SIMDRAM to achieve higher performance, higher throughput, and lower energy consumption compared to using basic logical operations as building blocks for in-DRAM computation.

The SIMDRAM framework we introduce is composed of three main steps. The first step of the framework builds an efficient MAJ/NOT representation of a desired operation from

its AND/OR/NOT-based implementation. The second step allocates DRAM rows to the operation's inputs and outputs and generates the required sequence of DRAM commands to execute the desired operation, which is called  $\mu Program$ . The third step executes the  $\mu Program$  to perform the operation. SIMDRAM uses a control unit in the memory controller that transparently issues the sequence of commands to DRAM, as dictated by the  $\mu Program$ .

We provide a detailed reference implementation of SIMDRAM in this thesis, including required hardware, programming, and ISA support, to (1) address key system integration challenges, and (2) allow programmers to define new operations without hardware changes. We demonstrate the generality of the SIMDRAM framework using 16 complex in-DRAM operations, and seven commonly-used real-world applications. We show that SIMDRAM is a promising processing-using-memory framework that (1) can ease the adoption of processing-using-DRAM architectures, and (2) improve the performance and efficiency of processing-using-DRAM architectures.

The SIMDRAM framework is introduced, discussed and evaluated in detail in Chapter 2 of this thesis (as well as Appendixes A, B, C, and D). An earlier version of SIMDRAM was presented at the ASPLOS 2021 conference [131].

# 1.3.2 The Virtual Block Interface: A Flexible Data-Aware Alternative to the Conventional Virtual Memory Framework (Chapter 3)

Considering the key role that virtual memory has in the overall performance of the modern computing systems, a wide body of research (e.g., [1-3, 10, 17, 27, 28, 30, 32-34, 38, 42-204-207, 230, 231, 234, 250-254, 257, 259, 297, 304-306, 308, 309, 312, 313, 321-323, 329, 339, 344, 320-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-320, 330-3200, 330-3200, 330-3200, 330-3200, 330-3200, 330349, 351, 356, 367–369, 378, 383–386, 391, 401) propose mechanisms to alleviate the various overheads associated with it (in some cases when handling the large data demand in modern applications). However, despite notable improvements, these solutions suffer from three major shortcomings. First, they are mainly designed based on specific system or workload characteristics and, thus, are applicable to only a limited set of problems or applications. Second, each solution requires specialized and not necessarily compatible changes to either the operating system or hardware or both. Therefore, implementing a combination of these proposals at the same time in a system is a daunting prospect. Third, these proposals do not support understanding, conveying, and exploiting the properties of program data in order to enable more intelligent memory management decisions (i.e., data-aware architectures). These shortcomings highlight the need for a holistic solution to efficiently support modern applications in today's diverse system configurations, by (1) eliminating the inefficiencies of the conventional virtual memory framework when handling modern applications' large amount of data, (2) exploiting the properties of different pieces of program data to improve performance, efficiency and other metrics.

To this end, in this thesis, we introduce the Virtual Block Interface (VBI), a generalpurpose alternative virtual memory framework that has three major properties. First, VBI is able to understand, convey, and exploit the properties of different pieces of program data to enable more intelligent management of main memory. Second, VBI efficiently and flexibly supports increasingly diverse system configurations that are employed today to process the high data demand in modern applications. Third, VBI provides the key features of the conventional virtual memory framework while eliminating its key inefficiencies when handling large amounts of data in modern applications. The key idea in VBI is to delegate the physical memory allocation and address translation to dedicated hardware in the memory controller.

The VBI design is driven by three key guiding principles. First, programs should be allowed to choose the size of their virtual address space. This mitigates the translation overheads associated with unnecessarily large and fixed-sized virtual address spaces in current systems that results in increasingly large inefficiencies with the diverse memory requirements of modern applications. Second, address translation should be decoupled from memory protection, as they are logically separate. This enables opportunities to remove address translation from the critical path of an access protection check, and defer the address translation until physical memory must be accessed, thereby lowering the performance overheads of virtual memory when handling large amounts of data in modern applications. It also enables the flexibility of managing address translation and access protection using separate structures customized to their characteristics, which again helps with more efficient address translation mechanisms which reduce the overhead of processing large data volumes in modern applications. Third, software should be allowed to communicate semantic information about application data to the hardware. This helps hardware to exploit the rich properties of different pieces of data to manage the underlying memory resources more intelligently.

VBI naturally enables a variety of important optimizations that improve overall system performance when handling the high memory demand in modern applications, including: (1) enabling benefits akin to using virtually-indexed virtually-tagged (VIVT) caches (e.g., reduced address translation overhead), (2) eliminating two-dimensional page table walks in virtual machine environments, (3) delaying physical memory allocation until the first dirty last-level cache line eviction, and (4) flexibly supporting different virtual-to-physical address translation structures for different memory regions.

We demonstrate the benefits of VBI with two example use cases. First, we experimentally show that VBI significantly improves performance for both native execution and virtual machine environments. Second, we show that VBI significantly improves the effectiveness of heterogeneous main memory architectures. We demonstrate that VBI is a promising new virtual memory framework, that can enable several important optimizations, and increase the design flexibility for virtual memory to support efficient handling of data in modern computing systems.

The VBI virtual memory framework is introduced, discussed, and evaluated in detail in Chapter 3 of this thesis. An earlier version of VBI was presented at the ISCA 2020 conference [132].

#### 1.4 Contributions

To our knowledge, this thesis is the first to propose and study new frameworks for fundamentally-efficient data handling in modern computing systems with a focus on two key directions at the same time, i.e., data-centric and data-aware architectures. In this thesis, we make two major contributions.

- We present SIMDRAM, an end-to-end processing-using-DRAM framework that aids the widespread adoption of processing-using-DRAM, a data-centric computation paradigm that improves the overall performance and efficiency of the system when computing on large amounts of data by minimizing the cost of data movement and enabling computation where the data resides. To this end, SIMDRAM (1) efficiently computes complex operations required by modern data intensive applications, (2) provides the ability to implement new arbitrary operations as required, and (3) uses an in-DRAM massively-parallel SIMD substrate that requires minimal changes to the DRAM architecture. We provide a detailed reference implementation of SIMDRAM, including required changes to applications, ISA, and hardware. We demonstrate the effectiveness and generality of the SIMDRAM framework at improving the system performance and efficiency using a wide range of complex operations and commonly-used real-world applications.

- We introduce VBI, a novel data-aware scalable general-purpose virtual memory framework that enables efficient handling of large amounts of data in modern applications by (1) efficiently understanding, conveying, and exploiting the properties of different pieces of program data to enable more intelligent management of main memory, (2) efficiently and flexibly supporting increasingly diverse system configurations and memory architectures that are employed today to process the high data demand in modern applications, and (3) providing the key features of the conventional virtual memory framework while eliminating its key inefficiencies when handling large amounts of data in modern applications. We provide a detailed reference implementation of VBI, including required changes to applications, system software, ISA, and hardware. We demonstrate the effectiveness of VBI at significantly improving the overall system performance in native and virtualized environments. We also show that VBI significantly improves the effectiveness of heterogeneous main memory architectures.

Other contributions of this thesis are listed in Chapters 2 and 3. We specifically direct the reader to the final subsections in each chapter for a concise summary and contributions of each chapter, i.e., Sections 2.8 and 3.8 in this thesis.

## Chapter 2

## **SIMDRAM**

As discussed in Chapter 1, the increasing prevalence and growing size of data in modern applications has led to high energy and latency costs for computation in traditional computer architectures. Moving large amounts of data between memory (e.g., DRAM) and the CPU across bandwidth-limited memory channels can consume more than 60% of the total energy in modern systems [51,272]. To mitigate such costs, the *processing-in-memory* (PIM) paradigm moves computation closer to where the data resides, reducing (and in some cases eliminating) the need to move data between memory and the processor.

There are two main approaches to PIM [112, 273]: (1) processing-near-memory, where PIM logic is added to the same die as memory or to the logic layer of 3D-stacked memory [7–9,14,15,26,29,31,39,40,50–55,73,80,83,92,109,110,113,116,118,124,127,136,137,147,148,150–152,166,184,185,189,190,215,221,239–241,243,278,279,287–289,302,314,327,331,353–355,365,397,399,402,403]; and (2) processing-using-memory, which makes use of the operational principles of the memory cells themselves to perform computation by enabling interactions between cells [4,11,19-22,39,40,66,71,77,82,85,94,103,108,141,157,172,188,197,227-229,286,333,335,336,338,340-343,345,347,359,360,364,380,389]. Since processing-using-memory operates directly in the memory arrays, it benefits from the large internal bandwidth and parallelism available inside the memory arrays, which processing-near-memory solutions cannot take advantage of.

A common approach for processing-using-memory architectures is to make use of bulk bitwise computation. Many widely-used data-intensive applications (e.g., databases, neural networks, graph analytics) heavily rely on a broad set of simple (e.g., AND, OR, XOR) and complex (e.g., equality check, multiplication, addition) bitwise operations. Ambit [335,338], an in-DRAM processing-using-memory accelerator, was the first work to propose exploiting DRAM's analog operational principles to perform bulk bitwise AND, OR, and NOT logic operations. Inspired by Ambit, many prior works have explored DRAM (as well as NVM) designs that are capable of performing in-memory bitwise operations [11, 18–22, 77, 108, 141, 157, 229, 333, 335–338, 340–343, 389]. However, a major shortcoming prevents these proposals from becoming widely applicable: they support only basic operations (e.g., Boolean

operations, addition) and fall short on flexibly and easily supporting new and more complex operations. Some prior works propose processing-using-DRAM designs that support more complex operations [77, 228]. However, such designs (1) require significant changes to the DRAM subarray, and (2) support only a limited and specific set of operations, lacking the flexibility to support new operations and cater to the wide variety of applications that can potentially benefit from in-memory computation.

Our goal in this work is to design a framework that aids the adoption of processing-using-DRAM by efficiently implementing complex operations and providing the flexibility to support new desired operations. To this end, we propose SIMDRAM, an end-to-end processing-using-DRAM framework that provides the programming interface, the ISA, and the hardware support for (1) efficiently computing *complex* operations, and (2) providing the ability to implement *arbitrary* operations as required, all in an in-DRAM massively-parallel SIMD substrate. At its core, we build the SIMDRAM framework around a DRAM substrate that enables two previously-proposed techniques: (1) vertical data layout in DRAM, and (2) majority-based logic for computation.

Vertical Data Layout. Supporting bit-shift operations is essential for implementing complex computations, such as addition or multiplication. Prior works show that employing a vertical layout [11,35,85,103,108,144,145,170,350,373] for the data in DRAM, such that all bits of an operand are placed in a single DRAM column (i.e., in a single bitline), eliminates the need for adding extra logic in DRAM to implement shifting [77,228]. Accordingly, SIMDRAM supports efficient bit-shift operations by storing operands in a vertical fashion in DRAM. This provides SIMDRAM with two key benefits. First, a bit-shift operation can be performed by simply copying a DRAM row into another row (using RowClone [336], LISA [66], NoM [345] or FIGARO [380]). For example, SIMDRAM can perform a left-shift-by-one operation by copying the data in DRAM row j to DRAM row j+1. (Note that while SIMDRAM supports bit shifting, we can optimize many applications to avoid the need for explicit shift operations, by simply changing the row indices of the SIMDRAM commands that read the shifted data). Second, SIMDRAM enables massive parallelism, wherein each DRAM column operates as a SIMD lane by placing the source and destination operands of an operation on top of each other in the same DRAM column.

Majority-Based Computation. Prior works use majority operations to implement basic logical operations [108,228,335,338] (e.g., AND, OR) or addition [11,19,77,104,108,228]. These basic operations are then used as basic building blocks to implement the target in-DRAM computation. SIMDRAM extends the use of the majority operation by directly using only the logically complete set of majority (MAJ) and NOT operations to implement in-DRAM computation. Doing so enables SIMDRAM to achieve higher performance, throughput, and reduced energy consumption compared to using basic logical operations as building blocks for in-DRAM computation. We find that a computation typically requires fewer

DRAM commands using MAJ and NOT than using basic logical operations AND, OR, and NOT.

To aid the adoption of processing-using-DRAM by flexibly supporting new and more complex operations, SIMDRAM addresses two key challenges: (1) how to synthesize new arbitrary in-DRAM operations, and (2) how to exploit an optimized implementation and control flow for such newly-added operations while taking into account key limitations of in-DRAM processing (e.g., DRAM operations that destroy input data, limited number of DRAM rows that are capable of processing-using-DRAM, and the need to avoid costly in-DRAM copies). As a result, SIMDRAM is the first end-to-end framework for processing-using-DRAM. SIMDRAM provides (1) an effective algorithm to generate an efficient MAJ/NOT-based implementation of a given desired operation; (2) an algorithm to appropriately allocate DRAM rows to the operands of the operation and an algorithm to map the computation to an efficient sequence of DRAM commands to execute any MAJ-based computation; and (3) the programming interface, ISA support and hardware components required to (i) compute any new user-defined in-DRAM operation without hardware modifications, and (ii) program the memory controller for issuing DRAM commands to the corresponding DRAM rows and correctly performing the computation. Such end-to-end support enables SIMDRAM as a holistic approach that facilitates the adoption of processing-using-DRAM through (1) enabling the flexibility to support new in-DRAM operations by providing the user with a simplified interface to add desired operations, and (2) eliminating the need for adding extra logic to DRAM.

The SIMDRAM framework efficiently supports a wide range of operations of different types. In this work, we demonstrate the functionality of the SIMDRAM framework using an example set of 16 operations including (1) N-input logic operations (e.g., AND/OR/XOR of more than 2 input bits); (2) relational operations (e.g., equality/inequality check, greater than, maximum, minimum); (3) arithmetic operations (e.g., addition, subtraction, multiplication, division); (4) predication (e.g., if-then-else); and (5) other complex operations such as bitcount and ReLU [120]. The SIMDRAM framework is not limited to these 16 operations, and can enable processing-using-DRAM for other existing and future operations. SIMDRAM is well-suited to application classes that (i) are SIMD-friendly, (ii) have a regular access pattern, and (iii) are memory bound. Such applications are common in domains such as database analytics, high-performance computing, image processing, and machine learning.

We compare the benefits of SIMDRAM to different state-of-the-art computing platforms (CPU, GPU, and the Ambit [338] in-DRAM computing mechanism). We comprehensively evaluate SIMDRAM's reliability, area overhead, throughput, and energy efficiency. We leverage the SIMDRAM framework to accelerate seven application kernels from machine learning, databases, and image processing (VGG-13 [352], VGG-16 [352], LeNET [209], kNN [222], TPC-H [372], BitWeaving [233], brightness [119]). Using a single DRAM bank, SIMDRAM provides (1)  $2.0\times$  the throughput and  $2.6\times$  the energy efficiency of Ambit [338],

averaged across the 16 implemented operations; and (2) 2.5× the performance of Ambit, averaged across the seven application kernels. Compared to a CPU and a high-end GPU, SIMDRAM using 16 DRAM banks provides (1) 257× and 31× the energy efficiency, and 88× and 5.8× the throughput of the CPU and GPU, respectively, averaged across the 16 operations; and (2) 21× and 2.1× the performance of the CPU and GPU, respectively, averaged across the seven application kernels. SIMDRAM incurs no additional area overhead on top of Ambit, and a total area overhead of only 0.2% in a high-end CPU. We also evaluate the reliability of SIMDRAM under different degrees of manufacturing process variation, and observe that it guarantees correct operation as the DRAM process technology node scales down to smaller sizes.

#### 2.1 Background

We first briefly explain the architecture of a typical DRAM chip. Next, we describe prior processing-using-DRAM works that SIMDRAM builds on top of (RowClone [336] and Ambit [335, 338, 342]) and explain the implications of majority-based computation. For an even more detailed operation of DRAM, we refer the reader to many prior works [61,63–66, 138–140, 168, 178–181, 186, 188, 191, 193, 195–197, 214–216, 216–219, 237, 238, 299–301, 333, 336, 338, 339, 341, 381].

#### 2.1.1 DRAM Basics

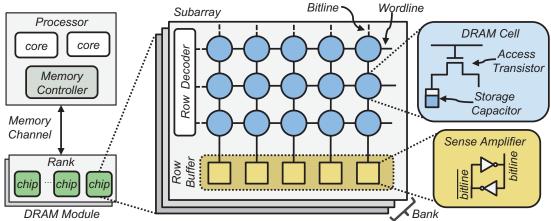

A DRAM system comprises a hierarchy of components, as Figure 2.1 shows, starting with channels at the highest level. A channel is subdivided into ranks, and a rank is subdivided into multiple banks (e.g., 8-16). Each bank is composed of multiple (e.g., 64-128) 2D arrays of cells known as subarrays. Cells within a subarray are organized into multiple rows (e.g., 512-1024) and multiple columns (e.g., 2-8 kB) [186, 216, 217]. A cell consists of an access transistor and a storage capacitor that encodes a single bit of data using its voltage level. The source nodes of the access transistors of all the cells in the same column connect the cells' storage capacitors to the same bitline. Similarly, the gate nodes of the access transistors of all the cells in the same wordline.

Figure 2.1: High-level overview of DRAM organization.

When a wordline is asserted, all cells along the wordline are connected to their corresponding bitlines, which perturbs the voltage of each bitline depending on the value stored in each cell's capacitor. A two-terminal sense amplifier connected to each bitline senses the voltage difference between the bitline (connected to one terminal) and a reference voltage (typically  $\frac{1}{2}V_{DD}$ ; connected to the other terminal) and amplifies it to a CMOS-readable value. In doing so, the sense amplifier terminal connected to the reference voltage is amplified to the opposite (i.e., negated) value, which is shown as the bitline terminal in Figure 2.1. The set of sense amplifiers in each subarray forms a logical row buffer, which maintains the sensed data for as long as the row is open (i.e., the wordline continues to be asserted). A read or write operation in DRAM includes three steps:

- 1. ACTIVATE. The *wordline* of the target row is asserted, which connects all cells along the row to their respective bitlines. Each bitline shares charge with its corresponding cell capacitor, and the resulting bitline voltage shift is sensed and amplified by the bitline's sense amplifier. Once the sense amplifiers finish amplification, the row buffer contains the values originally stored within the cells along the asserted wordline.

- 2. RD/WR. The memory controller then issues read or write commands to columns within the activated row (i.e., the data within the row buffer).

- 3. PRECHARGE. The capacitor is disconnected from the bitline by disabling the wordline, and the bitline voltage is restored to its quiescent state (e.g., typically  $\frac{1}{2}V_{DD}$ ).

#### 2.1.2 Processing-using-DRAM

#### In-DRAM Row Copy.

RowClone [336] is a mechanism that exploits the vast internal DRAM bandwidth to efficiently copy rows inside DRAM without CPU intervention. RowClone enables copying a source row A to a destination row B in the same subarray by issuing two consecutive ACTIVATE commands to these two rows, followed by a PRECHARGE command. This command sequence is called AAP [338]. The first ACTIVATE command copies the contents of the source row A into the row buffer. The second ACTIVATE command connects the cells in the destination row B to the bitlines. Because the sense amplifiers have already sensed and amplified the source data by the time row B is activated, the data (i.e., voltage level) in each cell of row B is overwritten by the data stored in the row buffer (i.e., row A's data). Recent work [108] experimentally demonstrates the feasibility of executing in-DRAM row copy operations in unmodified off-the-shelf DRAM chips.

#### In-DRAM Bitwise Operations.

Ambit [335, 338, 342] shows that simultaneously activating three DRAM rows (via a DRAM operation called Triple Row Activation, TRA) can be used to perform bitwise Boolean AND, OR, and NOT operations on the values contained within the cells of the three rows. When activating three rows, three cells connected to each bitline share charge simultaneously and contribute to the perturbation of the bitline. Upon sensing the perturbation, the sense amplifier amplifies the bitline voltage to  $V_{DD}$  or 0 if at least two of the capacitors of the

three DRAM cells are charged or discharged, respectively. As such, a TRA results in a Boolean majority operation (MAJ) among the three DRAM cells on each bitline. A majority operation MAJ outputs a 1 (0) only if more than half of its inputs are 1 (0). In terms of AND  $(\cdot)$  and OR (+) operations, a 3-input majority operation can be expressed as MAJ(A, B, C) = A · B + A · C + B · C.

Ambit implements MAJ by introducing a custom row decoder (discussed in Section 2.2.1) that can perform a TRA by simultaneously addressing three wordlines. To use this decoder, Ambit defines a new command sequence called AP, which issues (1) a TRA to compute the MAJ of three rows, followed by (2) a PRECHARGE to close all three rows. Ambit uses AP command sequences to implement Boolean AND and OR operations by simply setting one of the inputs (e.g., C) to 1 or 0. The AND operation is computed by setting C to 0 (i.e., MAJ(A, B, 0) = A AND B). The OR operation is computed by setting C to 1 (i.e., MAJ(A, B, 1) = A OR B).

To achieve functional completeness alongside AND and OR operations, Ambit implements NOT operations by exploiting the differential design of DRAM sense amplifiers. As Section 2.1.1 explains, the sense amplifier already generates the complement of the sensed value as part of the activation process ( $\overline{\text{bitline}}$  in Figure 2.1). Therefore, Ambit simply forwards  $\overline{\text{bitline}}$  to a special DRAM row in the subarray that consists of DRAM cells with two access transistors, called dual-contact cells (DCCs). Each access transistor is connected to one side of the sense amplifier and is controlled by a separate wordline (d-wordline or n-wordline). By activating either the d-wordline or the n-wordline, the row of DCCs can provide the true or negated value stored in the row's cells, respectively.

#### Majority-Based Computation.

Activating multiple rows simultaneously reduces the reliability of the value read by the sense amplifiers due to manufacturing process variation, which introduces non-uniformities in circuit-level electrical characteristics (e.g., variation in cell capacitance levels) [338]. This effect worsens with (1) an increased number of simultaneously activated rows, and (2) more advanced technology nodes with smaller sizes. Accordingly, although processing-using-DRAM can potentially support majority operations with more than three inputs (as proposed by prior works [11, 19, 229]) our realization of processing-using-DRAM uses the minimum number of inputs required for a majority operation (N=3) to maintain the reliability of the computation. In Section 2.6.5, we demonstrate via SPICE simulations that using 3-input MAJ operations provides higher reliability compared to designs with more than three inputs per MAJ operation. Using 3-input MAJ, a processing-using-DRAM substrate does not require modifications to the subarray organization (Figure 2.2) beyond the ones proposed

<sup>&</sup>lt;sup>1</sup>Although the 'A' in AP refers to a TRA operation instead of a conventional ACTIVATE command, we use this terminology to remain consistent with the Ambit paper [338], since an ACTIVATE command can be internally translated to a TRA operation by the DRAM chip [338].

by Ambit (Section 2.2.1). Recent work [108] experimentally demonstrates the feasibility of executing MAJ operations by activating three rows in unmodified off-the-shelf DRAM chips.

#### 2.2 SIMDRAM Overview

SIMDRAM is a processing-using-DRAM framework whose goal is to (1) enable the efficient implementation of complex operations and (2) provide a flexible mechanism to support the implementation of arbitrary user-defined operations. We present the subarray organization in SIMDRAM, describe an overview of the SIMDRAM framework, and explain how to integrate SIMDRAM into a system.

#### 2.2.1 Subarray Organization

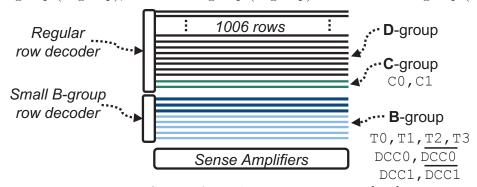

In order to perform processing-using-DRAM, SIMDRAM makes use of a subarray organization that incorporates additional functionality to perform logic primitives (i.e., MAJ and NOT). This subarray organization is *identical* to Ambit's [338] and is similar to DRISA's [228]. Figure 2.2 illustrates the internal organization of a subarray in SIMDRAM, which resembles a conventional DRAM subarray. SIMDRAM requires only minimal modifications to the DRAM subarray (namely, a small row decoder that can activate three rows simultaneously) to enable computation. Like Ambit [338], SIMDRAM divides DRAM rows into *three groups*: the **D**ata group (D-group), the **C**ontrol group (C-group) and the **B**itwise group (B-group).

Figure 2.2: SIMDRAM subarray organization [338].

The D-group contains regular rows that store program or system data. The C-group consists of two constant rows, called C0 and C1, that contain all-0 and all-1 values, respectively. These rows are used (1) as initial input values for a given SIMDRAM operation (e.g., the initial carry-in bit in a full addition), or (2) to perform operations that naturally require AND/OR operations (e.g., AND/OR reductions). The D-group and the C-group are connected to the regular row decoder, which selects a single row at a time.

The B-group contains six regular rows, called T0, T1, T2, and T3; and two rows of dual-contact cells (see Section 2.1.2), whose d-wordlines are called DCC0 and DCC1, and whose n-wordlines are called  $\overline{\rm DCC0}$  and  $\overline{\rm DCC1}$ , respectively. The B-group rows, called compute rows, are designated to perform bitwise operations. They are all connected to a special row decoder that can simultaneously activate three rows using a single address (i.e., perform a TRA)

(a) SIMDRAM Framework: Steps 1 and 2

(b) SIMDRAM Framework: Step 3

Figure 2.3: Overview of the SIMDRAM framework.

Using a typical subarray size of 1024 rows [65, 186, 188, 195, 218], SIMDRAM splits the row addressing into 1006 D-group rows, 2 C-group rows, and 16 B-group rows.

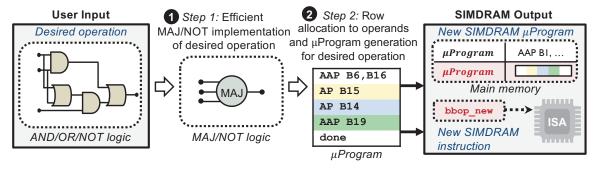

#### 2.2.2 Framework Overview

SIMDRAM is an end-to-end framework that provides the user with the ability to implement an *arbitrary* operation in DRAM using the AAP/AP command sequences. The framework comprises three key steps, which are illustrated in Figure 2.3. The first two steps of the framework give the user the ability to efficiently implement any desired operation in DRAM, while the third step controls the execution flow of the in-DRAM computation transparently from the user. We briefly describe these steps below, and discuss each step in detail in Section 2.3.

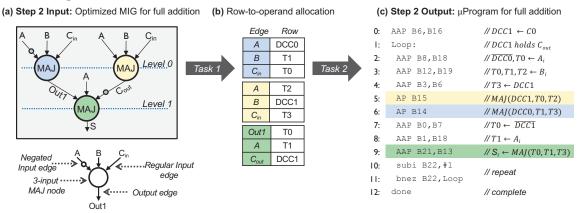

The first step (**1** in Figure 2.3a; Section 2.3.1) builds an efficient MAJ/NOT representation of a given desired operation from its AND/OR/NOT-based implementation. Specifically, this step takes as input a desired operation and uses logic optimization to minimize the number of logic primitives (and, therefore, the computation latency) required to perform the operation. Accordingly, for a desired operation input into the SIMDRAM framework by the user, the first step derives its *optimized* MAJ/NOT-based implementation.

The second step (② in Figure 2.3a; Section 2.3.2) allocates DRAM rows to the operation's inputs and outputs and generates the required sequence of DRAM commands to execute the desired operation. Specifically, this step translates the MAJ/NOT-based implementation of the operation into AAPs/APs. This step involves (1) allocating the designated compute rows in DRAM to the operands, and (2) determining the optimized sequence of AAPs/APs that

are required to perform the operation. While doing so, SIMDRAM minimizes the number of AAPs/APs required for a specific operation. This step's output is a  $\mu$ Program, i.e., the optimized sequence of AAPs/APs that is stored in main memory and will be used to execute the operation at runtime.

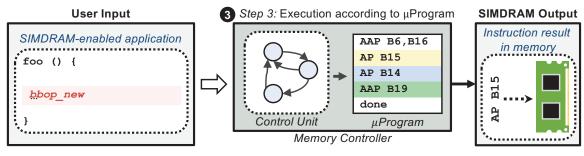

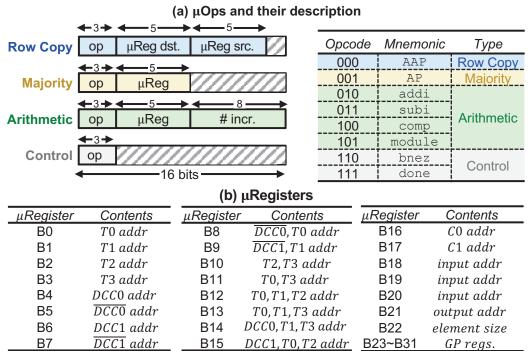

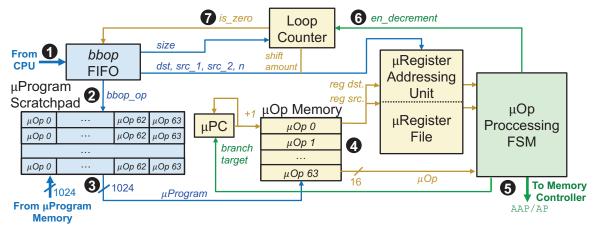

The third step (**3** in Figure 2.3b; Section 2.3.3) executes the μProgram to perform the operation. Specifically, when a user program encounters a *bbop* instruction (Section 2.4.2) associated with a SIMDRAM operation, the *bbop* instruction triggers the execution of the SIMDRAM operation by performing its μProgram in the memory controller. SIMDRAM uses a *control unit* in the memory controller that transparently issues the sequence of AAPs/APs to DRAM, as dictated by the μProgram. Once the μProgram is complete, the result of the operation is held in DRAM.

#### 2.2.3 Integrating SIMDRAM in a System

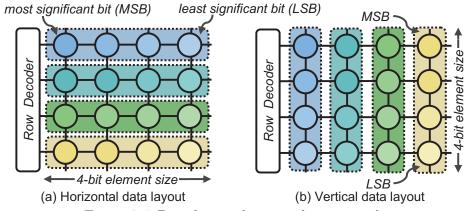

As we discuss earlier, SIMDRAM operates on data using a vertical layout. Figure 2.4 illustrates how data is organized within a DRAM subarray when employing a horizontal data layout (Figure 2.4a) and a vertical data layout (Figure 2.4b). We assume that each data element is four bits wide, and that there are four data elements (each one represented by a different color). In a conventional horizontal data layout, data elements are stored in different DRAM rows, with the contents of each data element ordered from the most significant bit to the least significant bit (or vice versa) in a single row. In contrast, in a vertical data layout, the DRAM row holds only the *i*-th bit of multiple data elements (where the number of elements is determined by the bit width of the row). Therefore, when activating a single DRAM row in a vertical data layout organization, a single bit of data from each data element is read at once, which enables in-DRAM bit-serial parallel computation [11,35,124,228,342,350].

Figure 2.4: Data layout: horizontal vs. vertical.

To maintain compatibility with traditional system software, we store regular data in the conventional horizontal layout and provide hardware support (explained in Section 2.4.1) to transpose horizontally-laid-out data into the vertical layout for in-DRAM computation. To

simplify program integration, we provide ISA extensions that expose SIMDRAM operations to the programmer (Section 2.4.2).

#### 2.3 SIMDRAM Framework

We describe the three steps of the SIMDRAM framework introduced in Section 2.2.2, using the full addition operation as a running example.

#### 2.3.1 Step 1: Efficient MAJ/NOT Implementation

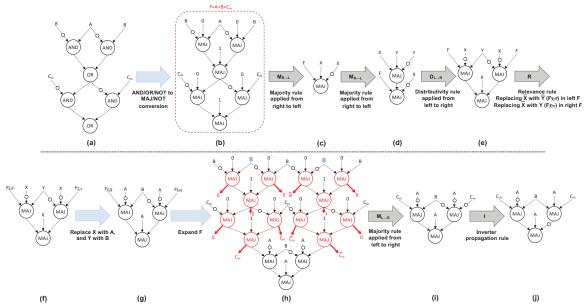

SIMDRAM implements in-DRAM computation using the logically-complete set of MAJ and NOT logic primitives, which requires fewer AAP/AP command sequences to perform a given operation when compared to using AND/OR/NOT. As a result, the goal of the first step in the SIMDRAM framework is to build an optimized MAJ/NOT implementation of a given operation that executes the operation using as few AAP/AP command sequences as possible, thus minimizing the operation's latency. To this end, Step 1 transforms an AND/OR/NOT representation of a given operation to an optimized MAJ/NOT representation using a transformation process formalized by prior work [16].

The transformation process uses a graph-based representation of the logic primitives, called an  $AND-OR-Inverter\ Graph\ (AOIG)$  for AND/OR/NOT logic, and a  $Majority-Inverter\ Graph\ (MIG)$  for MAJ/NOT logic. An AOIG is a logic representation structure in the form of a directed acyclic graph where each node represents an AND or OR logic primitive. Each edge in an AOIG represents an input/output dependency between nodes. The incoming edges to a node represent input operands of the node and the outgoing edge of a node represents the output of the node. The edges in an AOIG can be either regular or complemented (which represents an inverted input operand; denoted by a bubble on the edge). The direction of the edges follows the natural direction of computation from inputs to outputs. Similarly, a MIG is a directed acyclic graph in which each node represents a three-input MAJ logic primitive, and each regular/complemented edge represents one input or output to the MAJ primitive that the node represents. The transformation process consists of two parts that operate on an input AOIG.