School of Engineering Science • Burnaby, BC • V5A 1S6 ensc440-IJtech@sfu.ca

March 9, 2006

Dr. Andrew Rawicz School of Engineering Science Simon Fraser University Burnaby, British Columbia V5A 1S6

Re: ENSC 440 Design Specifications for a Smart Alarm Clock

Dear Dr. Rawicz,

The enclosed document, Design Specifications for a Smart Alarm Clock, details the design specifications of our product currently in development for the ENSC 440 course.

In an active attempt to remedy the sociological problem of sleep deprivation plaguing over 50 million Americans, we are constructing an alarm clock with a pulse measurement module that awakes individuals at the designated sleeping stage to feel more energetic and less prone to the effects of sleep inertia. An MP3 module allows users to rise to their favourite tunes, while a Bluetooth light control plug simulates the gradually intensifying light of a sunrise.

The accompanying document outlines the design features and testing procedures that the Smart Alarm Clock is to fulfill upon completion. The main components of our device include an Alarm Clock subsystem, an MP3 subsystem, a Pulse Measurement subsystem, and a Light Control subsystem. A detailed approach to the design specification provides an unambiguous design standard for which all team members follow.

Inglewood Jack Technologies Inc. consists of five talented and innovative individuals who study engineering at Simon Fraser University: Albert Su, Christian Le, Herman Leung, William Ng, and Matthew Ng. If you have any questions or concerns, we will be pleased to answer them. We can be contacted via email at ensc440-IJtech@sfu.ca.

Sincerely,

hutche

Christian Le Chief Operations Officer Inglewood Jack Technologies, Inc.

Enclosure: Design Specifications for a Smart Alarm Clock

# Inglewood Jack Technologies, Inc

# Design Specifications for a Smart Alarm

|  | 1 |

|--|---|

|  | Ζ |

|  |   |

|  |   |

| Project Team:   | Christian Le                 |

|-----------------|------------------------------|

| -               | Herman Leung                 |

|                 | Matthew Ng                   |

|                 | William Ng                   |

|                 | Albert Su                    |

| Contact Person: | Christian Le                 |

|                 | ensc440-IJtech@sfu.ca        |

| Submitted to:   | Dr. Andrew Rawicz – ENSC 440 |

|                 | Steve Whitmore – ENSC 305    |

School of Engineering Science Simon Fraser University Issued Date: March 9, 2006 Revision: 1.0

# **EXECUTIVE SUMMARY**

With the advent of electrical lighting, shift work, social diversion and global competition, modern lifestyle has evolved to sacrifice an average of two hours of sleep a night for more time and productivity in society. Sleep deprivation results in increased vulnerability to accidents, reduced work performance and decreased concentration, yet people in industrialized nations refuse to tradeoff their busy lifestyle for more sleep. As a practical solution to the widespread and serious health problem, the Smart Alarm Clock applies the theories of circadian rhythm and strives to allow its users to wake up feeling more refreshed, sustaining better moods and performing tasks with improved efficiency and accuracy.

Central to the Smart Alarm Clock is a pulse measurement device that monitors user sleep rhythm. Sleeping cycle data are relayed and processed to awake the user at the Rapid Eye Movement stage in the closest proximity to the preset wake time. To promote a pleasant waking experience, an MP3 subsystem and a light control module replaces agonizing alarm sounds with music and light.

To demonstrate the concept of the Smart Alarm Clock, a proof-of-concept model will first be designed and constructed. In the first phase of development, the proof-of-concept model will support full functionalities including the following features:

- i. Active sleep cycle monitoring to activate gradually intensifying music and light at the proper sleep stage and time to reduce grogginess.

- ii. MP3 storage and playback capabilities for the user to awake to music.

- iii. A functional light control unit that enables user to rise to their favorite light or the operation of other electronic devices.

- iv. Easy to use alarm clock and menu system.

- v. Preliminary compliance to safety and environment standards.

Upon the completion of the proof-of-concept model in April, we will pursue to the development of a production version which adds:

- 1. Attractive packaging and casing for the alarm clock and light control unit.

- 2. Additional MP3 capabilities for the user to awake to customized music.

- 3. Full compliance to safety, environmental and energy efficiency standards.

# **Table of Contents**

| EXECU'         | TIVE SUMMARY                          | ii   |

|----------------|---------------------------------------|------|

| Table of       | Contents                              | iii  |

| List of F      | igures                                | vi   |

| List of T      | ables                                 | vii  |

| Glossary       | <sup>7</sup>                          | viii |

| 1. Intr        | oduction                              | 1    |

| 1.1.           | Theoretical Background                |      |

| 1.2.           | Scope                                 |      |

| 1.3.           | Intended Audience                     |      |

|                |                                       |      |

| 2. Syst        | tem Overview                          |      |

|                |                                       |      |

| 2.1.           | Alarm Clock Subsystem                 |      |

| 2.2.           | Music Player Subsystem                |      |

| 2.3.           | Pulse Measurement Subsystem           |      |

| 2.4.           | Light Control Subsystem               |      |

| 3. Syst        | tem Hardware Design                   | 6    |

| 3.1.           | Alarm Clock Subsystem Design          | 6    |

| 3.1.1          | , .                                   |      |

| 3.1.2          |                                       |      |

| 3.1.3          |                                       | 7    |

| 3.1.4          | . ICM7211 LCD Driver                  |      |

| 3.1.5          | . EmbeddedBlue eb505 Bluetooth Module |      |

| 3.1.6          | · · · · · · · · · · · · · · · · · · · |      |

| 3.1.7          |                                       |      |

| 3.1.8          |                                       |      |

| 3.1.9          |                                       |      |

| 3.1.1          |                                       |      |

| 3.1.1<br>3.1.1 |                                       |      |

| 3.1.1          |                                       |      |

| 3.1.1          |                                       |      |

| 3.1.1          |                                       |      |

| 3.2.           | Music Player Subsystem Design         |      |

| 3.2.1          |                                       |      |

| 3.2.1          |                                       |      |

|                |                                       |      |

| 3.2.3          | . <i>MMC</i>                          |      |

| 3.2.3<br>3.2.4 |                                       |      |

Copyright  $\ensuremath{\mathbb{C}}$  2006, Inglewood Jack Technologies, Inc.

|                          | 3.2.6                                                                                                                                                                        | J                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                          | 3.2.7                                                                                                                                                                        | MP3 Decoding                                                                                                                                                                                                                                                                                                                             | . 19                                                                                         |

|                          | 3.2.8                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|                          | 3.2.9                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|                          | 3.3.                                                                                                                                                                         | Light Control Subsystem Design                                                                                                                                                                                                                                                                                                           | . 22                                                                                         |

|                          | 3.3.1                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | . 22                                                                                         |

|                          | 3.3.2                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|                          | 3.3.3                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|                          | 3.3.4                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|                          | 3.4.                                                                                                                                                                         | Pulse Measurement Subsystem Design                                                                                                                                                                                                                                                                                                       |                                                                                              |

|                          | 3.4.1                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|                          | 3.4.2                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

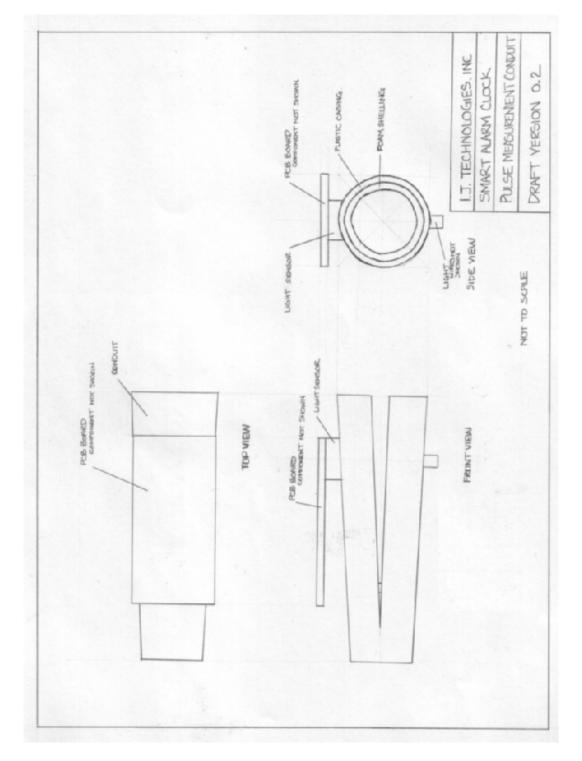

|                          | 3.4.3                                                                                                                                                                        | Device Conduit Design                                                                                                                                                                                                                                                                                                                    | . 26                                                                                         |

| 4.                       | Firn                                                                                                                                                                         | nware Design                                                                                                                                                                                                                                                                                                                             | . 28                                                                                         |

|                          | 4.1.                                                                                                                                                                         | Microcontroller                                                                                                                                                                                                                                                                                                                          | . 28                                                                                         |

|                          | 4.1.1                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|                          | 4.1.2                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|                          | 4.1.3                                                                                                                                                                        | Bluetooth Module                                                                                                                                                                                                                                                                                                                         | . 30                                                                                         |

|                          | 4.2.                                                                                                                                                                         | MP3 Audio Codec                                                                                                                                                                                                                                                                                                                          | . 31                                                                                         |

|                          | 4.3.                                                                                                                                                                         | MMC                                                                                                                                                                                                                                                                                                                                      | 32                                                                                           |

|                          | 4.4.                                                                                                                                                                         | Audio Amplifier                                                                                                                                                                                                                                                                                                                          |                                                                                              |

|                          | 4.5.                                                                                                                                                                         | I/O Expander                                                                                                                                                                                                                                                                                                                             |                                                                                              |

|                          | 4.3.                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                          | . 54                                                                                         |

|                          |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

| 5.                       | Con                                                                                                                                                                          | munication Protocols                                                                                                                                                                                                                                                                                                                     | . 36                                                                                         |

| 5.                       | <b>Con</b> 5.1.                                                                                                                                                              | Wireless Communication Requirements                                                                                                                                                                                                                                                                                                      |                                                                                              |

| 5.                       |                                                                                                                                                                              | Wireless Communication Requirements                                                                                                                                                                                                                                                                                                      | . 36                                                                                         |

| 5.                       | 5.1.<br>5.2.                                                                                                                                                                 | Wireless Communication Requirements<br>Bluetooth Implementation                                                                                                                                                                                                                                                                          | . 36<br>. 36                                                                                 |

| 5.                       | 5.1.<br>5.2.<br>5.3.                                                                                                                                                         | Wireless Communication Requirements<br>Bluetooth Implementation<br>EmbeddedBlue Command Set                                                                                                                                                                                                                                              | . 36<br>. 36<br>. 38                                                                         |

| 5.                       | 5.1.<br>5.2.                                                                                                                                                                 | Wireless Communication Requirements<br>Bluetooth Implementation<br>EmbeddedBlue Command Set<br>Search Local Device                                                                                                                                                                                                                       | . 36<br>. 36<br>. 38<br>. <i>39</i>                                                          |

| 5.                       | 5.1.<br>5.2.<br>5.3.<br><i>5.3.1</i>                                                                                                                                         | Wireless Communication Requirements<br>Bluetooth Implementation<br>EmbeddedBlue Command Set<br>Search Local Device<br>Check Device Mode                                                                                                                                                                                                  | . 36<br>. 36<br>. 38<br>. 39<br>. 39                                                         |

| 5.                       | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.                                                                                                                                     | Wireless Communication Requirements<br>Bluetooth Implementation<br>EmbeddedBlue Command Set<br>Search Local Device<br>Check Device Mode<br>Establish Bluetooth Connection.                                                                                                                                                               | . 36<br>. 36<br>. 38<br>. 39<br>. 39<br>. 39                                                 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.                                                                                                                   | Wireless Communication Requirements<br>Bluetooth Implementation<br>EmbeddedBlue Command Set<br>Search Local Device<br>Check Device Mode<br>Establish Bluetooth Connection<br>Bluetooth Communication Protocol                                                                                                                            | . 36<br>. 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39                                         |

| <b>5</b> .<br><b>6</b> . | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b>                                                                                                    | Wireless Communication Requirements<br>Bluetooth Implementation<br>EmbeddedBlue Command Set<br>Search Local Device<br>Check Device Mode<br>Establish Bluetooth Connection<br>Bluetooth Communication Protocol                                                                                                                            | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                                         |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.                                                                                            | Wireless Communication Requirements<br>Bluetooth Implementation<br>EmbeddedBlue Command Set<br>Search Local Device<br>Check Device Mode<br>Establish Bluetooth Connection<br>Bluetooth Communication Protocol<br>ware Design<br>Modular Description of Hardware Components                                                               | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                                 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.1.                                                                                  | <ul> <li>Wireless Communication Requirements</li></ul>                                                                                                                                                                                                                                                                                   | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 42<br>. 42<br>. 42 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.1.<br>6.1.2.                                                                        | <ul> <li>Wireless Communication Requirements</li></ul>                                                                                                                                                                                                                                                                                   | . 36<br>. 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39         |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.1.<br>6.1.2.<br>6.1.3.                                                              | Wireless Communication Requirements. Bluetooth Implementation EmbeddedBlue Command Set Search Local Device Check Device Mode Establish Bluetooth Connection. Bluetooth Communication Protocol Ware Design Modular Description of Hardware Components LCD Module                                                                          | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.                                                    | Wireless Communication Requirements.   Bluetooth Implementation   EmbeddedBlue Command Set   Search Local Device   Check Device Mode   Establish Bluetooth Connection   Bluetooth Communication Protocol   ware Design   Modular Description of Hardware Components   LCD Module   Real Time Clock (RTC) Module   FC Module   SPI Module | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.                                                    | Wireless Communication Requirements                                                                                                                                                                                                                                                                                                      | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>6.1.6.                                          | Wireless Communication Requirements                                                                                                                                                                                                                                                                                                      | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>6.1.6.<br>6.1.7.                                | <ul> <li>Wireless Communication Requirements</li></ul>                                                                                                                                                                                                                                                                                   | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>6.1.6.<br>6.1.7.<br>6.1.8.                      | <ul> <li>Wireless Communication Requirements</li></ul>                                                                                                                                                                                                                                                                                   | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>6.1.6.<br>6.1.7.<br>6.1.8.<br>6.1.9.            | <ul> <li>Wireless Communication Requirements</li></ul>                                                                                                                                                                                                                                                                                   | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>6.1.6.<br>6.1.7.<br>6.1.8.<br>6.1.9.<br>6.1.10. | <ul> <li>Wireless Communication Requirements</li></ul>                                                                                                                                                                                                                                                                                   | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                 |

|                          | 5.1.<br>5.2.<br>5.3.<br>5.3.1.<br>5.3.2.<br>5.3.3.<br>5.4.<br><b>Soft</b><br>6.1.<br>6.1.2.<br>6.1.3.<br>6.1.4.<br>6.1.5.<br>6.1.6.<br>6.1.7.<br>6.1.8.<br>6.1.9.            | <ul> <li>Wireless Communication Requirements</li></ul>                                                                                                                                                                                                                                                                                   | . 36<br>. 38<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39<br>. 39                 |

Copyright  $\ensuremath{\mathbb{C}}$  2006, Inglewood Jack Technologies, Inc.

|                   | 6.2.2.                        | Initialization State                                                |     |

|-------------------|-------------------------------|---------------------------------------------------------------------|-----|

|                   | 6.2.3.                        | Idle State                                                          |     |

|                   | 6.2.4.                        | Alarm Set State                                                     |     |

|                   | 6.2.5.                        | Monitoring State                                                    |     |

|                   | 6.2.6.                        | Alarming State                                                      |     |

| 6.                | 3. A                          | lgorithms                                                           |     |

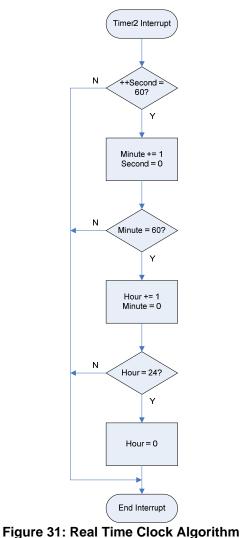

|                   | 6.3.1.                        | Real Time Clock Generation                                          |     |

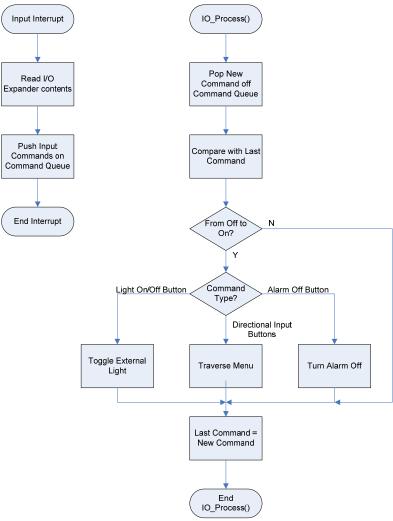

|                   | 6.3.2.                        | Input Handling                                                      |     |

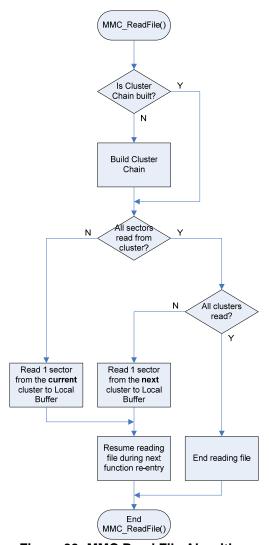

|                   | 6.3.3.                        | Reading MP3 Files from MMC                                          |     |

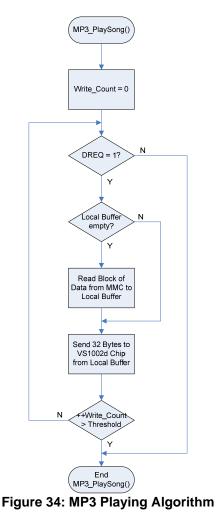

|                   | 6.3.4.                        | Playing MP3 Files                                                   |     |

|                   | 6.3.5.                        | Increasing Volume Level                                             |     |

|                   | 6.3.6.                        | Acquiring Pulse Samples                                             |     |

|                   | 6.3.7.                        | Determining Pulse Rate                                              |     |

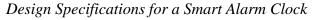

|                   | 6.3.8.                        | Determining Appropriate Waking Stage                                |     |

| 7.                | User I                        | nterface Design                                                     | 57  |

|                   |                               |                                                                     |     |

| 7.                | 1. Ir                         | nitialization                                                       |     |

| 7.2               | 2. R                          | oot Menu                                                            |     |

| 7.                | 3. A                          | larm Menu                                                           |     |

| 7.4               |                               | lock Menu                                                           |     |

| ,.                |                               |                                                                     |     |

| 8.                | Test P                        | lan                                                                 |     |

| 8.                | 1. H                          | ardware Test Plan                                                   |     |

|                   | 8.1.1.                        | General System Testing                                              |     |

|                   | 8.1.2.                        | Alarm Clock Subsystem Verification                                  |     |

|                   | 8.1.3.                        | Music Player Subsystem Verification                                 |     |

|                   | 8.1.4.                        | Light Control Subsystem Verification                                |     |

|                   | 8.1.5.                        | Pulse Meter Subsystem Verification                                  |     |

| 8.2               | 2. S                          | oftware Test Plan                                                   |     |

| 8.                |                               | roof of Concept Experiments                                         |     |

|                   |                               | 1 1                                                                 |     |

| 9.                | Conclu                        | usion                                                               |     |

| 10.               | Refere                        | ences                                                               |     |

|                   |                               |                                                                     |     |

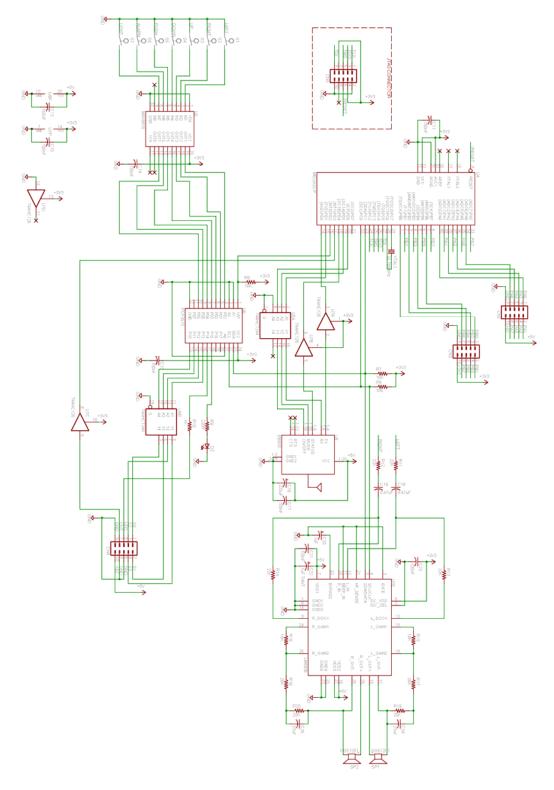

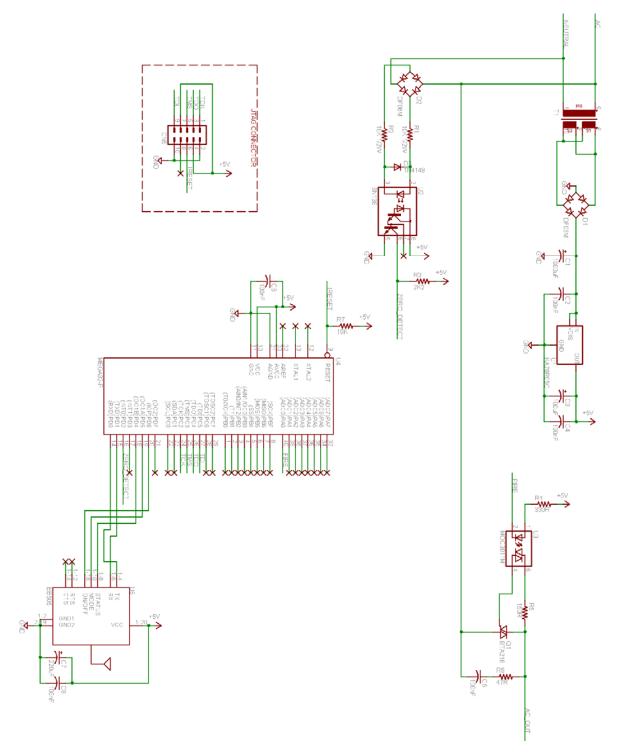

| App               | endix A                       | A – Alarm Clock Module Schematic                                    |     |

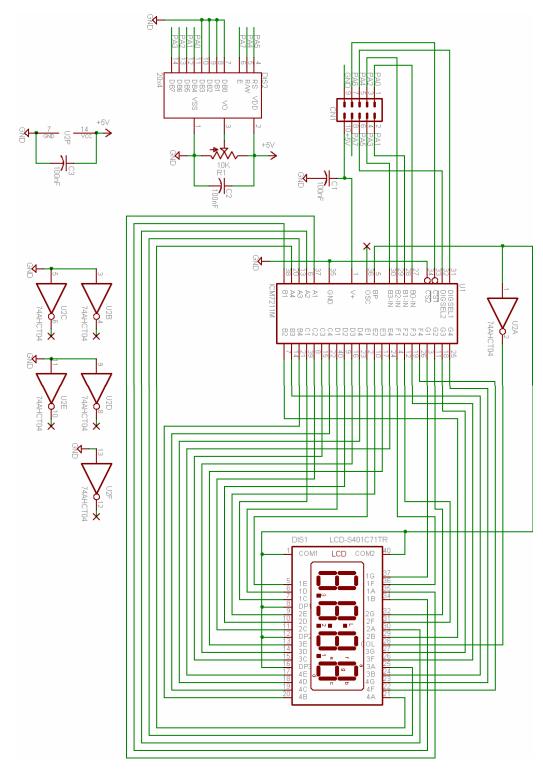

|                   |                               | B – LCD Schematic                                                   |     |

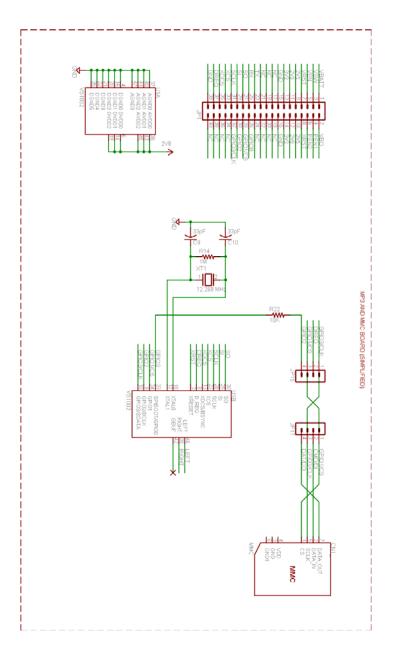

|                   |                               | C – MP3 Module Schematic                                            |     |

| Ann               | endiv I                       |                                                                     | / 1 |

|                   |                               |                                                                     |     |

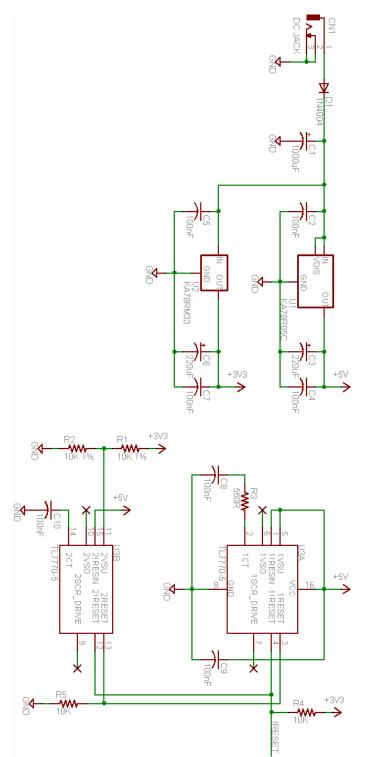

| App               | endix l                       | D – Light Dimmer Module Schematic                                   |     |

| App<br>App        | endix l<br>endix l            | D – Light Dimmer Module Schematic<br>E – Power Regulation Schematic |     |

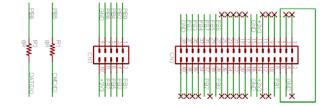

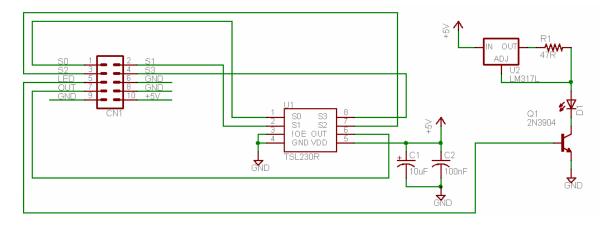

| App<br>App<br>App | endix l<br>endix l<br>endix l | D – Light Dimmer Module Schematic                                   |     |

# List of Figures

| Figure 1: Sleep Cycle throughout a Typical Night of Sleep [10]               | 1  |

|------------------------------------------------------------------------------|----|

| Figure 2: Smart Alarm Clock Modules & Interconnections                       |    |

| Figure 3: Functional Block Diagram of the Alarm Clock Subsystem              |    |

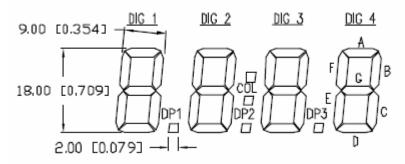

| Figure 4: Digit Size on Numeric LCD                                          |    |

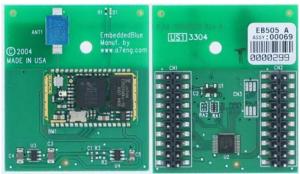

| Figure 5: EmbeddedBlue eb505 Module; front view (Left) and back view (Right) | 9  |

| Figure 6: 4-Direction Input Button                                           |    |

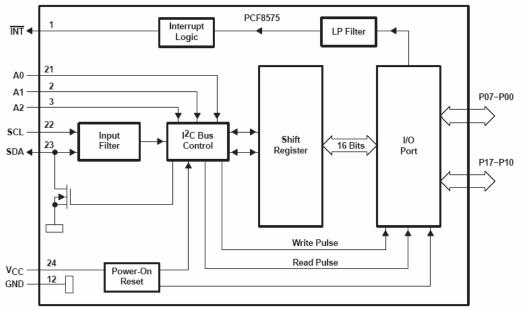

| Figure 7: I/O Expander Block Diagram                                         | 12 |

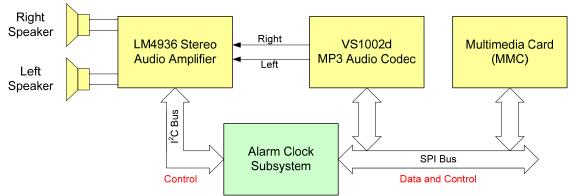

| Figure 8: Functional Block Diagram of the Music Player Subsystem             | 14 |

| Figure 9: VS10xx Prototyping Board                                           |    |

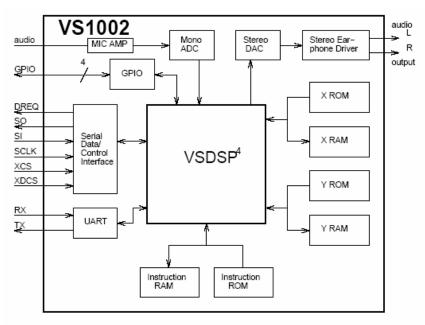

| Figure 10: VS1002d MP3 Audio Codec                                           | 16 |

| Figure 11: Kingston 128MB MMC                                                | 16 |

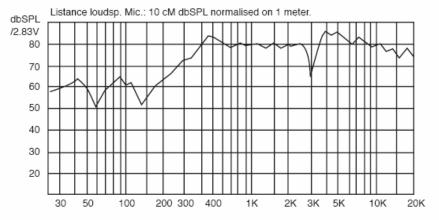

| Figure 12: Sound Pressure Level (dbSPL) versus Frequency Response [6]        | 17 |

| Figure 13: MMC Pin Assignments                                               | 18 |

| Figure 14: VS1002d Functional Block Diagram                                  | 19 |

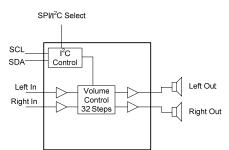

| Figure 15: LM4936 Functional Block Diagram                                   | 20 |

| Figure 16: Functional Block Diagram of the Light Control Subsystem           | 22 |

| Figure 17: Functional Block Diagram of the Pulse Measurement Subsystem       | 24 |

| Figure 18: Pulse Measurement Subsystem in Use                                | 27 |

| Figure 19: List of Alphanumeric LCD Instructions and Execution Time [8]      | 29 |

| Figure 20: List of Characters Supported by the Alphanumeric LCD [8]          |    |

| Figure 21: List of Numeric Characters Available on Seven-Segment Display     | 30 |

| Figure 22: MMC Command Format                                                |    |

| Figure 23: Most Commonly Used MMC Commands                                   | 33 |

| Figure 24: MMC Transfer Flow                                                 | 33 |

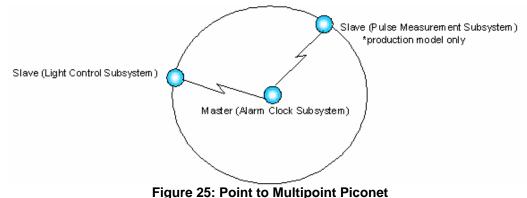

| Figure 25: Point to Multipoint Piconet                                       |    |

| Figure 26: OSI Reference and Bluetooth Stack Models                          |    |

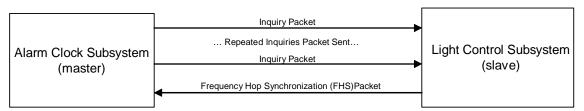

| Figure 27: Device Discovery Procedures                                       |    |

| Figure 28: Baseband Paging Procedures                                        |    |

| Figure 29: Command Structure                                                 |    |

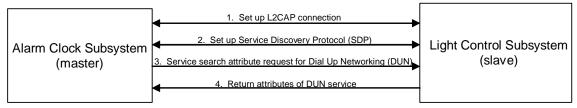

| Figure 30: State Transition Diagram for the Smart Alarm Clock                |    |

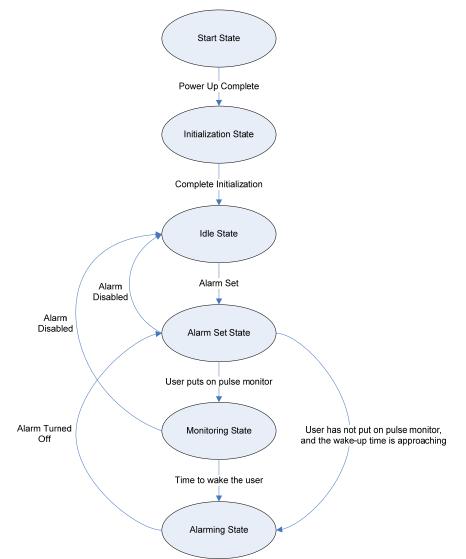

| Figure 31: Real Time Clock Algorithm                                         |    |

| Figure 32: Input Handling Algorithm                                          |    |

| Figure 33: MMC Read File Algorithm                                           |    |

| Figure 34: MP3 Playing Algorithm                                             |    |

| Figures 35 & 36: Root Menu Screens (Alarm Disabled & Alarm Enabled)          |    |

| Figures 37 & 38: Alarm Menu Screenshots                                      |    |

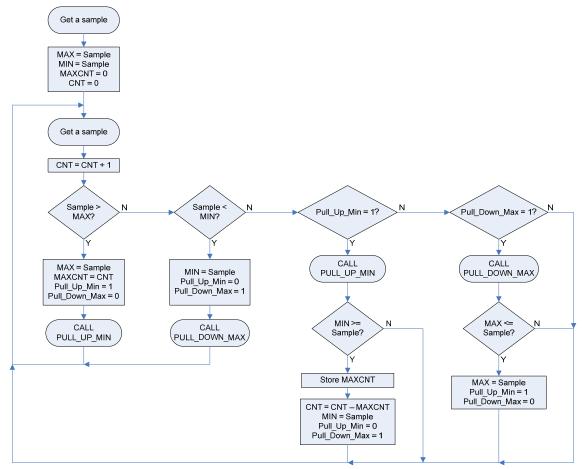

| Figure 39: Set Alarm Time Screen                                             |    |

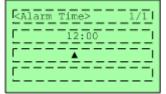

| Figures 40 & 41: Set Window Period Screenshots                               |    |

| Figures 42 & 43: Set Alarm Volume Screenshots                                |    |

| Figures 44 & 45: Clock Menu Screen (12-Hour Enabled & 12-Hour Disabled)      | 60 |

# List of Tables

| Table 1: Alphanumeric LCD Pin Assignment                        | . 10 |

|-----------------------------------------------------------------|------|

| Table 2: Numeric LCD Pin Assignment                             | . 11 |

| Table 3: Bluetooth Pin Assignment                               | . 11 |

| Table 4: I/O Expander Pin Assignment                            | . 12 |

| Table 5: MMC Pin Assignment                                     | . 18 |

| Table 6: VS1002d Pin Assignment                                 | . 19 |

| Table 7: LM4936 Pin Assignment                                  |      |

| Table 8: Summary of Jumpers Removed on VS10xx Prototyping Board |      |

| Table 9: VS10xx Prototype Board Connection to Microcontroller   | . 21 |

| Table 10: Terminal Functions of TSL230R                         |      |

| Table 11: Bluetooth Module Common Commands and Syntax           |      |

| Table 12: Registers of Interest on MP3 Audio Codec              |      |

| Table 13: Register Contents of Interest for MODE                |      |

| Table 14: Register Contents on the Audio Amplifier              |      |

| Table 15: Bit Contents on the Audio Amplifier                   |      |

| Table 16: I/O Expander Interface Definition                     |      |

| Table 17: Operation Byte                                        |      |

| Table 18: Reply Byte                                            |      |

| Table 19: Start State Transition                                |      |

| Table 20: Initialization State Transition                       |      |

| Table 21: Idle State Transition                                 |      |

| Table 22: Alarm Set State Transition                            |      |

| Table 23: Monitoring State Transition                           |      |

| Table 24: Alarming State Transition                             |      |

| Table 25: SAC Menus.                                            |      |

| Table 26: Root Menu Functions                                   |      |

| Table 27: Alarm Menu Functions                                  |      |

| Table 28: Clock Menu Functions                                  | . 60 |

|                                                                 |      |

# Glossary

| AC               | Alternating Current                                     |

|------------------|---------------------------------------------------------|

| ACS              | Alarm Clock Subsystem                                   |

| DAC              | Digital to Analog Converter                             |

| dB               | Decibel                                                 |

| EEPROM           | Electrically Erasable Programmable Read Only Memory     |

| FIFO             | First In First Out                                      |

| GPIO             | General Purpose Input/Output                            |

| I <sup>2</sup> C | Inter-Integrated Circuit                                |

| ISM              | Industrial, Scientific and Medical                      |

| LCD              | Liquid Crystal Display                                  |

| LCS              | Light Control Subsystem                                 |

| LD               | Light Detector                                          |

| LE               | Light Emitter                                           |

| LED              | Light Emitting Diode                                    |

| MMC              | MultiMedia Card                                         |

| MPEG             | Moving Picture Experts Group                            |

| MP3              | Moving Picture Experts Group Layer 3                    |

| MPS              | Music Player Subsystem                                  |

| NREM             | Non Rapid Eye Movement                                  |

| OSI              | Open Systems Interconnect                               |

| PMS              | Pulse Measurement Subsystem                             |

| REM              | Rapid Eye Movement                                      |

| RMS              | Root Mean Square                                        |

| SAC              | Smart Alarm Clock                                       |

| SCI              | Serial Control Interface                                |

| SD               | Secure Digital                                          |

| SDI              | Serial Data Interface                                   |

| SNR              | Signal to Noise Ratio                                   |

| SPI              | Serial Peripheral Interface                             |

| SRAM             | Static Random Access Memory                             |

| SWS              | Slow-Wave Sleep                                         |

| UART             | Universal Asynchronous Receiver/Transmitter             |

| USART            | Universal Synchronous/Asynchronous Receiver/Transmitter |

# 1. Introduction

The Smart Alarm Clock (SAC) is a device that will help users wake up in the morning with greater ease and feeling more refreshed. This goal is achieved by using a combination of gradually intensifying light and sound as stimuli initiated based on the user's sleep stage. Users can wake up to their favourite music by simply loading MP3 files into the device. The users can also use their existing bedside lamp for the light feature by simply plugging the electrical plug into a subcomponent of the Smart Alarm Clock. Sleep stage is monitored by examining the user's pulse rate for transitional cues. The project will be developed in two phases. Phase one consists of developing a prototype as a "proof of concept" model scheduled for completion in April of 2006. Phase two consists of improving upon the features' effectiveness and usability in preparation for commercial sales.

#### 1.1. Theoretical Background

Sleep stage is divided into two distinct groups: Rapid Eye Movement (REM) sleep and Slow-Wave sleep (SWS). SWS is further broken down into four stages from 1 to 4. REM sleep stage is characterized by the high amount of brainwave activity associated with it, which is very similar to brainwave patterns of an individual who is awake. Stages 1 and 2 of SWS also show similar brainwave patterns as waking. However, Stages 3 and 4 show a much slower brainwave activity. SWS is often collectively lumped together under the term Non-REM (NREM) sleep [15].

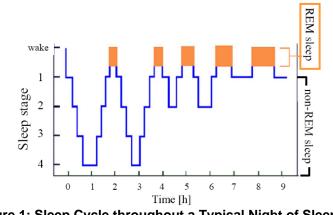

A typical night of sleep consists of a periodical rhythm of REM and NREM sleep stages. Each periodic cycle lasts anywhere between 90 to 110 minutes, depending on the time during the night. During the early part of the night, there is more Stage 3 and Stage 4 sleep. As the night progresses, the amount of Stage 3 and Stage 4 sleep reduces, resulting in an alternating pattern between Stage 2 sleep and REM sleep. Figure 1 shows the typical sleep cycle experienced throughout the night.

Figure 1: Sleep Cycle throughout a Typical Night of Sleep [12]

Sleep inertia is a physiological state characterised by a decline in motor dexterity and a subjective feeling of grogginess, immediately following an abrupt awakening from deep sleep. The effects of sleep inertia typically last from one minute to several hours. Studies have been conducted to verify the differential effect of sleep inertia based on the sleep stage at which wakening occurs. One such study involved several university students being subjected to two conditions of consecutive nights of REM and NREM sleep stage (Stage 2 in this case) wakening. Assessments on performance were done immediately after awakening and then every three hours thereafter. The results have shown that waking up from Stage 3 or 4 produces the most sleep inertia, whereas Stage 2, REM, and Stage 1 produces reducing amounts of sleep inertia, in that order [4]. Thus, it is ideal to wake the individual during, or shortly after the completion of REM stage.

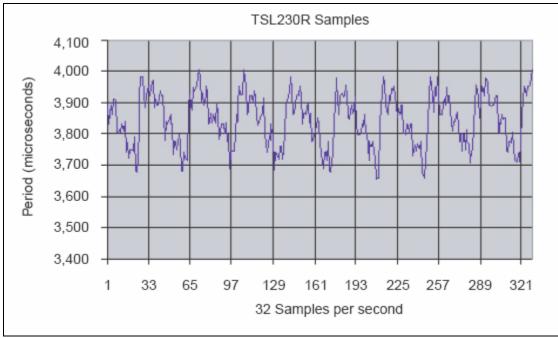

The autonomic activities associated with the REM and NREM sleep can be used to differentiate the two. REM sleep is characterized by variable heart rate with high bursts whereas SWS shows slow decline in heart rate [15]. Additional studies have shown that significant heart rate variation metrics are observed in different stages of sleep. These metrics compare the variability of the beat-to-beat period of the measured heart beat. SWS and REM shows the greatest observable contrast [5]. By using a pulse rate or heart rate monitor, it is possible to track the variable heart rate pattern associated with REM, and identify when transitions between SWS and REM occur through a threshold level detection of the heart rate variability [12].

Additional considerations must be made when attempting to wake a user up during REM sleep. The importance of REM sleep is still under debate, but a widely held belief is that REM sleep consolidates memories and aids in learning [9]. Thus, it is also ideal to maximize REM sleep whenever possible, by waking up users near the end of the REM sleep stage.

The exposure of light in the morning stimulates the Suprachiasmatic Nucleus (SCN), a group of cells in the hypothalamus that respond to light and dark signals. The SCN controls the circadian biological clock. The SCN responds to light by delaying the release of hormones associated with sleep onset, and releases hormones that raise the body temperature [14]. Thus the use of light will reduce the user's urge to fall back to sleep, and facilitate in the waking process.

#### 1.2. Scope

This document standardizes the design specifications that must be met by the proof of concept model of the Smart Alarm Clock to fulfill the functional requirements as discussed in the *Functional Specifications for a Smart Alarm Clock*. Additional specifications toward the production model will not be stated in this document. An extensive list of tests to be conducted in the development process of the proof of concept model provides the test plan framework for our module and integration engineers.

#### 1.3. Intended Audience

The primary audiences of this document are product developers, integration engineers and quality assurance personnel. The design specification acts as an implementation guideline in order to fulfill all functional requirements for the proof of concept model.

Chief engineers and executives can make use of this document to plan, direct, motivate and control development progress. In carrying out product tests, the design specification provides a comprehensive test plan for test engineers.

### 2. System Overview

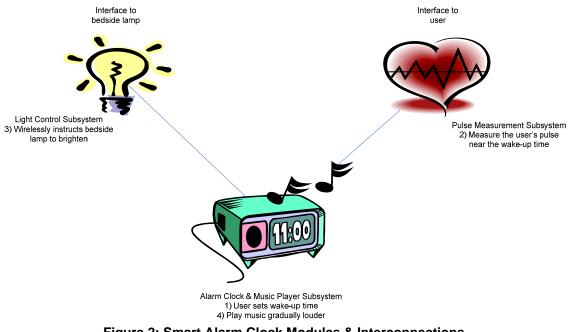

The Smart Alarm Clock is composed of four subsystems working together to provide the overall system functionality. The figure below shows an overview of the various subsystems and their interconnections.

Figure 2: Smart Alarm Clock Modules & Interconnections

#### 2.1. Alarm Clock Subsystem

As the central component, the Alarm Clock subsystem keeps track of the current time and the time when the user needs to wake up. A user interface allows easy setting of the wake-up time, selection of the music to wake up to, and various other user configurations.

This subsystem is responsible for communicating with the other subsystems during the waking process. It takes the user's pulse rate from the Pulse Measurement subsystem and processes the raw data to determine the appropriate time to initiate the light and sound features. Communication with the Light Control subsystem is performed wirelessly to instruct the gradual brightening of an external light source. Similarly, communication with the Music Player subsystem instructs it to play the specified song while gradually increasing the sound volume.

#### 2.2. Music Player Subsystem

This subsystem incorporates MP3 processing and non-volatile storage, allowing the users to load their own songs. Speakers and audio amplifiers are also incorporated to provide support for stereo sound. Digital volume adjustment features are available for automatically increasing the sound volume of the current song being played, as controlled by the Alarm Clock subsystem.

Though there are two subsystems for the alarm clock and music player, these subsystems will be in the same physical unit as shown in Figure 1.

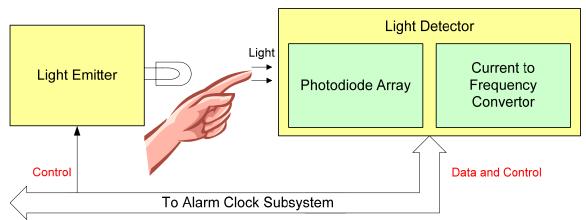

#### 2.3. Pulse Measurement Subsystem

This subsystem is responsible for measuring the user's pulse rate in a non-invasive manner. The measured data is then passed to the Alarm Clock subsystem where processing is done to determine any changes in the pulse rate.

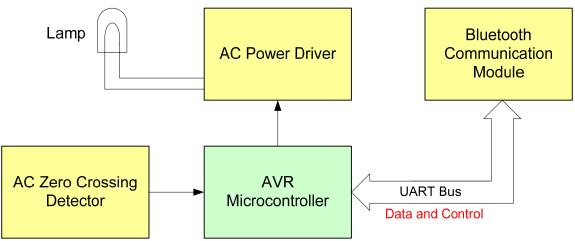

#### 2.4. Light Control Subsystem

This subsystem interfaces to the user's current bedside lamp, which acts as the external light source. It controls the light intensity by varying the amount of AC power that gets passed to the external light source. It communicates with the Alarm Clock subsystem wirelessly.

# 3. System Hardware Design

The hardware design approach of the SAC is divided into four sections, one for each functional subsystem.

#### 3.1. Alarm Clock Subsystem Design

The Alarm Clock Subsystem (ACS) is the central component of the SAC. It is responsible for keeping track of the current time as well as the wake up time. It provides visual feedback to the user through two Liquid Crystal Displays (LCDs) and accepts user inputs through directional and push buttons. The ACS Subsystem also interfaces with the other subsystems that make up the complete SAC system.

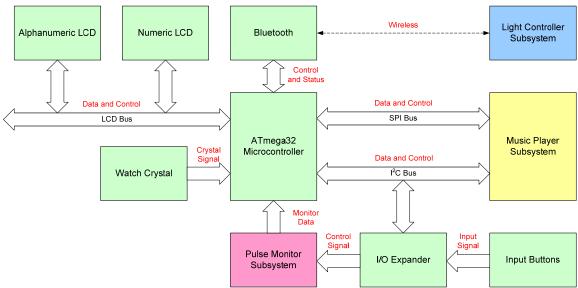

The high level functional block diagram of the ACS is shown in Figure 3.

Figure 3: Functional Block Diagram of the Alarm Clock Subsystem

There are several components of interest: the ATmega32 microcontroller, Alphanumeric LCD, Numeric LCD, I/O Expander, Input Buttons, Bluetooth, and Watch Crystal. The ACS also interfaces with the Light Controller Subsystem, Music Player Subsystem, and Pulse Monitor Subsystem. Through the Pulse Monitor Subsystem, the user's pulse rate is measured and closely monitored for the ideal time to wake the user. Once the ideal time is determined, the Light Controller Subsystem is instructed wirelessly via Bluetooth to gradually increase the intensity of the external light source. The Music Player Subsystem is instructed to begin playing songs at an increasing volume level.

#### 3.1.1. ATmega32 Microcontroller

The central processor of the SAC is the ATmega32 microcontroller from Atmel. The microcontroller is responsible for communicating with various subsystems using various bus interface standards as well as general purpose input/output (GPIO) pins. The ATmega32 is an 8-bit microprocessor with 32 KB of Flash memory, 2 KB of internal static random access memory (SRAM) and 1 KB of Electronically Erasable Programmable Read Only Memory (EEPROM). It boosts a maximum throughput of 16 million instructions per second when operated at 16 MHz. External interrupt lines are also available on the microcontroller for interrupt generation, reducing the need to constantly "poll" the line value. This results in more efficient use of the microprocessor's processing time.

This chip features the Serial Peripheral Interface (SPI), Inter-Integrated Circuit (I<sup>2</sup>C) interface, and Universal Synchronous/Asynchronous Receiver/Transmitter (USART) interface. Both the SPI and I<sup>2</sup>C interfaces allow multiple devices to be connected simultaneously on a single bus, greatly reducing the number of pins used on the microprocessor. Communication over this bus is established in a master-slave fashion. Data lines are pulled-up so that in the event of bus contention, the amount of current flowing through the devices is limited.

The ATmega32 processor was selected based on the amount of features it provided, ease of development and low cost. Cost was also an important discriminator, since mass production of the SAC is intended.

#### 3.1.2. LCM-S02004DSR 20x4 Alphanumeric LCD

To display the user menu, a 20 character by 4 line alphanumeric LCD is used. Due to the amount of text that needs to be displayed at a given time by the user menu, 2 lines will not be sufficient. The LCM-S02004DSR alphanumeric LCD was chosen since it incorporates a dot-matrix LCD driver (which is used to control each alphanumeric character). This allows the microcontroller to change the contents of the LCD using as little as 7 lines.

#### 3.1.3. LCD-S401C71TR Four Digit Numeric LCD

As outlined in the functional specification, the current alarm time must be displayed to the user. This is achieved by using a four digit, 8-segment LCD display. The LCD-S401C71TR in particular is capable of displaying ":" between digits, allowing us to display the time format in "HH:MM" easily.

Figure 4 shows the size of digits on the numeric LCD, measured in millimetre [inches]. The size of these digits can be easily viewed by a person with 20/20 vision over a distance of 20 feet (6.1 meters) [6]. Since users will usually be closer to the alarm than 20 feet, clock visibility will not be an issue.

Figure 4: Digit Size on Numeric LCD

#### 3.1.4. ICM7211 LCD Driver

To reduce the number of lines required to drive the numeric LCD, the ICM7211 LCD driver is used. This allows the microcontroller to control the contents of the LCD using as few as 7 lines. Moreover, it will provide the signals necessary to decode and drive each segment for each digit, since each segment needs to be driven by alternating logic level.

#### 3.1.5. EmbeddedBlue eb505 Bluetooth Module

In order to communicate wirelessly with the Light Controller Subsystem, the EmbeddedBlue eb505 manufactured by A7 Engineering allows us to accomplish this task with minimal prototyping. This module uses the Bluetooth standard for wireless communication. The benefits of using Bluetooth for our design are:

- 1. Provides worldwide specification, small-form factor and low cost.

- 2. Less susceptible to noise and interference due to the use of frequency hopping spread spectrum.

- 3. Ability to form small localized network of up to 8 Bluetooth devices coexisting in master-slave relationship. Allows for possibility of "add-on" components to be designed to expand the functionalities of the SAC.

The reason for using the eb505 is because the complexity of working with the Bluetooth standard, from implementing the Bluetooth protocol stack to circuit layout and antenna matching, is removed. Communication simply requires setting up the connection between the two endpoints. Once the connection is established, a serial port link is established through emulation. Data transmission can then proceed as if using a simple Universal Asynchronous Receiver/Transmitter (UART) device.

Figure 5 shows the eb505 module, which can be easily prototyped.

Figure 5: EmbeddedBlue eb505 Module; front view (Left) and back view (Right)

#### 3.1.6. PCF8575 Remote 16-bit I/O Expander

Due to the large number of input signals required to interface with the input buttons, directly interfacing the buttons with the microprocessor is a pin exhausting process. The PCF8575 I/O expander uses the I<sup>2</sup>C bus to interface with the microprocessor, reducing the pin usage to two pins for the I<sup>2</sup>C interface, and a third pin for interrupt generation. The PCF8575 is a quasi-bidirectional I/O interface, which means that the direction of each I/O port does not need to be individually configured. An interrupt signal can be generated whenever an input signal changes from its previous state, signifying to the microprocessor to perform a read. The interrupt signal is cleared shortly after the read.

#### 3.1.7. Input Buttons

Two types of input buttons are available on the SAC. The ALPS SKQUCAA010 is a 4direction tactile input button with center push is available for navigating through the user menu. Connection to ground is established whenever the button is pushed in a particular direction, or pressed down. Figure 6 shows the appearance of the directional button.

Figure 6: 4-Direction Input Button

The other type of input button used is the tactile push button. Two of these buttons are available, one for turning off the alarm and one for toggling the external light source.

#### 3.1.8. Seiko Tuning Fork Watch Crystal

To perform accurate time-keeping function, a 32.768 kHz watch crystal is used. The watch crystal can be connected to the microcontroller's TOSC1/TOSC2 pins where internal amplification is done. This amplified clock signal is used to clock an 8-bit counter at a rate of 32.768 kHz / 128 = 256 Hz. Thus, the 8-bit timer will overflow every 1 second allowing accurate time-keeping to take place.

The crystal has a frequency deviation of 5 parts per million, or  $\pm 0.16384$  Hz. This effectively creates a deviation of  $\pm 12.96$  seconds over a period of 30 days. This satisfies the functional requirement of no more than  $\pm 1$  minute per month.

#### 3.1.9. Voltage Translators

Although not shown on the high level block diagrams, voltage translation is necessary between certain hardware components and the microprocessor. This is accomplished by using buffers connected to a different power supply rail. Two supply rails are made available: 5 V and 3.3 V. The 74AHC126 buffer connected to 3.3 V supply is used to translate from 5 V to 3.3 V, since this buffer can tolerate input voltage levels much higher than its supply. The 74AHCT244 buffer is used to translate from 3.3 V to 5 V, since the minimum voltage for high input logic level is 2 V. Please refer to the schematic in the Appendix for further details.

#### 3.1.10. LCD Data and Control Bus

The alphanumeric and numeric LCDs share the same data and control bus. This is aptly termed, the LCD Bus. Sharing the LCD Bus reduces the number of I/O pins required without sacrificing performance. Table 1 and Table 2 show the pin assignments for the alphanumeric and numeric LCD, respectively.

| Name    | Туре         | Function          |

|---------|--------------|-------------------|

| DB4~DB7 | Input/Output | Data Bus          |

| R/W     | Input        | Read/Write Select |

| RS      | Input        | Register Select   |

| E       | Input        | Enable            |

Table 1: Alphanumeric LCD Pin Assignment

| Name     | Туре  | <b></b> Function |

|----------|-------|------------------|

| B0~B3    | Input | Data Input       |

| DS1, DS2 | Input | Digit Select     |

| !CS1     | Input | Chip Select      |

Table 2: Numeric LCD Pin Assignment

The LCD data bus consists of 4 lines which encompass DB4~DB7 and B0~B3. The control bus consists of 2 lines which encompass R/W, RS and DS1, DS2. Dedicated control lines are used to control E and !CS1. In total, eight pins are used on the microprocessor.

Data and control can be placed on the bus at any time. As long as E and !CS1 remain low and high, respectively, there is no risk of data being latched. It is the action of strobing these control lines that result in data and control being latched. Provided that E is held low whenever signals are changing on the LCD data and control bus, there is no risk of the alphanumeric LCD trying to drive the data bus (in response to R/W signal being driven low). PORTA on the microcontroller is reserved for interfacing with the LCDs. Please refer to the Appendix for detailed schematics.

#### 3.1.11. Bluetooth Interconnection

The eb505 module has several pins of interest besides the ones that connect to the microcontroller's USART interface. Table 3 shows the pin assignment for the Bluetooth module.

| Name   | Туре   | Function                    |

|--------|--------|-----------------------------|

| TX     | Output | Serial transmit line        |

| RX     | Input  | Serial receive line         |

| Status | Output | Bluetooth connection status |

| Mode   | Input  | Command/Data<br>mode toggle |

| On/Off | Input  | Power eb505 up or<br>down   |

| <b>Table 3: Bluetooth Pin Assignment</b> |

|------------------------------------------|

|------------------------------------------|

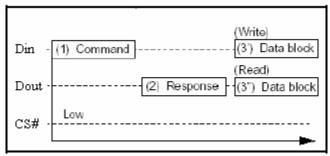

The transmission rate between the local serial port on the TX/RX ranges between 9.6 k and 230.4 kbps. The over-the-air transmission rate ranges between 9.6 k and 115.2 kbps. Two operating modes are possible: command mode and data mode. In command mode, serial commands can be sent to configure the Bluetooth module. Once a connection is

established between two end points, the module automatically switches over to the data mode. In this mode, all data sent along serial port will transmit to the remote device. The Status line can then be used to monitor the connection status.

Please refer to the Appendix for the interconnection between the Bluetooth module and the microcontroller.

#### 3.1.12. I/O Expander Interconnection

The I/O expander uses the  $I^2C$  bus for communication with the microcontroller. The I/O ports are read from and written to all together through the  $I^2C$  bus. Figure 7 shows the block diagram of the I/O expander while Table 4 summarizes the pins of interest and their functionalities.

Figure 7: I/O Expander Block Diagram

| Tuble 4. 1/O Expander 1 in Assignment |              |                           |

|---------------------------------------|--------------|---------------------------|

| Name                                  | Туре         | Function                  |

| !INT                                  | Output       | Interrupt line            |

| A0~A2                                 | Input        | Device address<br>setting |

| P00~P17                               | Input/Output | Input/Output ports        |

| SCL                                   | Input        | Serial Clock              |

| SDA                                   | Input/Output | Serial Data               |

#### Table 4: I/O Expander Pin Assignment

The !INT line is connected to the INT0 pin on the microcontroller, which detects external interrupts. Whenever the input signal changes in logic level, the !INT line will be brought low until data is read from the I/O expander. An interrupt service routine is used to handle this process.

Please refer to the Appendix for detailed schematics of the interconnection between the I/O expander and the microprocessor.

#### 3.1.13. Interconnection with Other Subsystems

The connection between the Music Player Subsystem and the ACS is established through the SPI and I<sup>2</sup>C bus. The two bus interfaces are well-established standards so its operations will not be elaborated. The connection between the Light Controller Subsystem is done wirelessly via Bluetooth. Please refer to the section on the Bluetooth communication protocol for further details. The connection between the Pulse Monitoring Subsystem is done through the I/O expander for control signals, while the measured data comes in to the microcontroller through a GPIO pin that accepts external interrupt.

Please refer to the individual sections on each subsystem for details about interfacing with the ACS.

#### 3.1.14. Power Supply

Power is provided to the ACS through an AC to DC converter that converts 120 VAC to 9 VDC. The adapter is Underwriters Laboratory, or UL certified, which reduces the amount of components that needs to be certified for the production model. Two voltage regulators, KA78R05C and KA78RM33 are used to convert the 9 V into 5 V and 3.3 V, respectively. Two supply rails are required because certain components require 5 V supply, whereas others require 3.3 V.

#### 3.1.15. Physical Enclosure

To shield potential electrical shock from the user, while providing a rigid enclosure, an off-the-shelf plastic case will be used for the prototype model. Holes will be made for mounting the numeric and alphanumeric LCD panels, as well as input buttons. As specified in the functional specification, the LCD panels shall be mounted in the front of the enclosure. The directional button will also be mounted in the front. The Alarm Off and Light On/Off button will be placed on the top of the enclosure. Speakers will be mounted on the front of the case and shall be exposed such that maximum air flow can result from the speakers. Adhesive rubber feet will be used to isolate the plastic enclosure from the surface which it rests on. The rubber feet will also prevent the alarm clock from slipping when buttons are being pushed.

The production model will use a rigid plastic injection molded enclosure with no sharp edges or corners. The enclosure will also be flame retardant to act as a safety redundancy.

#### 3.2. Music Player Subsystem Design

From the functional specifications, the SAC must be able to play audio files of Moving Picture Experts Group Layer 3 (MP3) format. The Music Player Subsystem (MPS) is responsible for MP3 processing as well as interfacing with non-volatile storage. The subsystem must also control the volume level, and increase the volume level gradually during the waking process.

The high level functional block diagram of the MPS is shown in Figure 8.

Figure 8: Functional Block Diagram of the Music Player Subsystem

There are three major components in the functional block diagram: the VS1002d MP3 Audio Codec, Multimedia Card (MMC) and LM4936 Stereo Audio Amplifier. The ACS interfaces with the MPS via two data and control buses, namely the I<sup>2</sup>C and SPI bus. The ACS acts as the master of these two buses. The microprocessor within the ACS reads data from the MMC and passes it to the MP3 Audio Codec for MP3 decoding. The decoded signal constitutes the Left and Right analog audio signals, which are then passed on to the Stereo Audio Amplifier for amplification. The microprocessor can also control the amount of amplification provided in discrete steps. The amplified signal then drives the two speakers, constituting the MPS.

#### 3.2.1. VS10xx Prototyping Board

The foundation of the MPS is the VS10xx Prototyping Board by VLSI Solution Oy, shown in the figure below.

Figure 9: VS10xx Prototyping Board

Overall, the prototyping board will be responsible for audio performances such as MP3 decoding, audio amplification, digital volume control, and audio output to external speakers. Another responsibility of the board is to properly communicate with the ACS to determine when audio is played.

The prototyping board incorporates an MP3 Audio Codec that can decode MP3 audio files of various sampling rates along with a MMC connector for hot-removal and insertion. Onboard power regulation ensures that all chips connected are operating with the correct voltage level. The board also provides a headphone jack with proper circuitry to drive an earphone. An onboard EEPROM contains the boot code required to allow the board to function as a standalone MP3 player.

This prototyping board was chosen to reduce the amount of components we need to assemble manually, since most of the audio circuitry is available for us. Moreover, header pins are available to easily interface with the microprocessor.

#### 3.2.2. VS1002d MP3 Audio Codec

The prototype board incorporates the VS1002d MP3 Audio Codec shown in Figure 10. The codec is capable of decoding Moving Picture Experts Group (MPEG) 1.0 and 2.0 audio layer III files, with sampling rates of 48 kHz and bitrate up to 224 kbps. The single-chip solution includes a high-quality stereo digital to analog converter (DAC), eliminating the need for a separate DAC, and an earphone amplifier for direct driving of a  $30\Omega$  load. Digital volume control allows the external microprocessor to control the volume level.

Figure 10: VS1002d MP3 Audio Codec