November 12, 2007 Dr Andrew Rawicz School of Engineering Science Simon Fraser University Burnaby, British Columbia V5A 1S6

Re: ENSC 440/305 Design Specification for a Wireless Heart Attack Detector

Dear Dr Rawicz,

The enclosed document specifies detail design aspects of a wireless heart attack detector entitled Pulze<sup>™</sup> by Precision Lifestyle Technologies. The Device is currently in the development stage for ENSC 440 course and the prototype is expected to be completed by January 2008.

The accompanying document outlines the design specifications of different parts and features of Pulze<sup>TM</sup>. The document also summarizes testing procedures that the device has to fulfill upon completion. A detailed approach has been conducted in preparing this document and Precision Lifestyle Technologies' team members will follow the stated specifications as their guideline throughout Pulze's <sup>TM</sup> design process.

PLT's dedicated, talented and motivated team of senior engineering students is comprised of Piraj Fozoonmayeh, Mojtaba Gharehbaghi and Sara Moghaddamjoo. For further information or any concern you may have please do not hesitate to contact me by phone at (778) 883-2424 or by email at ensc440-psm@sfu.ca .

Sincerely,

Sara Moghaddamjoo CEO Precision Lifestyle Technologies Inc.

**Design Specification for:**

# **Wireless Heart Attack Detector**

Submitted to:

Dr. Andrew Rawicz Mr. Mike Sjoerdsma School of Engineering Science Simon Fraser University

Issue Date: November 12, 2007 Revision: 1.0 Project Team:

Piraj Fozoonmayeh Sara Moghaddamjoo Mojtaba Gharehbaghi

Contact Person:

Sara Moghaddamjoo sma22@sfu.ca

# **Executive Summery**

According to the World Health Organization report of 2002, 59% of deaths were the result of non communal conditions. Of which, 29% of deaths were related to cardiovascular complications. To attain a better visual of this percentage, approximately 10 million people in a year die resulting from cardiovascular complications.

The elderly are more prone to heart attacks; however, many cardiovascular diseases are hereditary. Therefore, anyone regardless of age should take significant precautions in order to prevent a heart attack and adapt to a healthier life style.

Regardless of how many precautions are taken to prevent heart attacks, the fact remains that it is still the leading cause of death. Most heart attacks could be somewhat maintained if the patient is to receive the needed medical attention in time. However, not everyone knows what a heart attack is like or what to do in case of such an emergency; hence a lot of heart attacks amount to death due to either the patient not being aware or not being able to seek medical attention in sufficient time.

Our company's main objective is to design a functioning device that would alert the emergency personnel when a person is having a heart attack in the shortest time possible in order for them to promptly receive medical assistance. This device is attached to the user and will detect the heart attack and send a signal to the user's cell phone wirelessly in just seconds which is then transmitted to emergency personnel. This innovative product is compact and portable and can be used easily by a wide variety of people, ranging from athletes to seniors.

Existing solutions include a portable hand held ECG monitor which records a person's cardiac functions and displays the data on the monitor of the device. This device monitors the heart beat constantly but does not have the ability of alerting emergency personnel. This product's main objective is to record various heart readings that can be presented to the doctor to monitor a patient's heart abnormalities.

Precision Lifestyle Technologies is a Bio-medical engineering company founded by three senior Simon Fraser University engineering students dedicated to innovating and pioneering telemedicine equipments. By incorporating leading edge technologies and medical sciences, we hope to open up novel horizons not only to patients in need but also to healthy individuals to prevent health complications. We believe well-being is a right and we strive to offer the most practical and smartest solutions.

We have forecasted a tentative budget of \$585 for this thirteen week project, and we at Precision Lifestyle Technologies will make our greatest attempt at completing this project within the allocated budget if not under.

# **Table of Contents**

| Executive Summery                                                            | 3  |

|------------------------------------------------------------------------------|----|

| Table of Contents                                                            | 4  |

| List of Figures                                                              | 5  |

| List of Table                                                                | 6  |

| 1. Introduction                                                              | 7  |

| 1.1. Scope                                                                   | 9  |

| 1.2. Glossary                                                                | 9  |

| 1.3. Intended Audience                                                       | 9  |

| 2. System Overview                                                           | 10 |

| 3. System Hardware Design                                                    | 12 |

| 3.1 Data Acquisition Circuit                                                 | 13 |

| 3.1.1 Alternative Circuits                                                   | 19 |

| 3.1.2 PCB design                                                             |    |

| 3.2 PIC16F877 Controller Board                                               |    |

| 3.1.1 Specifications                                                         |    |

| 3.1.2 Power Supply                                                           |    |

| 4. Firmware Design                                                           |    |

| 4.1 Hardware                                                                 |    |

| 4.1.1 Processing Unit<br>4.1.2 The Pearl Blue Bluetooth module               |    |

| 5. Physical Design                                                           |    |

| 6. Software Design                                                           |    |

| 6.1 Programming Strategy                                                     |    |

| 7 Test Plan                                                                  |    |

| 7.1 Proof of Concept Experiments                                             |    |

| 8 Special feature and future work                                            |    |

| 9 Conclusion                                                                 |    |

| 10 References                                                                |    |

| 10 References                                                                |    |

| Appendices                                                                   |    |

| Appendix I: Phis descriptions and layout of Microcontroller board pin layout |    |

| Appendix II. Description of FIC 10F8// Microcontroller board pin layout      |    |

# **List of Figures**

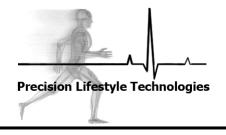

| Figure 1: Standard electrocardiogram (ECG)                                                    | 8  |

|-----------------------------------------------------------------------------------------------|----|

| Figure 2: System Overview                                                                     |    |

| Figure 3: System Block Diagram                                                                | 11 |

| Figure 4: System Components                                                                   | 12 |

| Figure 5: Overall Data Acquisition Circuit                                                    | 13 |

| Figure 6: Instrumentation Amplifier Circuit                                                   | 15 |

| Figure 7: Instrumentation Amplifier Simulation                                                | 16 |

| Figure 8: The filter Stage                                                                    |    |

| Figure 9: The Non-Inverting Amplifier and Output Stage                                        | 18 |

| Figure 10: Data Acquisition circuit using AD620.                                              | 19 |

| Figure 11: Data Acquisition circuit using INA128                                              | 19 |

| Figure 12: PCB Design of the Overall Signal Acquisition Circuit                               | 20 |

| Figure 13: Top layer of PCB design                                                            | 20 |

| Figure 14: Bottom Layer of PCB design                                                         | 21 |

| Figure 15: PIC16F877 microcontroller board                                                    |    |

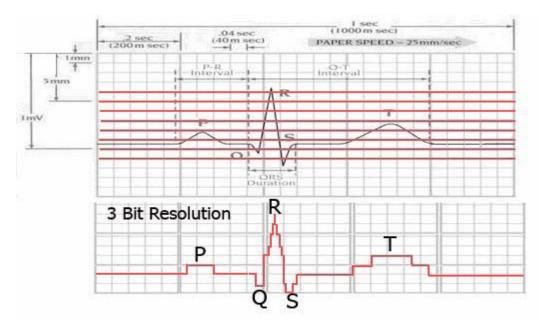

| Figure 16: Reconstruction of the Signal with 3 Bit Resolution                                 | 24 |

| Figure 17: Flowchart of how the heart attack is detected.                                     |    |

| Figure 18:PIE1 and PIR1 registers of the A/D                                                  | 27 |

| Figure 19: ADCON0 register bits layout                                                        | 28 |

| Figure 20: ADCON1 register bits layout                                                        | 29 |

| Figure 21: OPTION_REG Register bit specification                                              | 31 |

| Figure 22: RCSTA register bit specification                                                   | 33 |

| Figure 23: TXSTA register bit specification.                                                  |    |

| Figure 24: The Pearl Blue Bluetooth module connection diagram                                 |    |

| Figure 25: Physical design of the system (front view)                                         |    |

| Figure 26: Physical design of the system (back view)                                          |    |

| Figure 27: J2ME cell phone application Flow Designer MIDP 2.0                                 |    |

| Figure 28: Flow chart of cell phone application to initiate a call                            |    |

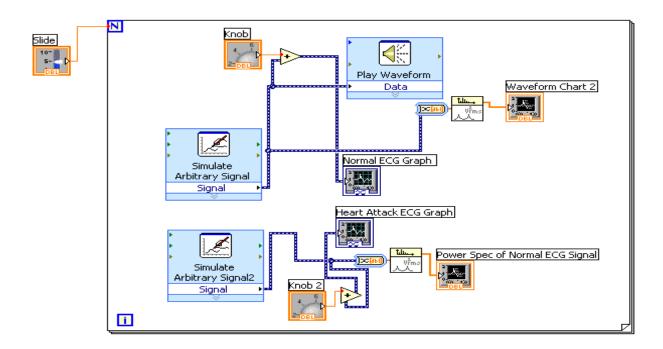

| Figure 29: Block diagram of generating the regular and heart attack signal using LabView      |    |

| Figure 30: Normal ECG signal (on the right) and a heart attack signal generated using LabView |    |

| Figure 31: Noise reduction and feature extraction by LabView                                  |    |

| Figure 32: Power spectrums of the normal and abnormal ECG signal                              | 45 |

# List of Table

| Table 1: Circuit Values                     |  |

|---------------------------------------------|--|

| Table 2: The PIC16F877 specifications       |  |

| Table 3: ADCON0 register bits specification |  |

| Table 4: ADCON1 register bits specification |  |

| Table 5: Physical Dimensions of Parts.      |  |

| Table 6: Overall Physical Dimension         |  |

|                                             |  |

# 1. Introduction

Telemedicine is a new advancement in delivery of clinical care through information technology and communication devices. This technology could be used immensely for disease detection and therapeutic purposes. Early detection of a disease at its preliminary stages could profoundly reduce the risks and complications that may arise with time.

In 2004 United States statistical data recognized coronary heart disease as the leading cause of death among American citizens. Each year 1,200,000 cardiac attacks are reported, from which 38 percent of these cases result in death [1]. In other words, one in every three incidences of heart attack results in death. Considering the world population of more than six billion people, millions of people are susceptible to death by heart attack. To reduce these horrific numbers we should concentrate our resources and technologies on improving early detection devices to further assist physicians to communicate with their patients on a daily basis since some heart complications may arise without prior warning.

An Electrocardiogram (ECG), shown in Figure 1, measures heart beat electrical activity which generates a wave or impulse through the heart muscles. This electrical impulse would constrict the cardiac muscles, which in turn causes blood to be pumped out of the heart into arteries. With patients with cardiac issues, an ECG allows the physician to know the length of time required for an electrical wave to travel through the heart. This information determines whether the electrical activity is normal, too fast/slow or irregular. An ECG can also give information about the size and health-state of the heart based on the amount of electrical activity that passes through the heart muscle. Based on these types of information, an ECG can detect a heart attack.

The ECG technology has had an enormous impact for diagnostic purposes since its discovery; however, to further enhance ECG technology, improvements can be implemented. For instance, available ECG devices lack the advantage of being portal and hence they impose physical and spatial restrictions on the patient and the doctor. Moreover, an ECG device is able to detect a heart attack only after it has occurred, and by that time it may be too late to save the patient's life. To this date, little improvement on the ECG devices has been implemented to enable faster and better communication between the patient and the doctor. Therefore, the flaws that this technology is experiencing at this time should be recognized and actions should be taken to further improve its functionality to serve human lives more efficiently.

Our proposed system not only detects heart attacks for immediate assistance, but also could be used for various other applications.

- 1- The rate at which a heart beats plays an important role especially in catabolic exercises such as cardio exercises, so this device may also be used by athletes and people that would like to lose weight.

- 2- The design of the bio-sensors may be modified for other medicine applications such as using a respiratory sensor to detect respiratory problems.

#### 1.1. Scope

The scope of this document covers the design requirements which need to be met mainly for the proof-ofconcept version of Pulze<sup>TM</sup>. Accordingly, some of the design specifications for the production version may change during the prototype design. The design requirements presented in this document characterize the current customers' demand from the product. After thorough market studies and testing of the concept, the final modification of the device will be prepared for the production.

#### 1.2. Glossary

| e: Measurement of speed in data transmission |  |  |  |  |

|----------------------------------------------|--|--|--|--|

| Configuration                                |  |  |  |  |

|                                              |  |  |  |  |

| l record of the cardiac activity             |  |  |  |  |

| mmable ROM                                   |  |  |  |  |

|                                              |  |  |  |  |

| l medical Radio Bands                        |  |  |  |  |

| n                                            |  |  |  |  |

| toolkit                                      |  |  |  |  |

| Profile                                      |  |  |  |  |

|                                              |  |  |  |  |

| 7                                            |  |  |  |  |

|                                              |  |  |  |  |

|                                              |  |  |  |  |

| hronous Receiver/Transmitter                 |  |  |  |  |

|                                              |  |  |  |  |

# 1.3. Intended Audience

The main purpose of this document is to act as a guideline to help the engineers in design, integration and quality assurance of Pulze<sup>TM</sup>. PLT's executives can also use the design specification document as a guide to ensure that the development process is inline and to control and to direct the progress toward the end according to the user's expectations from the device. Another intended purpose of this document is to provide a test plan for test engineers and to certify the product specifications for future marketing phase of development.

# 2. System Overview

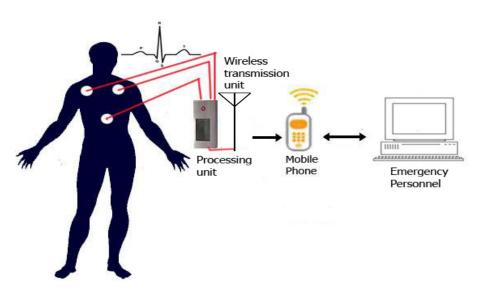

The aim of our project is to enhance the ECG technology to allow early detection of heart attack before a patient experiences it. We believe this device can save millions of lives around the world by making it possible to detect a heart attack in advance, allowing the physicians sufficient time for patient care and treatment in hopes to prevent cardiac arrest and death. By taking advantage of one of the communication technologies that is available today, namely, Bluetooth, our aim is to design and implement a device that can be easily worn as an accessory to monitor the heart beat. The data is monitored in this system in real time and as soon as an abnormality in heart beat is detected, the data are transmitted to the patient's cell phone via Bluetooth connection. Afterward an emergency alarm is transmitted to alert an emergency unit provided by PLT. We believe our device is able to enhance life for patients prone to heart attack by providing them with the required medical attention promptly. Figure 2 shows the overview of the system.

#### Figure 2: System Overview

http://www.vanth.org/vibes/images/normalECG2.PNG http://zone.ni.com/devzone/cda/tut/p/id/6361 http://www.widenclinic.com/images/human\_figure.gif

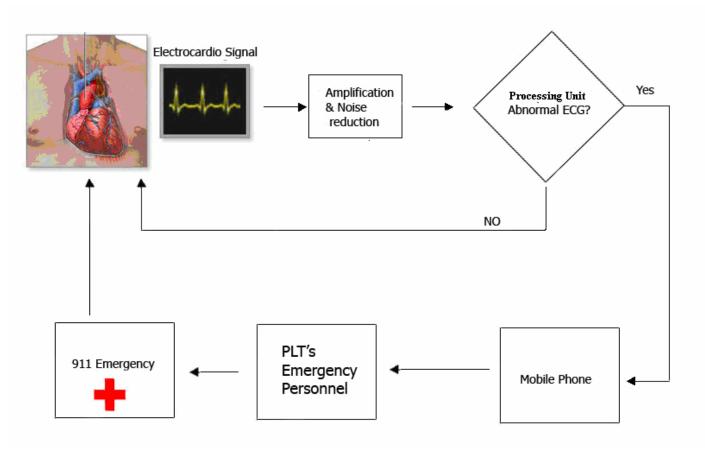

The heart signal will be captured via ECG sensors; noise reduction will take place, followed by signal amplification. The amplified signal will be digitized via a microprocessor, and it will be processed. In the next step, signal conditioning will be applied to detect any abnormality of the heart signal. If an abnormality is detected, the signal will be transmitted to a mobile phone via Bluetooth. The mobile phone in turn will alert appropriate agencies. Figure 3 demonstrates a block diagram of PULZE<sup>TM</sup> System.

### Figure 3: System Block Diagram

http://apps.uwhealth.org/health/adam/graphics/images/en/8772.jpg http://abhishek.tiwari.com/wp-content/uploads/2007/07/red\_cross.png

# 3. System Hardware Design

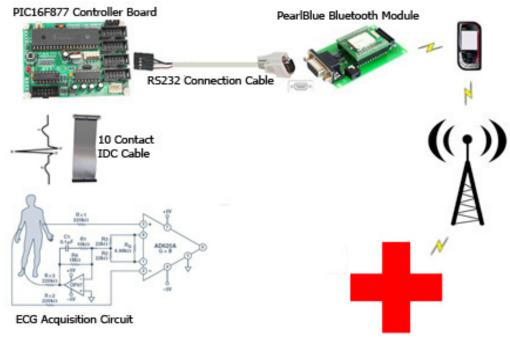

As described in the system overview section, wireless heart attack detection system is built up of different components. The design and specification of every part are described in the following section. The overall system components are presented in Figure 4.

Figure 4: System Components

www.datasheetcatalog.com/datasheets\_pdf/A/D/6/2/AD620.shtml www.gshop.com.au/images/ide\_133\_cable.jpg www.emxys.com/docs/PearlBlue\_Fact\_Sheet.pdf www.futurlec.com/PIC16F877\_Controller.shtml www.more-shop.co.uk/images/medium/mtom\_serial\_90\_com\_MED.png abhishek.tiwari.com/wp-content/uploads/2007/07/red\_cross.png www.vanth.org/vibes/images/normalECG2.PNG www.wpclipart.com/telephone/antenna.png

# **3.1 Data Acquisition Circuit**

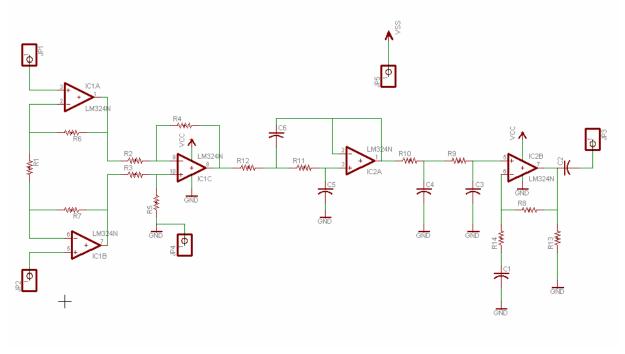

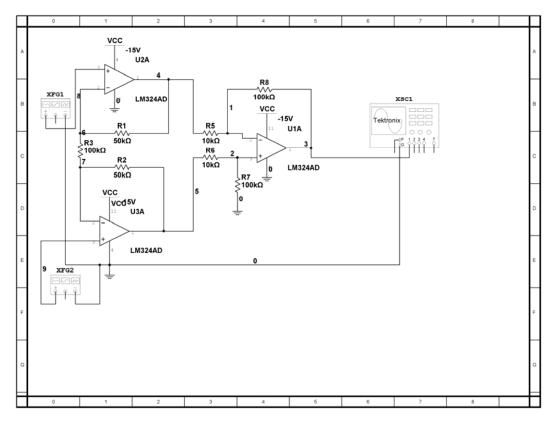

The overall data acquisition circuit which we have procured using simulation tools is shown in Figure 5.

Figure 5: Overall Data Acquisition Circuit

Table 1 summarizes the values used for the overall circuit. The values have been tested and simulated using MULTISIM <sup>TM</sup> simulation software.

| 5 |

|---|

| 5 |

| Label | Value             |

|-------|-------------------|

| R1    | 100K Ohms         |

| R2    | 10K Ohms          |

| R3    | 10K Ohms          |

| R4    | 100K Ohms         |

| R5    | 100K Ohms         |

| R6    | 50K Ohms          |

| R7    | 50K Ohms          |

| R8    | 100K Ohms         |

| R9    | 100K Ohms         |

| R10   | 100K Ohms         |

| R11   | 100K Ohms         |

| R12   | 100K Ohms         |

| R13   | 10K Ohms          |

| R14   | 100K Ohms         |

| C1    | 33 uF             |

| C2    | 10 uF             |

| C3    | 0.1 uF            |

| C4    | 0.1 uF            |

| C5    | 0.1 uF            |

| C6    | 0.1 uF            |

| PIN1  | Input 1           |

| PIN2  | Input 2           |

| PIN3  | Output            |

| PIN4  | Reference Voltage |

| Vcc   | 9V                |

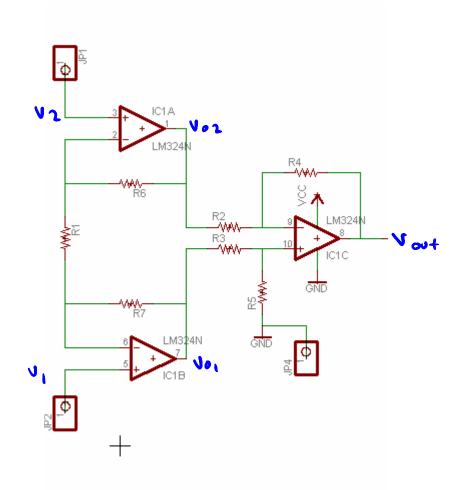

In order to get the signals due to action of the nerves of the heart muscle, a difference amplifier can be used. The acquired signal is in the order of microvolt, and is swamped by other noise and static present on human body. Therefore a circuit is needed to eliminate any common noise present on the inputs and amplify the difference between two common voltages. Also the desired degree of precision requires that the op-amp circuit not load down the measured circuit at all. Therefore an instrumentation amplifier can be used as an improvement to a regular difference amplifier. Figure 6 presents the schematic of our instrumentation amplifier.

Figure 6: Instrumentation Amplifier Circuit

The output voltage of the instrumentation amplifier can be found using the following equation:

$$V_{out} = \frac{R_2}{R_1} (1 + \frac{2R_B}{R_A}) (v_1 - v_2) = \frac{R_2}{R_1} (v_{o1} - v_{o2})$$

Figure 7 illustrates the simulation of the instrumentation amplifier stage of the data acquisition circuit.

Figure 7: Instrumentation Amplifier Simulation

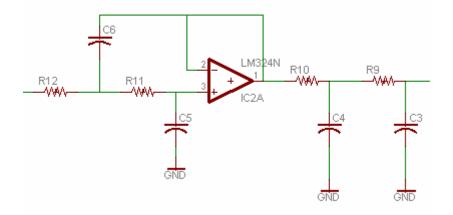

Since the action of the nerves in the heart muscles are relatively slow (on the order on milliseconds), we can incorporate several low pass filters to eliminate any high frequency noise that may be present on our signal as well. A few R-C combinations have been used to effectively filter off any high frequency noise that is present on the signal. Also a buffer amplifier is used in order to prevent the amplification circuit from loading the first circuit unacceptably and interfering with its desired operation. The schematic of the buffer and low pass circuits have been presented in Figure 8.

Figure 8: The filter Stage

The cut off frequency for all the low pass filters used in our circuit is as followed:

$$f_{LP} = \frac{1}{2\pi RC}$$

$$\omega_{LP} = \frac{1}{RC} = \frac{1}{0.1 \times 10^{-6} \times 100 \times 10^{3}} = 1 \frac{radians}{sec}$$

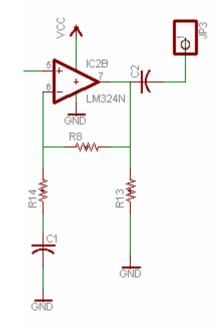

The last stage of the signal acquisition is the non-inverting amplifier stage which has been shown in Figure 9. The gain of this stage has been calculated as followed:

$$Gain = 1 + \frac{R_8}{R_{14}} = 1 + \frac{100K}{4.8K} = 22.27$$

Therefore the signal has been amplified 22 times. Also a high pass filter have been used at the last stage in order to filter out baseline wandering noise or any remaining high frequency noise cause by the circuit. The cut off frequency of the high pass filter is as followed:

School of Engineering Science • Burnaby, BC • V5A 1S6 www.precisionlifestyletech.com

The Heart of Medical Advances.

$$f_{LP} = \frac{1}{2\pi RC}$$

$$\omega_{LP} = \frac{1}{RC} = \frac{1}{10 \times 10^{-6} \times 10 \times 10^{3}} = 0.1 \frac{radians}{sec}$$

Figure 9: The Non-Inverting Amplifier and Output Stage

The IC used for the data acquisition circuit is LM324 amplifier. The supply voltage for all the amplifiers will be provided by a 9 Volt battery.

#### **3.1.1 Alternative Circuits**

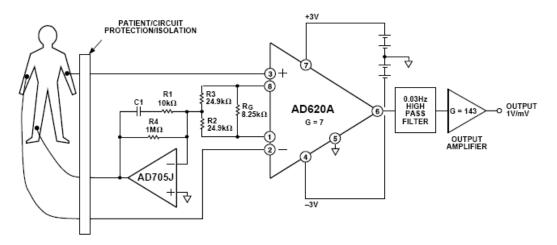

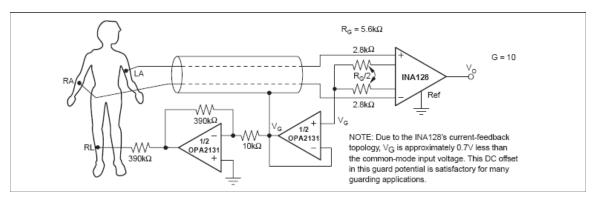

Figure 10 and Figure 11 illustrate alternative circuit configurations for ECG signal acquisition using AD620 and INA128 instrumentation amplifiers. These circuits are intended to be implemented for the commercialization version of PULZE<sup>TM</sup>.

#### Figure 10: Data Acquisition circuit using AD620.

www.datasheetcatalog.com/datasheets\_pdf/A/D/6/2/AD620.shtml

#### Figure 11: Data Acquisition circuit using INA128.

www.datasheetcatalog.com/datasheets\_pdf/I/N/A/1/INA128.shtml

School of Engineering Science • Burnaby, BC • V5A 1S6 www.precisionlifestyletech.com

The Heart of Medical Advances.

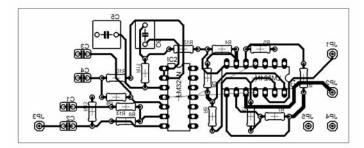

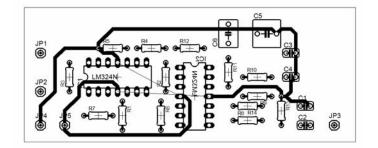

### 3.1.2 PCB design

Figure 12 presents the PCB board design the signal acquisition circuit, for both the top and bottom layers. Figure 13 and Figure 14 show the top and bottom layers of the circuit respectively.

Figure 12: PCB Design of the Overall Signal Acquisition Circuit

Figure 13: Top layer of PCB design

Figure 14: Bottom Layer of PCB design

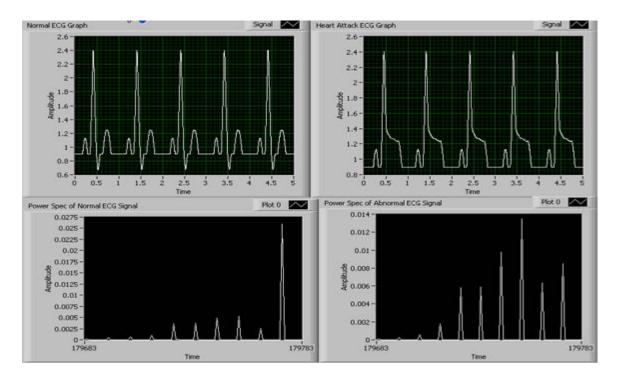

# 3.2 PIC16F877 Controller Board

After ECG signal is captured by the ECG circuit, it has to be processed. We will use the PIC16F877 as our microcontroller in the system. There are various reasons for choosing this particular microcontroller board such as a very reasonable price and accessible ports. Moreover the onboard crystal will make the system more reliable. The mentioned controller board also allows in-circuit programming using only a wire. Figure 15 presents the PIC16F877 controller board.

Figure 15: PIC16F877 microcontroller board

http://www.futurlec.com/PIC16F877\_Controller.shtml

### **3.1.1 Specifications**

The specifications of the PIC16F877 are as following:

- Microcontroller: PIC16F877-20/P

- Main Crystal: 10.000MHz

- Speed: 2.5MHz

- Processor Language: PICMemory

- Program Flash Memory (Internal): 8kBytes

- RAM Memory (Internal): 368 Bytes

- EEPROM Memory (Internal): 256 BytesInput/Ouput

- I/O Points Available: 28

- I/O Points Connection: IDCC Connector A/D

- A/D Channels: 8

- A/D Accuracy: 10-bit Timers

- Timers: One 16-bit Timer and Two 8-bit Timers

- Capture/Compare: 2 Modules with PWM Auxiliary Communication

- RS232 Communication

- Dimensions: 82mm x 62mm x 25mm

### 3.1.2 Power Supply

The power input of the microcontroller will be 5 V DC. The power supply of the device though will be a 9 volt battery.

# 4. Firmware Design

### 4.1 Hardware

### **4.1.1 Processing Unit**

As previously discussed in our functional specification, the processing unit needs to have at least the following specifications:

- 1. A/D with at least 200 Hz sampling frequency

- 2. A/D with at least 3 bit resolution. Figure 16 represents the reconstruction of the signal with 3 bit resolution

- 3. Timer which allows the microcontroller to detect the R to S transition.

- 4. Serial communication.

In order to meet the above specifications, Microcontroller PIC16F877 will be chosen. PIC 16F877 is a 40-pin 8-Bit CMOS FLASH Microcontroller from Microchip. 16F877 uses 3 operating speeds with 4, 8, or 20 MHz clock input. Each instruction cycle takes four operating clock cycles, so when using 20MHz oscillator, each instruction will take about 0.2  $\mu$ s. Table 2 illustrates some of specifications of the PIC16877.

| Programmable Flash Memory (Internal) | 8K Bytes                                  |

|--------------------------------------|-------------------------------------------|

|                                      |                                           |

| RAM Memory (Internal)                | 368 Bytes                                 |

| EEPROM Memory (Internal)             | 256 Bytes                                 |

| Interrupts                           | 14                                        |

| I/O Ports                            | Ports A, B, C, D, E                       |

| Timers                               | 3 (One 16-bit Timer and Two 8-bit Timers) |

| Capture/Compare/PWM Modules          | 2                                         |

| Serial Communications                | MSSP, USART                               |

| 10-bit Analog-to-Digital Module      | 8 channels                                |

| Instruction Set                      | 35                                        |

Table 2: The PIC16F877 specifications

There are two types of internal memories: program and data memory. Program memory is provided by 8K bytes of FLASH Memory, and data memory has two sources namely a 368-byte RAM and a 256-byte EEPROM. Moreover, pins descriptions are presented in appendix I.

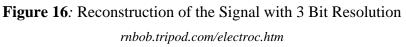

Heart attack will be detected by acquiring the time it takes for the detected ECG signal to descend from the R wave peak to the baseline and comparing it to the time that R wave of a normal ECG signal takes to descend to baseline.

The microcontroller will convert analog signals from the ECG unit to digital using the A/D converters. The A/D converter will buffer the data. As mentioned above, data will be used to detect heart attack by comparing it with the characteristic of a normal heart signal. The A/D module will be discussed in detail later in the document.

If the heart attack is detected in 10 consecutive periods, an alert will be sent in the defined format using the USART serial port to the Bluetooth module. The flowchart is presented in Figure 17.

**Figure 17:** Flowchart of how the heart attack is detected.

#### 4.1.1.1 Input signal PORT

We will use PortA for our analog input signal. PortA is a 6-bit wide bidirectional port and the data direction of this port will be handled by the data direction register TRISA. By setting this bit, the direction of the port will be set as input. Operation of each pin is being controlled by ADCON1 register (A/D Control Register1). The A/D control register is explained in more detail in the following section.

#### 4.1.1.2 A/D

In our system positive reference voltage will be at +5V and negative reference at the ground and the conversion range will be at 5V. Our A/D has 10 bit resolution, so if we divide our voltage range (5V) by 1024 ( $2^{10}=1024$ ) the step size will be 5/1024=0.0048V or 4.88mV.

The 4.88mV is the actual resolution of our system. The resolution is the smallest voltage change that our system can measure.

There are two registers involved with A/D conversion: PIE1 (Peripheral Interrupt Enable 1) register and PIR1 (Peripheral Interrupt Request 1) register. Figure 18 represents the mentioned registrars in more detail.

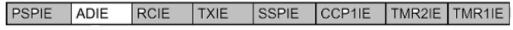

#### PIE1 REGISTER (8Ch)

ADIE: A/D Converter Interrupt Enable bit

1 = Enables the A/D converter interrupt

0 = Disables the A/D converter interrupt

#### PIR1 REGISTER (0Ch)

| PSPIF                                                                                                               | ADIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF |

|---------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--------|--------|--------|

| ADIF: A/D Converter Interrupt Flag bit<br>1 = An A/D conversion completed<br>0 = The A/D conversion is not complete |      |      |      |       |        |        |        |

| Figure 18: PIE1 and PIR1 registers of the A/D                                                                       |      |      |      |       |        |        |        |

| http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf                                                          |      |      |      |       |        |        |        |

The task of PIE1 register is to grant or deny a peripheral interrupt while PIR1 register indicates the status of the conversion. We only use the  $6^{th}$  bit of these registers (ADIE and ADIF). ADIF will be set to one when the conversion is completed and it changes to zero when incomplete. The ADCON0 register controls the A/D converter and the ADCON1 register configures the port pins. Different bits of the mentioned registers are presented in Figure 19 and Figure 20. Moreover each bit is described in Table 3 and Table4.

### ADCON0 REGISTER (ADDRESS: 1Fh)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|-------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE |     | ADON  |

| bit 7 |       |       |       |       |         |     | bit 0 |

#### Figure 19: ADCON0 register bits layout

http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf

#### Table 3: ADCON0 register bits specification

| from the internal<br>or)<br>AN0)<br>AN1)<br>AN2) |

|--------------------------------------------------|

| or)<br>AN0)<br>AN1)<br>AN2)                      |

| or)<br>AN0)<br>AN1)<br>AN2)                      |

| or)<br>AN0)<br>AN1)<br>AN2)                      |

| AN0)<br>AN1)<br>AN2)                             |

| AN1)<br>AN2)                                     |

| AN2)                                             |

| · ·                                              |

| 3.70                                             |

| AN3)                                             |

| AN4)                                             |

| AN5)(1)                                          |

| AN6)(1)                                          |

| AN7)(1)                                          |

|                                                  |

| rogress (setting this                            |

| rsion)                                           |

| in progress (this bit                            |

| by hardware when                                 |

|                                                  |

| as '0'                                           |

| le is operating                                  |

| le is shut-off and                               |

| current                                          |

|                                                  |

# ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| ADFM  | _   | _     | _   | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |     |       |       |       | bit 0 |

#### Figure 20: ADCON1 register bits layout

http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf

#### Table 4: ADCON1 register bits specification

| bit 7   | ADFM: A/D Result Format Select bit<br>1 = Right justified. 6 Most Significant bits<br>of ADRESH are read as '0'.<br>0 = Left justified. 6 Least Significant bits<br>of ADRESL are read as '0'. |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 3-0 | <b>PCFG3:PCFG0</b> : A/D Port Configuration Control bits:                                                                                                                                      |

After specifying a port as input (Port A will be chosen as input) following steps should be taken in order to get A/D conversion:

- 1. Make PORTA as inputs by setting all bits of TRISA register

- 2. Disable A/D interrupt by clearing ADIE bit of PIE1 register

- 3. Configure ADCON0 register and ADCON1 register

- 4. Start A/D conversion by setting GO/~DONE bit of ADCON0 register.

- 5. Read converted data from the A/D result register

#### 4.1.1.3 Timer

The detection of heart attack is done by use of a timer, we measure timing characteristic of the normal ECG and compare it with the one from patient.

Pic16F877 has 3 types of timers:

1-Timer0: 8-bit timer/counter with 8-bit pre-scalar

2-Timer1: 16-bit timer/counter with pre-scalar, can be incremented during SLEEP via external crystal/clock

3-Timer2: 8-bit timer/counter with 8-bit period register, pre-scalar and post-scalar

Since the required specification of our project for timer is very low, we are going to use the Timer0.

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable pre-scalar

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge selection for external clock

#### 4.1.1.4 Pre-scaling

The timer mode is selected by clearing the TOCS bit of the Regiter\_5 and in this mode the timer0 module will increment every instruction cycle (without pre-scalar). Pre-scaling comes from the fact that the instruction-cycle is too fast in the microcontroller. Therefore, if our timer is being incremented once every instruction and if our microcontroller has 20 MHz crystal oscillator, this means that every instruction takes about 0.0000002 S, and since the timer is 8 bits (max 255), therefore it takes 255\*0.000002=0.000051S for it to over flow.

In order to have 1 Sec, we need to have 19500 overflows. By pre-scaling, our microcontroller gives multiple instructions for increment. For example 1:256 means that the microcontroller will increment once every 256 instruction. This mean the overflow happens roughly every 255\*256\*0.000002=0.013056 Sec. So 1 sec will need 76 overflows.

We can assign the pre-scaling to Timer0 by clearing the PSA control bit (OPTION\_REG<3>).

Timer0 can be started or stopped by the TOCS bit of OPTION\_REG. The increment will come based on the value of the pre-scalar. So in order to get the exact time, we need to count the overflows of TMR0 register by looking at its TOIF flag (set when overflow). Moreover, we can set the triggering Timer0 interrupt. Figure 21 represents the OPTION\_REG Registrar specification.

#### REGISTER 5-1: OPTION\_REG REGISTER

|         | R/W-1                                                               | R/W-1                            | R/W-1        | R/W-1        | R/W-1         | R/W-1                     | R/W-1        | R/W-1 |

|---------|---------------------------------------------------------------------|----------------------------------|--------------|--------------|---------------|---------------------------|--------------|-------|

|         | RBPU                                                                | INTEDG                           | TOCS         | TOSE         | PSA           | PS2                       | PS1          | PS0   |

|         | bit 7                                                               |                                  |              |              |               |                           |              | bit 0 |

|         |                                                                     |                                  |              |              |               |                           |              |       |

| bit 7   | RBPU                                                                |                                  |              |              |               |                           |              |       |

| bit 6   | INTEDG                                                              |                                  |              |              |               |                           |              |       |

| bit 5   |                                                                     | R0 Clock So                      |              | bit          |               |                           |              |       |

|         |                                                                     | tion on TOCH<br>al instruction   |              |              |               |                           |              |       |

| bit 4   |                                                                     | R0 Source E                      | ,            | . ,          |               |                           |              |       |

| 511.4   |                                                                     | nent on high-                    |              |              | CKI pin       |                           |              |       |

|         | o = Increm                                                          | nent on low-t                    | o-high trans | ition on TO  | CKI pin       |                           |              |       |

| bit 3   | PSA: Prescaler Assignment bit                                       |                                  |              |              |               |                           |              |       |

|         |                                                                     | aler is assign<br>aler is assign |              |              | le            |                           |              |       |

| bit 2-0 |                                                                     | -                                |              |              |               |                           |              |       |

| 011 2-0 | PS2:PS0: Prescaler Rate Select bits<br>Bit Value TMR0 Rate WDT Rate |                                  |              |              |               |                           |              |       |

|         | Bit value                                                           |                                  | 1            | ę.           |               |                           |              |       |

|         | 000                                                                 | 1:2                              | 1:1          |              |               |                           |              |       |

|         | 010                                                                 | 1:8                              | 1:4          |              |               |                           |              |       |

|         | 011                                                                 | 1:16                             | 1:8          |              |               |                           |              |       |

|         | 100                                                                 | 1:32                             | 1:16         |              |               |                           |              |       |

|         | 101                                                                 | 1:64                             | 1:32         |              |               |                           |              |       |

|         | 110                                                                 | 1 : 128<br>1 : 256               | 1:64         |              |               |                           |              |       |

|         | 111                                                                 | 1.200                            | 1.120        |              |               |                           |              |       |

|         | Legend:                                                             |                                  |              |              |               |                           |              |       |

|         | R = Reada                                                           | able hit                         | W - V        | Vritable bit | LL = Lloissel | amontad b                 | it read as " | n'    |

|         | K = Keada                                                           | able bit                         | vv = v       | vinable bit  | 0 – Onimpi    | lemented bit, read as '0' |              |       |

#### Figure 21: OPTION\_REG Register bit specification

http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf

#### 4.1.1.5 Serial Communication:

The PIC16F877 supports 2 types of serial communication:

- 1- Universal Synchronous Asynchronous Receiver Transmitter (USART) module

- 2- Synchronous Serial Port (SSP) module

In this project we will use USART serial I/O to communicate with the Pearl Blue Bluetooth module. (The Bluetooth module will be discussed in detail later in the document). The USART is capable of transmitting and receiving synchronous and asynchronous data. We have chosen to use asynchronous because the synchronous communication is more complex and the clock has to be sent along with the data.

The PIC16F877 USART module is controlled by a few Special Function Registers:

1-RCSTA (receive status in bank 0 at 18h)

2-TXSTA (Transmit status in bank 1 at 98h)

3-SPBRG (Baud Rate Generator in bank 1 at 99h)

4- PIR1 (Peripheral Interrupt Register in bank 1 at 0CH)

Since the two serial ports RX (pin#26) and TX (pin#25) are also used by PORTC, therefore it is necessary to set both the Serial Port Enable bit (RCSTA bit 7) and TRISC (bit 7:6) bit , to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

Figure 22 and Figure 23 and represent RCSTA and TXSTA register bit specifications.

| REGISTER 10-2: | RCSTA: R                                                                                                                                                                                                                                               | ECEIVE S                                 | TATUS AN     | DCONTR        | OL REGIST    | ER (ADD    | RESS 18h)   |       |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------|---------------|--------------|------------|-------------|-------|

|                | R/W-0                                                                                                                                                                                                                                                  | R/W-0                                    | R/W-0        | R/W-0         | R/W-0        | R-0        | R-0         | R-x   |

|                | SPEN                                                                                                                                                                                                                                                   | RX9                                      | SREN         | CREN          | ADDEN        | FERR       | OERR        | RX9D  |

|                | bit 7                                                                                                                                                                                                                                                  |                                          | •            |               |              |            |             | bit 0 |

| bit 7          | <b>SPEN:</b> Serial Port Enable bit<br>1 = Serial port enabled (configures RC7/RX/DT and RC6/TX/CK pins as serial port pins)<br>o = Serial port disabled                                                                                               |                                          |              |               |              |            |             |       |

| bit 6          | RX9: 9-bit Receive Enable bit<br>1 = Selects 9-bit reception<br>o = Selects 8-bit reception                                                                                                                                                            |                                          |              |               |              |            |             |       |

| bit 5          |                                                                                                                                                                                                                                                        | gle Receive                              | Enable bit   |               |              |            |             |       |

|                | Asynchron<br>Don't care                                                                                                                                                                                                                                | ous mode:                                |              |               |              |            |             |       |

|                | <u>Synchronous mode - master:</u><br>1 = Enables single receive<br>o = Disables single receive<br>This bit is cleared after reception is complete.                                                                                                     |                                          |              |               |              |            |             |       |

|                | <u>Synchrono</u><br>Don't care                                                                                                                                                                                                                         | us mode - s                              | lave:        |               |              |            |             |       |

| bit 4          | CREN: Cor                                                                                                                                                                                                                                              | ntinuous Re                              | ceive Enable | e bit         |              |            |             |       |

|                |                                                                                                                                                                                                                                                        | ous mode:<br>s continuou<br>es continuou |              |               |              |            |             |       |

|                |                                                                                                                                                                                                                                                        |                                          |              | til enable bi | t CREN is cl | eared (CRE | N overrides | SREN) |

| bit 3          | ADDEN: A                                                                                                                                                                                                                                               | ddress Dete                              | ect Enable b | it            |              |            |             |       |

|                | Asynchronous mode 9-bit (RX9 = 1):<br>1 = Enables address detection, enables interrupt and load of the receive buffer when<br>RSR<8> is set<br>a Rischlose address detection of butter are received, and pinth bit can be used as parity bit           |                                          |              |               |              |            |             |       |

| bit 2          | <ul> <li>o = Disables address detection, all bytes are received, and ninth bit can be used as parity bit</li> <li>FERR: Framing Error bit</li> <li>1 = Framing error (can be updated by reading RCREG register and receive next valid byte)</li> </ul> |                                          |              |               |              |            |             |       |

|                | o = No fran                                                                                                                                                                                                                                            |                                          |              |               |              |            |             |       |

| bit 1          | OERR: Overrun Error bit<br>1 = Overrun error (can be cleared by clearing bit CREN)<br>o = No overrun error                                                                                                                                             |                                          |              |               |              |            |             |       |

|                |                                                                                                                                                                                                                                                        |                                          |              |               |              |            |             |       |

#### Figure 22: RCSTA register bit specification

http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf

R/ T

The Heart of Medical Advances.

|       | R/W-0                          | R/W-0        | R/W-0        | R/W-0         | U-0    | R/W-0 | R-1  |  |

|-------|--------------------------------|--------------|--------------|---------------|--------|-------|------|--|

|       | CSRC                           | TX9          | TXEN         | SYNC          | —      | BRGH  | TRMT |  |

|       | bit 7                          |              |              |               |        |       |      |  |

|       |                                |              |              |               |        |       |      |  |

| bit 7 | CSRC: Clock                    | k Source Se  | lect bit     |               |        |       |      |  |

|       | Asynchronou                    | us mode:     |              |               |        |       |      |  |

|       | Don't care                     |              |              |               |        |       |      |  |

|       | Synchronous                    |              |              |               |        |       |      |  |

|       | 1 = Master n<br>o = Slave mo   |              |              |               | m BRG) |       |      |  |

| hit c |                                |              |              | source)       |        |       |      |  |

| bit 6 | TX9: 9-bit Tr<br>1 = Selects 9 |              |              |               |        |       |      |  |

|       | 0 = Selects 8                  |              |              |               |        |       |      |  |

| bit 5 | TXEN: Tran                     | smit Enable  | bit          |               |        |       |      |  |

|       | 1 = Transmit                   | enabled      |              |               |        |       |      |  |

|       | o = Transmit                   | disabled     |              |               |        |       |      |  |

|       | Note: SREN                     |              | ridoe TVEN   | in SVNC m     | odo    |       |      |  |

| bit 4 | SYNC: USA                      |              |              | III OTNO II   | ioue.  |       |      |  |

| 511.4 | 1 = Synchro                    |              | electoit     |               |        |       |      |  |

|       | o = Asynchro                   |              |              |               |        |       |      |  |

| bit 3 | Unimpleme                      | nted: Read   | as '0'       |               |        |       |      |  |

| bit 2 | BRGH: High                     | Baud Rate    | Select bit   |               |        |       |      |  |

|       | Asynchronou                    | us mode:     |              |               |        |       |      |  |

|       | 1 = High spe                   |              |              |               |        |       |      |  |

|       | o = Low spe                    |              |              |               |        |       |      |  |

|       | Synchronous                    |              |              |               |        |       |      |  |

|       | Unused in th                   |              |              |               |        |       |      |  |

| bit 1 | TRMT: Trans                    |              | gister Statu | s bit         |        |       |      |  |

|       | 1 = TSR emp<br>o = TSR full    | pty          |              |               |        |       |      |  |

| bit 0 |                                | t of Tranami | t Data aan   | ho pority bit |        |       |      |  |

| DILU  | TX9D: 9th bi                   | t or mansmi  | i Daia, can  | be parity bit |        |       |      |  |

|       |                                |              |              |               |        |       |      |  |

#### Figure 23: TXSTA register bit specification.

http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf

The BRG (Baud Rate Generator) supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer, in Asynchronous mode, bit BRGH (TXSTA<2>).

The most common data format for serial transmission is 8 bit. 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator.

We are setting up an Asynchronous Transmission, so the following steps should be taken:

1. Initialize the SPBRG register for the appropriate baud rate. To have a high speed baud rate we set bit BRGH.

2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

3. Set enable bit TXIE for interrupts.

4. Set transmit bit TX9, since we a 9-bit transmission is desired

5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

6. Load data to the TXREG register (starts transmission).

8. Ensure that GIE and PEIE (bits 7 and 6) of the INTCON register are set, interrupts will be used.

### 4.1.2 The Pearl Blue Bluetooth module

The technology that will be used to send wireless signal to user's cell phone will be Bluetooth technology. Bluetooth provides short range wireless communication and is widely available in computers, pocket PC's and cell phones nowadays.

The Bluetooth module that will be connected to the microcontroller will be The Pearl Blue Bluetooth module made by emxys<sup>TM</sup> Embedded Instruments. The module operates in the unlicensed ISM at 2.4 GHz using Frequency Hop Spread Spectrum to avoid interference. This device is a class 1 device which has the capability to reach up to 100 m with 20 dbm1. (Depending on the cell phone the user has the range will vary from 10 to 100 meters.)

The Pearl Blue Bluetooth module will act as the master to initiate connection with user's cell phone. Moreover it has a unique 48-bit address used as identification and definition of the two way device communication.

One of the main features of the Bluetooth module is that it has direct Bluetooth to serial interface which gets connected to the UART port of the microcontroller as shown in Figure 24.

Figure 24: The Pearl Blue Bluetooth module connection diagram

http://www.futurlec.com/PIC16F877\_Controller.shtml www.emxys.com/docs/PearlBlue\_Fact\_Sheet.pdf http://www.more-shop.co.uk/images/medium/mtom\_serial\_90\_com\_MED.png

Moreover the firmware allows us to specify the baud rate which will be 115k2. User's cell phones baud rate will be automatically adjusted by the J2ME program as described in programming strategy.

# 5. Physical Design

Table 5 summarizes the size of different parts which will be enclosed in PULZE<sup>TM</sup>. The dimensions are from the designed PCB board, Microcontroller and the Bluetooth module datasheet.

| Part             | Height (mm) | Width (mm) | Length (mm) |

|------------------|-------------|------------|-------------|

| Data Acquisition | 7           | 36         | 87          |

| Circuit          |             |            |             |

| Microcontroller  | 25          | 62         | 82          |

| Bluetooth        | 15          | 42         | 70          |

| Lithium Battery  | 17          | 26         | 49          |

• Note: The values have been rounded up.

In order to use the maximum space and to make the device as compact as possible, the box containing the parts should have the dimensions summarized in Table 6.

| Part             | Height (cm) | Width (cm) | Length (cm) |

|------------------|-------------|------------|-------------|

| Overall Physical | 3           | 11         | 16          |

| Design           |             |            |             |

• Note: Some part will be stacked on top of each other.

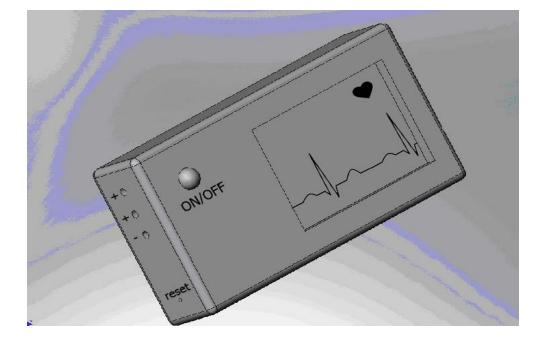

#### Figure 25

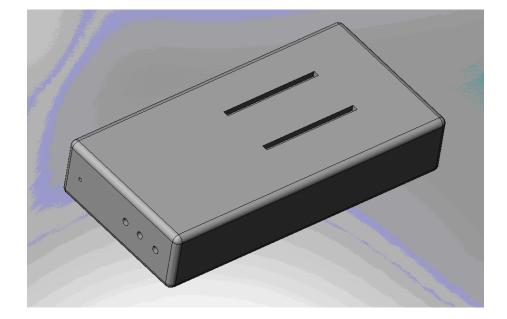

*Figure 25*: *Physical design of the system (front view)* represents a preliminary sketch of the front view of the device. Moreover the back view of the sketch is represented in Figure 26. The back part allows the user to attach the device to their belt for their convenient.

The Heart of Medical Advances.

Figure 25: Physical design of the system (front view)

The Heart of Medical Advances.

Figure 26: Physical design of the system (back view)

## 6. Software Design

#### 6.1 Programming Strategy

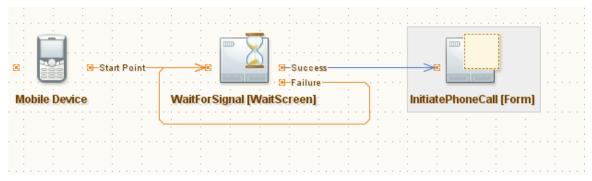

As mentioned in previous parts when a heart attack is detected, the microcontroller will send a signal to user's cell phone to initiate a call to the emergency personnel. The flow is presented in Figure 27.

Figure 27: J2ME cell phone application Flow Designer MIDP 2.0

In order to write the application for the cell phone we will use the NetBeans IDE version 5.5.1 with enabled NetBean Mobility Pack for CLDC. CLDC is a J2ME configuration designed for very small memory scenarios, typically 128 KB to 512 KB.

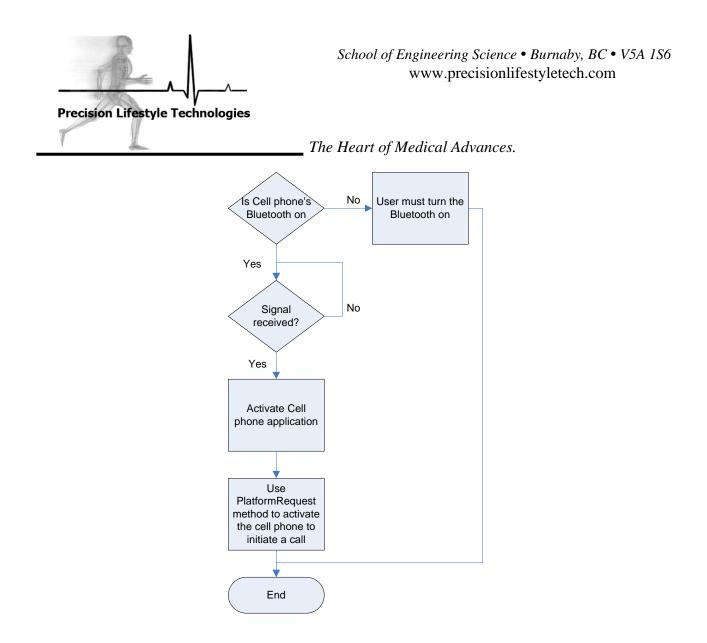

To initiate a phone call after the application has been activated by the Bluetooth signal, Public Class MIDlet will use PlatformRequest method, as fully specified in RFC2806 document [2] to initiate the phone call to the specified number. Then the platform interprets this as a request to initiate a voice call and will be passed to the Phone application to handle. The flow chart is presented in Figure 28.

Figure 28: Flow chart of cell phone application to initiate a call

Since using phone's application to make a voice call might have financial impact to the user (e.g. phones airtime), therefore the platform must ask user to explicitly acknowledge all requests at the time of installing the application on the cell phone.

# 7 Test Plan

In order to test the device we have planned the following steps:

- 1. Electrodes are to be tested individually. One electrode is tested individually to ensure its workability while avoiding interference from the neighboring electrodes.

- 2. Minimum distortion should be seen when increasing the number of electrodes used.

- 3. Signal is acquired and processed at the pre-amp and filtering module.

- 4. The pre-amp and filtering module will first take in only 1 input signal at a time.

- 5. After it is verified that all electrode signals can be obtained with minimal noise and distortion, all electrode signals will be multiplexed into the amplification and filtering module.

- 6. The signal is tested and that maximum gain is achieved without clamping the signal

- 7. A signal will be observed to ensure the output is expected.

- 8. Simulation and signal processing will be investigated using MATLAB. (second phase)

- 9. Signal display is obtained by MATLAB (second phase) and Oscilloscope.

- 10. Connections of all parts of the system will be checked.

- 11. The electrodes are placed on the one of group members' heart.

- 12. Using LabView the normal and un-normal (signal due to heart attack) can be generated. The generated signal can be outputted from the computer's sound card and be sent to the MC unit for analysis. If the un-normal signals are received by the MC, they will be detected.

#### Copyright © 2007 Precision Lifestyle Technologies Inc.

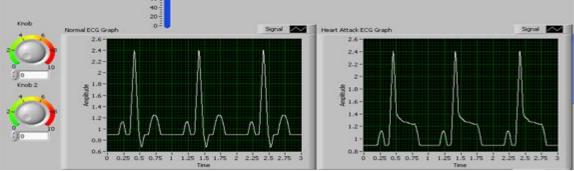

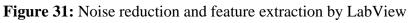

The ECG signals are generated using the arbitrary signal generator of LabView. The block diagram of the signal generation is presented in the Figure 29. The generated signals are presented in Figure 30.

13. In order to test the software, phone number of one of PLT's group members will be used instead of the emergency personnel to receive the phone call for help for the heart attack victim.

Figure 29: Block diagram of generating the regular and heart attack signal using LabView

Figure 30: Normal ECG signal (on the right) and a heart attack signal generated using LabView

#### 7.1 Proof of Concept Experiments

PULZE<sup>TM</sup> will undergo a series of development phases before it is commercialized. The device will not fulfill all the functional requirements as it is intended to serve as a proof-of-concept only. Once ST elevation of heart signal has been detected by the device, other acute heart attack signal characteristics will be evaluated by the device for the commercialized version. For example characteristics such as T wave inversion and Q wave depression.

## 8 Special feature and future work

The acquisition of heart signal by LabView via sound card of the computer is one of the possible enhancements to the device.

The advantages of this feature are:

- 1- The heart signal can be recorded for a long period of time.

- 2- The recorded data can be emailed.

3- Accurate signal processing by Advanced Signal Processing Toolkit (ASPT) and the Digital Filter Design Toolkit (DFDT)

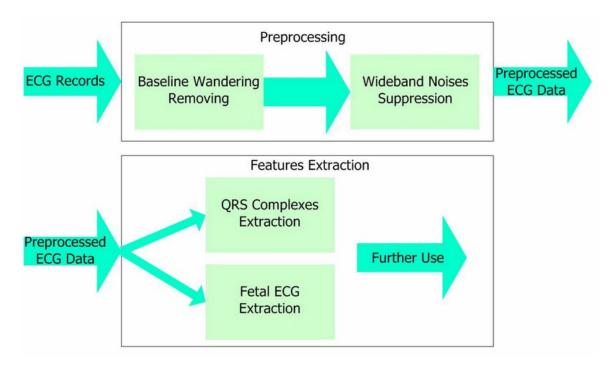

Preprocessing ECG signals will improve the system by eliminating the following:

- power line interference

- electrode pop or contact noise

- patient–electrode motion artifacts

- electromyography (EMG) noise

- baseline wandering noise[2]

Figure 31 represents the preprocessing and feature extraction using LabView.

www.ni.com

The power line interference (60 Hz noise) and the wandering noise have the most negative effect on ECG signal. By using a notch filter the mentioned noises can be eliminated. On the other hand, baseline wandering and wideband noises can not be easily eliminated by an analog circuit; therefore Digital filtering is a very desirable feature.

We plan to detect more types of heart attack and cardiovascular diseases by doing complex signal processing. This can be done by using smarter and more expensive microcontrollers such as speedy 33 which is capable of using LabView graphical program instead of assembly and C programming language. One of the advantages of using LabView program is the ability to use DSP Module, which is a library containing signals processing nodes. Power spectrums of the normal and abnormal ECG signal as well as regular and abnormal signals are presented in the Figure 32.

Figure 32: Power spectrums of the normal and abnormal ECG signal generated by LabView

## 9 Conclusion

The proposed design solutions of the PULZE<sup>TM</sup> have been discussed in this document, which provides guidelines to meet the functional specification. On the other hand, proposed design solutions will be adjusted accordingly to fully meet the functional specification. The test plan will ensure the functionalities of the device are tested and fully functional. Moreover successful prototyping of the device will depend on the validity of the proposed design, which is planed to be completed by January 1, 2008.

## **10 References**

- [1]www.americanheart.org/presenter.jhtml

- [2] www.ietf.org/rfc/rfc2806.txt

- [3] www.ni.com

[4] Embedded Computing with PIC16F877 -Assembly Language Approach (Vols 1 & 2) *A complete guided project book for PIC students* by Charles Kim, Ph.D.

- [5] www.istockPhoto.com

- [6] www.microchip.com, PIC16F877 datasheet

- [7] www.emxys.com, The Pearl Blue Bluetooth Module Getting Started Manual

- [8] www.mobileinfo.com/Bluetooth/FAQ.htm#t1

- [9] www.datasheetcatalog.com

- [10] http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf

- [11] http://www.widenclinic.com/images/human\_figure.gif

- [12] http://zone.ni.com/devzone/cda/tut/p/id/6361

- [13] http://www.vanth.org/vibes/images/normalECG2.PNG

- [14] http://apps.uwhealth.org/health/adam/graphics/images/en/8772.jpg

- [15] http://abhishek.tiwari.com/wp-content/uploads/2007/07/red\_cross.png

- [16] www.datasheetcatalog.com/datasheets\_pdf/A/D/6/2/AD620.shtml

- [17] http://www.gshop.com.au/images/ide\_133\_cable.jpg

- [18] www.emxys.com/docs/PearlBlue\_Fact\_Sheet.pdf

- [19] http://www.futurlec.com/PIC16F877\_Controller.shtml

- [20] http://www.more-shop.co.uk/images/medium/mtom\_serial\_90\_com\_MED.png

- [21] http://abhishek.tiwari.com/wp-content/uploads/2007/07/red\_cross.png

- [22] http://www.vanth.org/vibes/images/normalECG2.PNG

- [23] www.wpclipart.com/telephone/antenna.png

- [24] www.datasheetcatalog.com/datasheets\_pdf/A/D/6/2/AD620.shtml

- [25] www.datasheetcatalog.com/datasheets\_pdf/I/N/A/1/INA128.shtml

- [26] http://www.futurlec.com/PIC16F877\_Controller.shtml

- [27] http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf

- [28] http://www.futurlec.com/PIC16F877\_Controller.shtml

- [29] www.emxys.com/docs/PearlBlue\_Fact\_Sheet.pdf

- [30] http://www.more-shop.co.uk/images/medium/mtom\_serial\_90\_com\_MED.png

The Heart of Medical Advances.

## **11 Appendices**

#### Appendix I: Pins descriptions and layout of Microcontroller PIC16F877

| Pin | Pin Name    | Description                                     |

|-----|-------------|-------------------------------------------------|

| #   |             |                                                 |

| 1   | ~MCLR       |                                                 |

| 2   | RA0/AN0     | PORTA.0 /Analog Channel 0                       |

| 3   | RA1/AN1     | PORTA.1 /Analog Channel 1                       |

| 4   | RA2/AN2     | PORTA.2 /Analog Channel 2                       |

| 5   | RA3/AN3     | PORTA.3 /Analog Channel 3                       |

| 6   | RA4/T0CK1   | PORTA.4 / External Clock for Timer 0            |

| 7   | RA5/AN4     | PORTA.5 /Analog Channel 4                       |

| 8   | RE0/AN5     | PORTE.0 /Analog Channel 5                       |

| 9   | RE1/AN6     | PORTE.1 /Analog Channel 6                       |

| 10  | RE2/AN7     | PORTE.2 /Analog Channel 7                       |

| 11  | Vdd         | $+3 \sim +5V$                                   |

| 12  | Vss         | GND                                             |

| 13  | OSC1/CLKIN  | Oscillator Connection /Clock In                 |

| 14  | OSC2/CLKOUT | Oscillator Connection / Clock Out               |

| 15  | RC0/T1CK1   | PORTC.0 /External Clock for Timer 1             |

| 16  | RC1/CCP2    | PORTC.1 /CCP2                                   |

| 17  | RC2/CCP1    | PORTC.2 /CCP1                                   |

| 18  | RC3/SCK/SCL | PORTC.3 /SCK(for SPI)/SCL(for I <sup>2</sup> C) |

| 19  | RD0         | PORTD.0                                         |

| 20  | RD1         | PORTD.1                                         |

The Heart of Medical Advances.

| Pin Name    | Description                                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | _                                                                                                                                                                                 |

| RD2         | PORTD.2                                                                                                                                                                           |

| RD3         | PORTD.3                                                                                                                                                                           |

| RC4/SDI/SDA | PORTC.4/SDI(for SPI)/SDA(for I <sup>2</sup> C)                                                                                                                                    |

| RC5/SDO     | PORTC.5 /SDO (for SPI)                                                                                                                                                            |

| RC6/TX      | PORTC.6 /TX (for Serial Com.)                                                                                                                                                     |

| RC7/RX      | PORTC.7 /RX (for Serial Com.)                                                                                                                                                     |

| RD4         | PORTD.4                                                                                                                                                                           |

| RD5         | PORTD.5                                                                                                                                                                           |

| RD6         | PORTD.6                                                                                                                                                                           |

| RD7         | PORTD.7                                                                                                                                                                           |

| Vss         | GND                                                                                                                                                                               |

| Vdd         | $+3 V \sim +5 V$                                                                                                                                                                  |

| RB0/INT     | PORTB.0/External Interrupt                                                                                                                                                        |

| RB1         | PORTB.1                                                                                                                                                                           |

| RB2/PGM     | PORTB.2 /Programming Input                                                                                                                                                        |

| RB3         | PORTB.3                                                                                                                                                                           |

| RB4         | PORTB.4                                                                                                                                                                           |

| RB5         | PORTB.5                                                                                                                                                                           |

| RB6/PGC     | PORTB.6 /Debugger/ICSP                                                                                                                                                            |

| RB7/PGD     | PORTB.7 /Debugger/ICSP                                                                                                                                                            |

|             | RD2<br>RD3<br>RC4/SDI/SDA<br>RC5/SDO<br>RC6/TX<br>RC7/RX<br>RD4<br>RD5<br>RD6<br>RD7<br>Vss<br>Vdd<br>RB0/INT<br>RB1<br>RB0/INT<br>RB1<br>RB2/PGM<br>RB3<br>RB4<br>RB5<br>RB6/PGC |

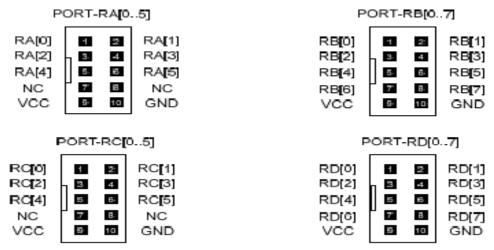

#### Appendix II: Description of PIC16F877 Microcontroller board pin layout

http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf

- **1-**Power Supply port

- 2-Microcontroller PIC 40 PIN or PIC16F877

- **3-** Signal Port I/O of PIC MCU PORT-RB

- 4- Signal Port I/O of PIC MCU PORT-RD

- 5- Signal Port I/O of PIC MCU PORT-RC

- 6- Signal Port I/O of PIC MCU PORT-RA

http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf

7- PORT RS232 and be arranged as following

8-PIN PORTE

http://ww1.microchip.com/downloads/en/DeviceDoc/30292c.pdf

9- JUMPER for using PIC MCU. There are 2 modes;

- 16F is Microcontroller 40 PIN No. PIC16F877

- 18F is Microcontroller 40 PIN No. PIC18F458

- **10-** PORT for download program

- **11-** iLED Power

- 12- Reset switch

- 13- Power Supply port to be used with board ET-BASIC I/O