#### National Library of Canada

Bibliothèque nationale du Canada

Service des thèses canadiennes

Canadian Theses Service

Ottawa, Canada K1A 0N4

### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of eproduction possible.

pages are missing, contact the university which granted he degree.

some pages may have indistinct print especially if the riginal pages were typed with a poor typewriter ribbon or the university sent us an inferior photocopy.

leproduction in full or in part of this microform is governed y the Canadian Copyright Act, R.S.C. 1970, c. C-30, and ubsequent amendments. AVIS

• •

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséguents.

### VLSI-Based Hypermesh Interconnection Networks for Array Processing

by

Masoud Rostam Kafhesh

B.Sc., Sharif University of Technology, 1986

### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE-REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

in the School

of

Computing Science

© Masoud Rostam Kafhesh 1989 SIMON FRASER UNIVERSITY July 1989

All rights reserved. This thesis may not be reproduced in whole or in part, by photocopy or other means, without the permission of the author. KIA ON4

Service des thèses canadiennes

Canadian Theses Service

Ottawa, Canada

The author has granted an irrevocable nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-59355-5

Canadä

### Approval

Name:

Masoud Rostam Kafhesh

Degree: Master of Science

Title of Thesis:

VLSI-Based Hypermesh Interconnection Networks for Array Processing

**Examining Committee:**

Dr. Warren Burton, Chairman

÷ \*

Dr. Rick Hobson Director and Associate Professor Senior Supervisor

Dr. Ramesh Krishnamurti Assistant Professor Supervisor

Dr. Art Liestman Associate Professor External Examiner

July 24, 1989

Date Approved

i

### PAGINATION ERROR.

TEXT COMPLETE.

NATIONAL LIBRARY OF CANADA.

CANADIAN THESES SERVICE.

х.

ERREUR DE PAGINATION.

LE TEXTE EST COMPLET.

BIBLIOTHEQUE NATIONALE DU CANADA. SERVICE DES THESES CANADIENNES.

### PARTIAL COPYRIGHT LICENSE

I hereby grant to Simon Fraser University the right to lend my thesis, project or extended essay (the title of which is shown below) to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its users. I further agree that permission for multiple copying of this work for scholarly purposes may be granted by me or the Dean of Graduate Studies. It is understood that copying or publication of this work for financial gain shall not be allowed without my written permission.

#### Title of Thesis/Project/Extended Essay

i.

| ased Hypermesh Inter                  | connection Ne                               | <u>tworks for Array</u>                        | Processing.                     |

|---------------------------------------|---------------------------------------------|------------------------------------------------|---------------------------------|

|                                       | <b>.</b> 5                                  |                                                |                                 |

|                                       |                                             |                                                |                                 |

|                                       |                                             |                                                |                                 |

|                                       |                                             | •                                              |                                 |

| · · · · · · · · · · · · · · · · · · · |                                             |                                                |                                 |

|                                       |                                             |                                                | 3                               |

|                                       | -<br>esh                                    |                                                |                                 |

| (name)                                | · · · · · · · · · · · · · · · · · · ·       |                                                |                                 |

| July 27, 198                          | 9                                           |                                                |                                 |

|                                       | (signature)<br>Masoud Rostam Kafh<br>(name) | (signature)<br>Masoud Rostam Kafhesh<br>(name) | Masoud Rostam Kafhesh<br>(name) |

### Abstract

Given the clear and pressing need for improved computer system performance, there are several means of achieving this end. In the simplest approach, current computer architectures are reimplemented using faster technologies. Although this approach will always be exploited, physical, technological, and economic limitations make it incapable of providing all the needed computational power.

Instead, *parallelism* must be exploited to obtain truly significant performance improvements. Parallelism is a two dimensional problem. Along one dimension we find pure data parallelism as might be found in typical array algorithms involving vectors and matrices. Along the other dimension we find concurrency where independent processes work on facets of an algorithm which may not lend themselves to array processing. Assuming the use of the fastest reasonable technology, any further increase in performance requires the efficient exploitation of parallelism in one form or another.

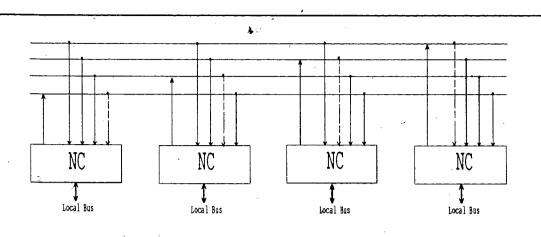

The performance of computers can be made incrementally extensible by exploiting VLSI technology to build concurrent/parallel computers, ensembles of processing nodes connected by a network. Low latency communication elements are required to support fine-grain or medium-grain parallel computation. Communication between nodes of a multicomputer need not be slower than the communication between the processor and memory of a conventional computer. A VLSI-Based network controller can provide node-to-node communication times that approach main memory access times of sequential computers. A VLSI chip is subject to several technological constraints. Whenever each node of a multicomputer system is implemented as a VLSI chip or a printed circuit board, packaging constraints limit the number of connections that can be made available for communication links. Some key issues which must be considered when designing a high performance network controller based on VLSI technology are also discussed.

New variations on the 2-d mesh interconnection computer which can be implemented

iii

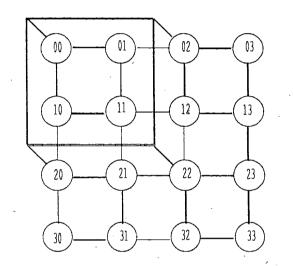

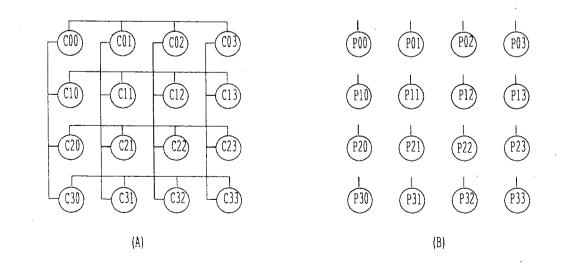

very efficiently using VLSI technology for chips and packaging are proposed. Direct connectivity along rows and columns reduces the diameter of an nxn 2-d mesh from 2n-2 to 2. This technique permits the network communication bandwidth to be more balanced (or uniform) with the node processor data bus bandwidth. Simulation studies on several important permutation and matrix algorithms show that direct connectivity in hypermesh highly simplifies algorithm design and supports very efficient communication patterns.

### To my parents

ζ. . . . . .

•

•

### Acknowledgements

I would like to thank my supervisor, Dr. Rick Hobson, for his guidance throughout my research and development of this thesis and also for the financial support in the forms of research assistantships.

The VLSI lab and all its enthusiastic members provided a very inspiring work environment. John Simmons for helping me and his support deserves special mention. Many of my colleagues in computing science were very helpful. Garnik Haftevani and Ranabir Gupta deserve many thanks.

I would also like to acknowledge the School of Computing Science and Simon Fraser University financial assistance in the forms of teaching assistantships and a Graduate Fellowship.

v

## Table of Contents

| Approval                                                         | ·4 ·    | i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |

|------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Abstract                                                         |         | iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ·<br>· |

| Acknowledgements                                                 |         | <b>.</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| Table of Contents                                                |         | vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | · 1    |

| 1. Introduction                                                  |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | , ·    |

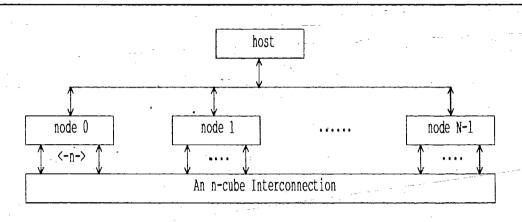

| 1.1. Multicomputer Networks: A Definition                        |         | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2      |

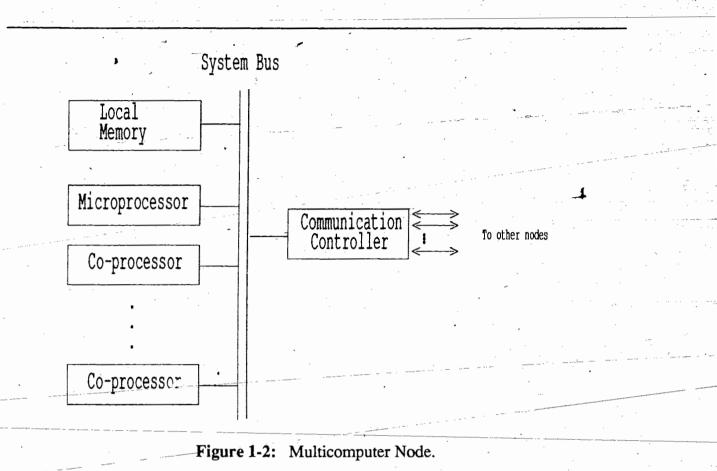

| 1.2. Multicomputers Building Blocks                              |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4      |

| 1.3. VLSI Constraints                                            |         | · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 5    |

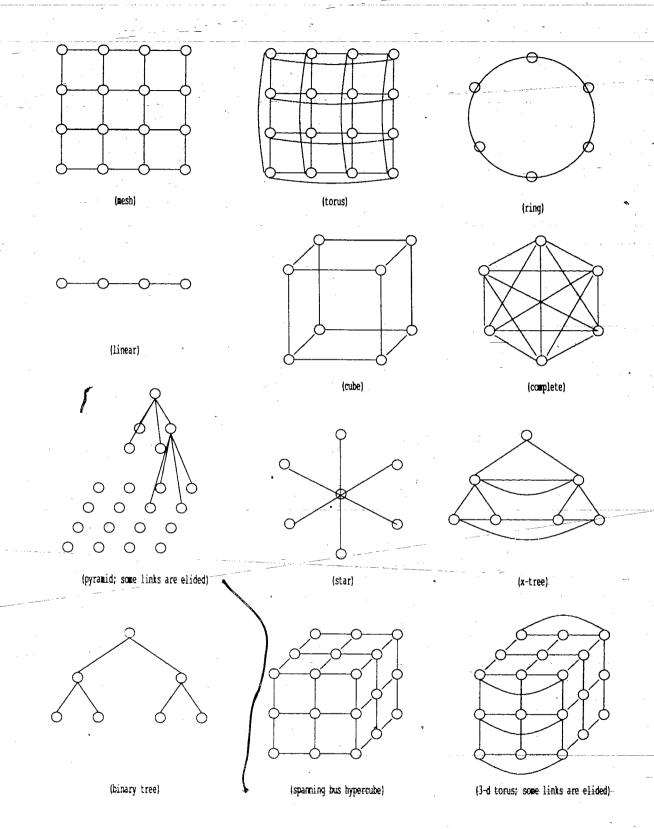

| 1.4. Interconnection Networks                                    |         | · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6      |

| 1.5. Multicomputer Programming                                   |         | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6      |

| 1.6. Thesis Objectives                                           |         | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8      |

| 2. Architectural Features and Design Considerations of Hypermesh | Multico | mputers for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |

| Array Processing                                                 |         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| 2.1. Issues in Designing Parallel Machines                       |         | <ul> <li>And the second se</li></ul> | 11     |

| 2.1.1. General versus Fixed Communication:                       | •       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12     |

| 2.1.2. Fine Grained versus Coarse Grained                        |         | · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12     |

| 2.1.3. Multiple versus Single Instruction Stream                 | ·       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13     |

| 2.2. The Communication Network                                   | ·       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14-    |

| 2.2.1. Choosing a Topology                                       | 1. A.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • 14   |

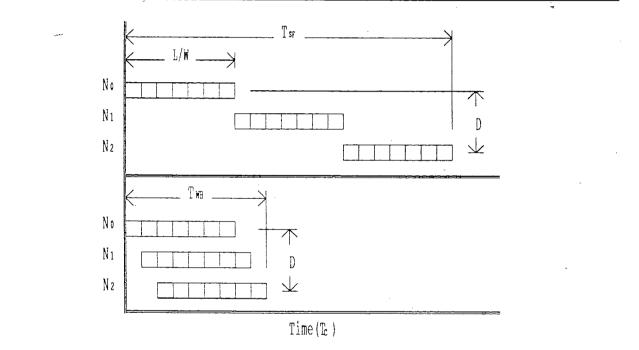

| 2.2.2. Choosing a Routing Strategy and Mechanism                 |         | · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16     |

| 2.3. Enhancements on Mesh Structure                              |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18     |

| 2.4. Proposed Network Structure                                  |         | · •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20     |

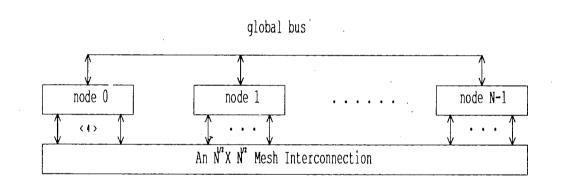

| 2.4.1. The Architecture                                          |         | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21     |

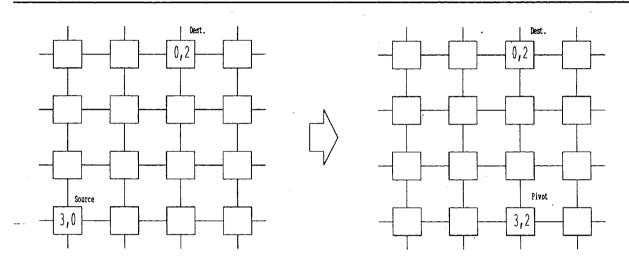

| 2.4.2. Routing Scheme in Hypermesh                               | F       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22     |

| 2.4.3. Characteristics of Hypermesh                              |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25     |

| 2.5. Characterizing the Computational Power of the Hypermes      | sh      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26     |

| 2.5.1. Hypermesh vs. Regular Mesh                                |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26     |

| 2.5.2. Hypermesh vs. mesh with single broadcasting               |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 27     |

| 2.5.3. Hypermesh vs. mesh with multiple broadcasting             |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 28     |

| 2.5.4. Hypermesh versus Fully Connected Network                  |         | • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29     |

| 2.5.5. Divide and Conquer Strategy                               |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29     |

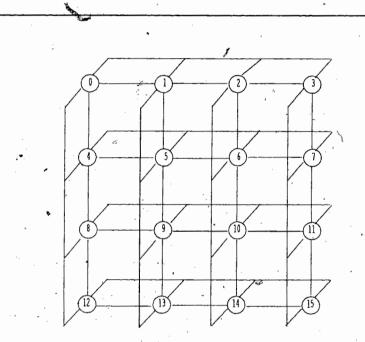

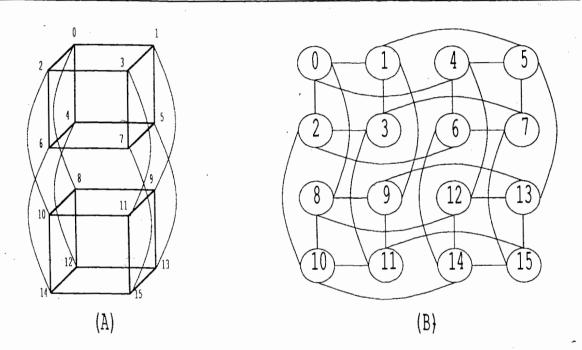

| 2.6. Symmetry and Embedding                                      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30     |