# Abstracting OpenCL for Multi-Application Workloads on CPU-FPGA Clusters

by

### Graham Mark Holland

B.A.Sc. (Hons.), Simon Fraser University, 2014

Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Master of Applied Science

> in the School of Engineering Science Faculty of Applied Sciences

© Graham Mark Holland 2019 SIMON FRASER UNIVERSITY Fall 2019

Copyright in this work rests with the author. Please ensure that any reproduction or re-use is done in accordance with the relevant national copyright legislation.

## Approval

Name: Graham Mark Holland

Degree: Master of Applied Science (Engineering)

Title: Abstracting OpenCL for Multi-Application

Workloads on CPU-FPGA Clusters

Examining Committee: Chair: Anita Tino

Lecturer

Lesley Shannon

Senior Supervisor

${\bf Professor}$

Zhenman Fang

Supervisor

Assistant Professor

Arrvindh Shriraman

Internal Examiner Associate Professor

School of Computing Science

Date Defended: December 3, 2019

## Abstract

Field-programmable gate arrays (FPGAs) continue to see integration in data centres, where customized hardware accelerators provide improved performance for cloud workloads. However, existing programming models for such environments typically require a manual assignment of application tasks between CPUs and FPGA-based accelerators. Furthermore, coordinating the execution of tasks from multiple applications necessitates the use of a higher-level cluster management system. In this thesis, we present an abstraction model named CFUSE (Cluster Front-end USEr framework), which abstracts the execution target within a heterogeneous cluster. CFUSE allows tasks from multiple applications from unknown workloads to be mapped dynamically to the available CPU and FPGA resources and allows accelerator sharing among applications. We demonstrate CFUSE with an OpenCL-based prototype implementation for a small cluster of Xilinx FPGA development boards. Using this cluster, we execute a variety of multi-application workloads to evaluate three scheduling policies and to determine the relevant scheduling factors for the system.

**Keywords:** Field-programmable gate arrays; runtime task scheduling; OpenCL; hardware acceleration; FPGA clusters

## Acknowledgements

Completing this thesis would not have been possible without the help and support of many people. Firstly, I would like to thank my graduate supervisor, Dr. Lesley Shannon, for the wealth of advice and guidance she has given me and for always having faith in my abilities. Thanks to my family and friends for their encouragement and to the members of the Reconfigurable Computing Lab, thanks for the thoughtful discussions and good company.

To my wife Jennifer, thank you for always believing in me. You have kept me focused on my goals and have been the person I could turn to whenever I needed help. I would not have been able to finish this without you.

# Table of Contents

| <b>A</b>         | ppro       | val                    |                                            | ii           |  |  |

|------------------|------------|------------------------|--------------------------------------------|--------------|--|--|

| A                | bstra      | ıct                    |                                            | iii          |  |  |

| Acknowledgements |            |                        |                                            | iv           |  |  |

| Ta               | able       | of Con                 | tents                                      | $\mathbf{v}$ |  |  |

| Li               | st of      | Table                  | S                                          | viii         |  |  |

| Li               | st of      | Figur                  | es                                         | ix           |  |  |

| Li               | st of      | Listin                 | ${f gs}$                                   | x            |  |  |

| Li               | st of      | Acron                  | ıyms                                       | xi           |  |  |

| $\mathbf{G}$     | lossa      | $\mathbf{r}\mathbf{y}$ |                                            | xiii         |  |  |

| 1                | Inti       | $\mathbf{coduct}$      | ion                                        | 1            |  |  |

|                  | 1.1        | Motiva                 | ation                                      | 2            |  |  |

|                  | 1.2        | Object                 | tive                                       | 3            |  |  |

|                  | 1.3        | Contri                 | ibutions                                   | 4            |  |  |

|                  | 1.4        | Thesis                 | S Organization                             | 4            |  |  |

| 2                | Background |                        |                                            |              |  |  |

|                  | 2.1        | Field-                 | Programmable Gate Arrays                   | 6            |  |  |

|                  |            | 2.1.1                  | Architecture                               | 6            |  |  |

|                  |            | 2.1.2                  | Synthesis, Programming and Reconfiguration | 7            |  |  |

|                  | 2.2        | Open(                  | CL                                         | 9            |  |  |

|                  |            | 2.2.1                  | OpenCL Models                              | 9            |  |  |

|                  |            | 2.2.2                  | Typical OpenCL Host Application Flow       | 11           |  |  |

|                  |            | 2.2.3                  | OpenCL FPGA Implementations                | 13           |  |  |

|                  | 2.3        | Amda                   | hl's Law                                   | 14           |  |  |

|                  | 2.4        | Relate                 | ed Work                                    | 14           |  |  |

|   |                                            | 2.4.1  | POCL                                                   | 4 |  |  |  |

|---|--------------------------------------------|--------|--------------------------------------------------------|---|--|--|--|

|   |                                            | 2.4.2  | FUSE                                                   | 5 |  |  |  |

|   |                                            | 2.4.3  | Task Scheduling in Heterogeneous Systems               | 6 |  |  |  |

|   |                                            | 2.4.4  | Resource Managers for Clusters and Distributed Systems | 7 |  |  |  |

|   |                                            | 2.4.5  | FPGAs in the Data Centre                               | 8 |  |  |  |

|   |                                            | 2.4.6  | OpenCL for FPGAs                                       | 9 |  |  |  |

| 3 | The                                        | CFUS   | SE Framework 2                                         | 1 |  |  |  |

|   | 3.1                                        | Backgr | round                                                  | 1 |  |  |  |

|   | 3.2                                        | Execut | tion Model                                             | 2 |  |  |  |

|   | 3.3                                        | Overvi | ${ m ew}$                                              | 3 |  |  |  |

|   | 3.4                                        | Compo  | onent Details                                          | 4 |  |  |  |

|   |                                            | 3.4.1  | Proxy                                                  | 4 |  |  |  |

|   |                                            | 3.4.2  | Resource Manager                                       | 4 |  |  |  |

|   |                                            | 3.4.3  | Kernel Scheduler                                       | 5 |  |  |  |

|   |                                            | 3.4.4  | Request Handler                                        | 5 |  |  |  |

|   |                                            | 3.4.5  | Runtime Library                                        | 5 |  |  |  |

| 4 | CF                                         | USE P  | rototype Implementation 2                              | 6 |  |  |  |

|   | 4.1                                        | Cluste | r Hardware                                             | 6 |  |  |  |

|   |                                            | 4.1.1  | Zynq-7000 System-on-Chip                               | 8 |  |  |  |

|   | 4.2                                        | Hardw  | rare Accelerators                                      | 8 |  |  |  |

|   |                                            | 4.2.1  | Accelerator Operation                                  | ( |  |  |  |

|   | 4.3                                        | Softwa | re Runtime Components                                  | 1 |  |  |  |

|   |                                            | 4.3.1  | Hardware Accelerator Device Driver                     | 1 |  |  |  |

|   |                                            | 4.3.2  | DMA Buffer Module                                      | 1 |  |  |  |

|   |                                            | 4.3.3  | CFUSE Daemons                                          | 3 |  |  |  |

|   |                                            | 4.3.4  | Runtime Library                                        | 5 |  |  |  |

|   | 4.4                                        | Hardw  | are and Software Build Automation                      |   |  |  |  |

| 5 | Experimental Framework Characterization 37 |        |                                                        |   |  |  |  |

|   | 5.1                                        | Low O  | verhead Interval Timer                                 | 7 |  |  |  |

|   |                                            | 5.1.1  | Timer Read Procedure                                   | 8 |  |  |  |

|   |                                            | 5.1.2  | Timer Accuracy Characterization                        | 8 |  |  |  |

|   | 5.2                                        | CFUS   | E Daemon Instrumentation                               | C |  |  |  |

|   | 5.3                                        | Data   | Transfer Characterization                              | 1 |  |  |  |

|   | 5.4                                        | DMA    | Buffer Overhead                                        | 3 |  |  |  |

| 6 | Exp                                        | erime  | ntal Results and Discussion 4                          | 5 |  |  |  |

|   | 6.1                                        | Bench  | mark Applications                                      |   |  |  |  |

|   |                                            |        |                                                        |   |  |  |  |

|              |       | 6.1.1  | 3D Rendering                       | 46 |

|--------------|-------|--------|------------------------------------|----|

|              |       | 6.1.2  | Digit Recognition                  | 47 |

|              |       | 6.1.3  | Face Detection                     | 47 |

|              |       | 6.1.4  | Spam Filter                        | 47 |

|              |       | 6.1.5  | CPU Kernel Conversion Process      | 48 |

|              |       | 6.1.6  | Benchmark Hardware Accelerators    | 50 |

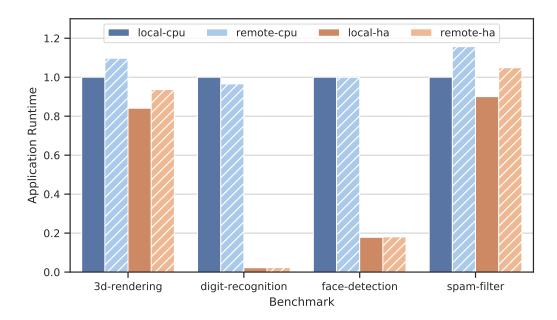

|              | 6.2   | Baseli | ne Kernel Performance              | 51 |

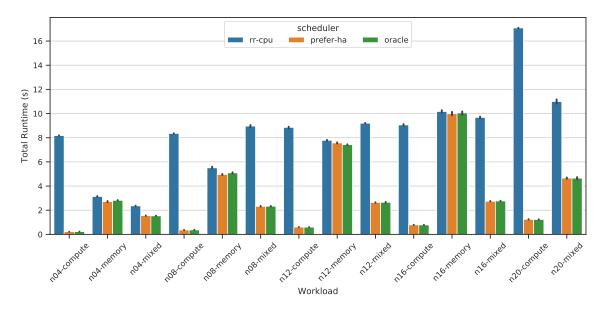

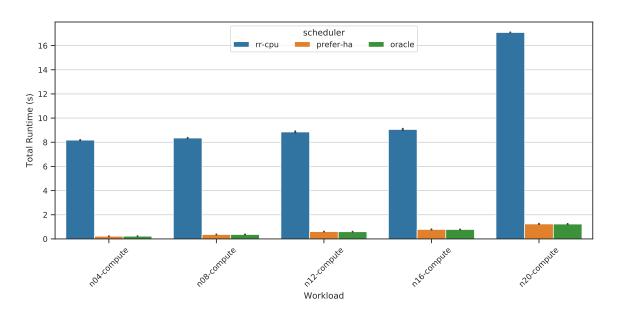

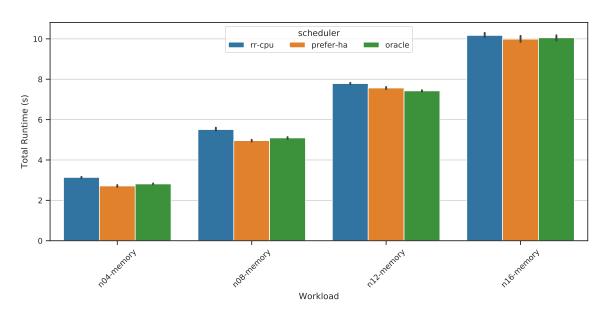

|              | 6.3   | Sched  | uler Policies                      | 54 |

|              |       | 6.3.1  | Round-Robin CPU-only Policy        | 54 |

|              |       | 6.3.2  | Prefer Hardware Accelerator Policy | 54 |

|              |       | 6.3.3  | Oracle Policy                      | 55 |

|              | 6.4   | Workl  | oad Experiments                    | 56 |

|              |       | 6.4.1  | FPGA Configurations                | 57 |

|              |       | 6.4.2  | Workload Results and Discussion    | 57 |

| 7            | Cor   | clusio | ns and Future Work                 | 62 |

|              | 7.1   | Conclu | usions                             | 62 |

|              | 7.2   | Future | e Work                             | 62 |

| $\mathbf{R}$ | efere | nces   |                                    | 64 |

| $\mathbf{A}$ | ppen  | dix A  | OpenCL Application Example         | 69 |

|              | A.1   | openc  | l_example.c                        | 69 |

|              | Δ 2   | wecto  | r add cl                           | 72 |

# List of Tables

| Table 5.1    | Interval timer overhead statistics                             | 39 |

|--------------|----------------------------------------------------------------|----|

| Table 6.1    | Rosetta benchmark application summary                          | 46 |

| Table 6.2    | C++ and OpenCL C language differences and resolutions          | 49 |

| Table 6.3    | Rosetta benchmark kernel CPU runtimes                          | 49 |

| Table 6.4    | Comparison of object code for Rosetta benchmark CPU kernels $$ | 50 |

| Table 6.5    | Total system resource usage                                    | 51 |

| Table 6.6    | Accelerator resource usage                                     | 51 |

| Table 6.7    | System infrastructure (interconnect and reset) resource usage  | 51 |

| Table 6.8    | 3d-rendering runtime breakdown on each target device           | 53 |

| Table 6.9    | digit-recognition runtime breakdown on each target device      | 53 |

| Table $6.10$ | face-detection runtime breakdown on each target device type    | 53 |

| Table 6.11   | spam-filter runtime breakdown on each target device type       | 54 |

| Table $6.12$ | Summary of benchmark application workloads                     | 56 |

| Table 6.13   | Hardware accelerator instances within each FPGA configuration  | 57 |

# List of Figures

| Figure 2.1 | Simplified FPGA architecture                                       | 7  |

|------------|--------------------------------------------------------------------|----|

| Figure 2.2 | FPGA CAD tool flow                                                 | 8  |

| Figure 2.3 | OpenCL platform and memory models                                  | 10 |

| Figure 2.4 | OpenCL kernel compilation                                          | 11 |

| Figure 2.5 | Typical OpenCL host application program flow                       | 12 |

| Figure 2.6 | FUSE thread creation and scheduling                                | 15 |

| Figure 3.1 | OpenCL and CFUSE execution models                                  | 22 |

| Figure 3.2 | CFUSE runtime system overview                                      | 23 |

| Figure 4.1 | CFUSE prototype target platform                                    | 27 |

| Figure 4.2 | Zynq-7000 device block diagram                                     | 27 |

| Figure 4.3 | CFUSE hardware accelerator architecture                            | 29 |

| Figure 4.4 | Overview of the CFUSE runtime prototype implementation             | 32 |

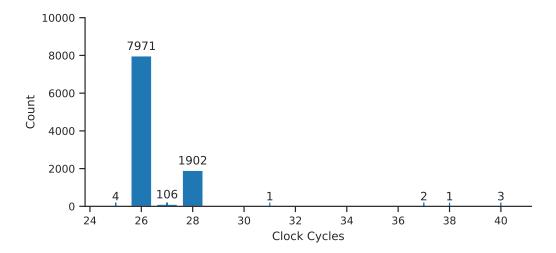

| Figure 5.1 | Histogram of interval timer overhead                               | 39 |

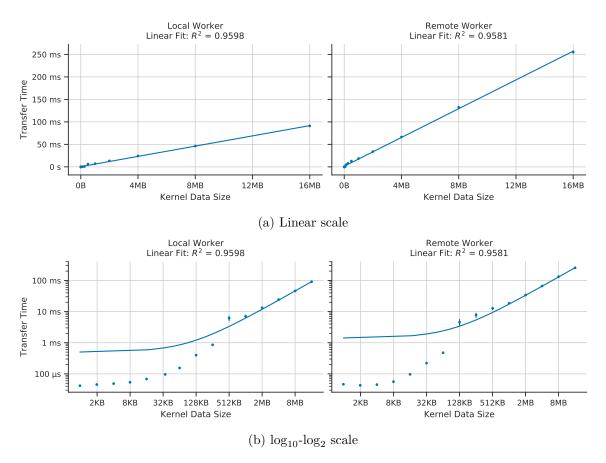

| Figure 5.2 | Kernel data transfer time with linear regression                   | 42 |

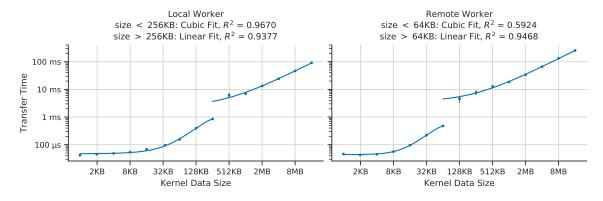

| Figure 5.3 | Kernel data transfer time with segmented regression                | 42 |

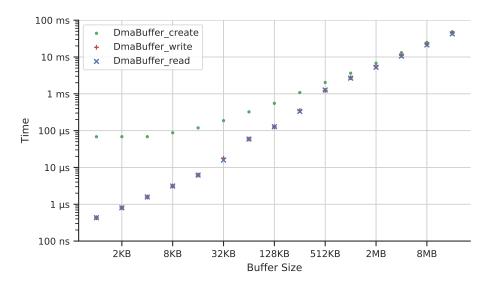

| Figure 5.4 | DMA buffer overheads                                               | 43 |

| Figure 6.1 | Total benchmark application runtime on each target type            | 52 |

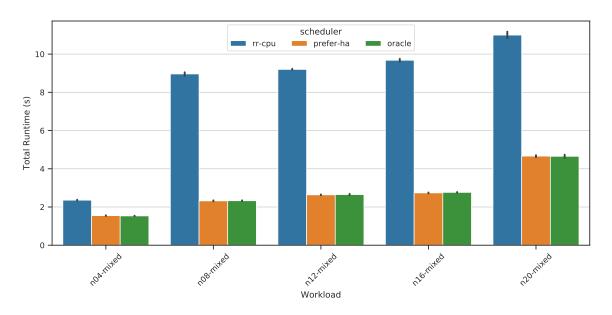

| Figure 6.2 | Total execution time per workload                                  | 58 |

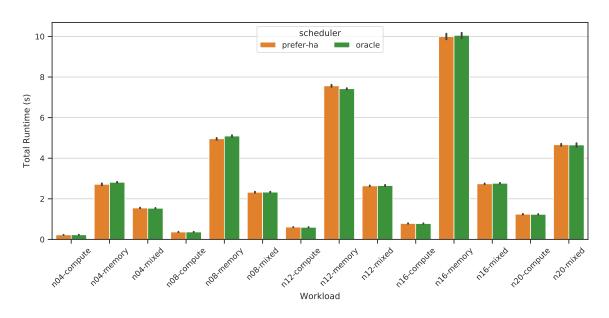

| Figure 6.3 | Total execution time of compute workloads                          | 59 |

| Figure 6.4 | Total execution time of memory workloads                           | 59 |

| Figure 6.5 | Total execution time of mixed workloads                            | 60 |

| Figure 6.6 | Total execution time per workload: Prefer-HA and Oracle schedulers |    |

|            | only                                                               | 60 |

# List of Listings

| Listing 5.1 | Global Timer read procedure           | 38 |

|-------------|---------------------------------------|----|

| Listing 5.2 | Interval timer benchmarking procedure | 38 |

## List of Acronyms

ACP Accelerator Coherency Port

**API** application programming interface

APU Application Processor Unit

AWS Amazon Web Services

AXI Advanced eXtensible Interface

**BRAM** block RAM

CAD computer-aided design

CFUSE Cluster Front-end USEr framework

CMA Contiguous Memory Allocator

CPU central processing unit

DAG directed acyclic graph

DMA direct memory access

**DSP** digital signal processing

EC2 Elastic Compute Cloud

FF flip-flop

FPGA field-programmable gate array

**FPU** floating-point unit

FUSE Front-end USEr framework

**GP** General Purpose

GPU graphics processing unit

**HDL** hardware description language

**HLS** high-level synthesis

${f HP}$  High Performance

IOMMU I/O memory management unit

IP Intellectual Property

JIT just-in-time

JNI Java Native Interface

JVM Java Virtual Machine

**LKM** loadable kernel module

**LUT** lookup table

MPI Message Passing Interface

MPSoC multiprocessor system-on-chip

**OS** operating system

PaaS Platform as a Service

**PCIe** PCI Express

**PL** Programmable Logic

POCL Portable Computing Language

POSIX Portable Operating System Interface

**PS** Processing System

RTL register-transfer level

SCU Snoop Control Unit

SIMD single instruction multiple data

SoC system-on-chip

## Glossary

- **behavioural synthesis** The process within the FPGA CAD tool flow in which a circuit description at the register-transfer level is transformed into a netlist of gates.

- bitstream Configuration data that is loaded onto an FPGA allowing the FPGA to implement custom digital logic.

- **compute unit** OpenCL devices are logically divided into compute units, which contain processing elements and local memory.

- data-parallel programming model An OpenCL programming model involving kernel instructions that operate on a memory object for points in an NDRange index space.

- **device** A compute resource capable of executing a *kernel* function using an appropriate binary. Examples include CPU cores, GPUs and FPGA fabric.

- high-level synthesis The process in which a circuit description at the register-transfer level is generated from an algorithm description in a high-level programming language such as C, C++ or OpenCL C.

- **kernel** A software-defined function marked for acceleration on an OpenCL device. Unrelated to an operating system kernel.

- **NDRange** A one-, two- or three-dimensional index space that defines a grouping of workitems and that must be specified when a OpenCL kernel is submitted for execution.

- **platform** An OpenCL platform consists of a host processor and one or more devices.

- **processing element** A compute unit within an OpenCL device is logically divided into processing elements, which execute work-items.

- task-parallel programming model An OpenCL programming model involving single work-item kernels executing concurrently without the need for an NDRange index space.

**work-group** A collection of related *work-items*, executed by a *compute unit. Work-items* within a group share local memory.

$\mathbf{work\text{-}item}$  One of a group of parallel kernel execution instances.

## Chapter 1

## Introduction

For many years, data centres have consisted of racks of networked server systems featuring general-purpose processors. However, the end of Dennard scaling in the previous decade has meant that power consumption is now the limiting factor for single-threaded central processing unit (CPU) performance improvements. This limitation is particularly problematic for the data centre, where client applications demand continuous, efficient scaling, and where data centre operators seek to curb growing power costs.

As a result, data centre server systems now feature customized hardware, such as graphics processing units (GPUs) and field-programmable gate arrays (FPGAs), to offload some computation from the CPU. These devices are capable of achieving improved performance over CPUs for certain workload types due to their massively parallel architectures. However, high-end GPUs typically have high power requirements, which can be problematic for deployment in a power-constrained data centre [1].

To address the power concerns with GPUs, cloud providers have begun to deploy reconfigurable hardware, such as Amazon making FPGAs available on their Amazon Web Services (AWS) Elastic Compute Cloud (EC2) F1 instances. [2]. These deployments have been driven by research showing that reconfigurable hardware has the potential to significantly improve the throughput of cloud applications [3]. However, the integration of such reconfigurable hardware into cloud environments brings with it a large and diverse set of challenges. Among these are issues related to the following topics:

**programmability** Addressing the lack of portability of FPGA configurations (bitstreams) between different devices, and between different partial reconfiguration regions within a device.

synthesis Providing abstractions to allow software-based definitions of hardware accelerators and associated hardware system infrastructure. Addressing the long compile times for FPGA platforms.

hardware-software integration Managing hardware accelerator use from software applications.

resource management Managing the availability of all execution resources (e.g. CPUs, hardware accelerators) and managing device reconfiguration to enable different sets of hardware accelerators.

scheduling Enabling efficient use of the compute resources available in the cluster by choosing a sequence for task execution via the use of specific scheduling algorithms.

**security** Ensuring that client applications are sufficiently isolated from one another when they share resources during execution.

**reliability** Ensuring robustness in the presence of errors, including hardware failures on compute nodes as well as network errors.

In this thesis, we address a subset of the hardware-software integration, resource management and scheduling challenges. We develop an abstraction model for execution targets within a network cluster. Our abstraction allows tasks from multiple applications to be dynamically scheduled for execution on either a CPU and FPGA accelerator, without requiring an explicit mapping from the programmer. We provide a demonstration of our abstraction by leveraging an existing high-level synthesis (HLS) tool to generate FPGA hardware accelerators from software descriptions. These accelerators are integrated into a cluster with compute nodes featuring both CPUs and FPGA hardware.

#### 1.1 Motivation

From a programming perspective, FPGAs have historically been utilized by describing computations at the register-transfer level (RTL) with hardware description languages (HDLs). Subsequently, this has generally limited their use to hardware engineers with a background in digital systems design. Advances in high-level synthesis (HLS) tools have helped to raise the level of FPGA design entry toward more traditional software programming languages including C and C++. Researchers and industry continue to work to close the performance gap between HLS-generated designs and hand-optimized RTL. As a result, the hardware-specific knowledge required to create performant systems with reconfigurable hardware is decreasing, making FPGA-based systems more accessible to non-experts.

At the same time, OpenCL has emerged as a popular and effective framework for unifying the programming of heterogeneous systems, including those featuring FPGAs. Using the functionality provided by the OpenCL host application programming interface (API), programmers schedule software-defined kernel functions for accelerated execution onto the devices available in a given platform. In the case of OpenCL implementations targeting FPGAs, HLS tools are used to generate custom hardware accelerators from OpenCL kernel source code.

A large amount of prior research work has sought to overcome the challenge of effectively using FPGA accelerators from within application programs. Among these is the Front-end

USEr framework (FUSE) [4]. FUSE presents a Platform as a Service (PaaS) model for hardware accelerators, by providing a programming interface analogous to software threads. Using FUSE, a developer models application compute tasks as threads, without specifying whether these tasks will be executed by a CPU core or an FPGA-based hardware accelerator. Instead, the tasks are allocated to an appropriate target by the FUSE runtime, which tracks hardware accelerator availability and uses execution via software as a fallback mechanism. In our work, we seek to adapt this central concept of FUSE for use within a cluster.

### 1.2 Objective

The primary objective of this work is to create a framework allowing for the execution of kernel functions from multiple applications across CPUs and FPGA-based hardware accelerators within a networked cluster. We wish to provide an abstraction of the available devices in the cluster, by automating the selection of an appropriate execution target for each application kernel. To meet this requirement, we will base the work on the underlying concept of the FUSE project.

Beyond extending the concept of FUSE to a CPU-FPGA cluster, we will also address some of the limitations of the original FUSE implementation. These include supporting multi-core processor platforms, adding direct memory access (DMA) capability for accelerators, and automating accelerator generation via HLS tools.

While the original FUSE implementation used Portable Operating System Interface (POSIX) threads, our framework demonstration will be based on OpenCL in order to leverage existing HLS capability. This also allows our framework to maintain a level of compatibility with the familiar OpenCL execution model, in which kernels are submitted to device command queues for execution. Furthermore, this allows existing OpenCL applications to be modified to use the new framework with less developer effort.

While OpenCL implementations targeting FPGAs, such as Xilinx SDAccel [5] and Intel FPGA SDK for OpenCL [6], have enabled a more accessible, software-driven approach for defining hardware accelerators and scheduling accelerator tasks, there are limitations inherent to the OpenCL models. In the course of implementing our framework, we seek to address a subset of the following limitations:

- Typical OpenCL implementations for FPGA platforms do not use the system processor for executing kernels. Instead, all kernels are executed by FPGA hardware accelerators, while the system processor executes the OpenCL runtime library.

- While OpenCL defines a portable kernel programming language, kernel performance between different device targets can vary substantially. To achieve sufficient performance, kernel code must often exploit device-specific features.

- The runtime library implementation of the OpenCL host API limits the view of system resources, making simultaneous use of devices by multiple applications difficult.

- The OpenCL platform model is restricted to a single network node. There is no method available to utilize devices on remote nodes.

- OpenCL is a low-level framework. The application programmer is responsible for managing device work queues and moving kernel data between the host processor and devices.

#### 1.3 Contributions

The contributions of this thesis can be summarized as follows:

- The Cluster Front-end USEr framework (CFUSE): an abstraction model allowing for the dynamic mapping of tasks from multiple applications to CPU and FPGA hardware accelerators within a network cluster of heterogeneous nodes.

- A demonstration of CFUSE using an OpenCL-based framework prototype.

- An initial analysis of the scheduling performance within the framework using sets of benchmark application workloads.

The CFUSE framework presented in this thesis, raises the abstraction level over the OpenCL execution model by applying the FUSE concept to a cluster of CPU-FPGA nodes. It leverages the Xilinx Vivado HLS tool [7] to create hardware accelerators from kernel source code and provides a simplified mechanism for constructing heterogeneous CPU-FPGA systems with these accelerators. CFUSE utilizes the Portable Computing Language (POCL) [8] OpenCL implementation to enable application kernels to execute on CPU targets in addition to FPGA accelerators.

We present a prototype implementation of CFUSE on a small network cluster of Xilinx Zynq FPGA development boards and perform a series of characterization experiments to investigate the framework overhead. Finally, we perform an analysis of the scheduling capability of the framework to uncover the factors relevant to determining an execution schedule for kernels from a mix of benchmark applications.

### 1.4 Thesis Organization

This thesis is organized in the following manner. Chapter 2 presents relevant background information on FPGAs, the OpenCL framework and its models, and presents a summary of related research including the prior work of FUSE. Chapter 3 provides a high-level overview of the CFUSE framework, while the implementation details of the prototype are covered

in Chapter 4. Chapter 5 describes measurement techniques and presents a characterization of the prototype CFUSE implementation. We present the results of our investigations on scheduler policies for benchmark application workloads in Chapter 6. Finally, Chapter 7 summarizes the work, outlines areas for future research effort, and lists potential system improvements to CFUSE.

## Chapter 2

## Background

This chapter provides relevant background information about the technologies, hardware devices, software tools and frameworks used in this thesis. We begin with a discussion of field-programmable gate array (FPGA) architecture, synthesis and programming and then move on to discuss the OpenCL framework and OpenCL platforms supporting FPGAs. We provide an overview of two previous works that we make use of in this thesis: the Portable Computing Language (POCL) OpenCL implementation and the Front-end USEr framework (FUSE). Finally, we present an overview of related research.

### 2.1 Field-Programmable Gate Arrays

FPGAs are hardware reconfigurable integrated circuits, capable of implementing custom digital logic designs. In the following sections, we discuss their internal architecture and the computer-aided design (CAD) tool flow used to create a custom configuration from a circuit design specification. After this, we describe the device configuration process.

#### 2.1.1 Architecture

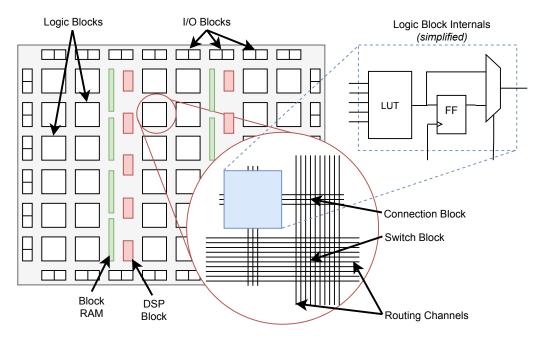

Figure 2.1 shows a simplified model of a modern FPGA architecture. As shown, FPGAs are made up of a programmable fabric, consisting of an array of *logic blocks* that implement circuit functions, connected by a *programmable interconnect*. *I/O blocks* are used to interface with the physical device pins and are capable of implementing various digital I/O standards and voltages.

Logic blocks differ between FPGA vendor and device family, but at a minimum contain a lookup table (LUT), flip-flop (FF) and multiplexer. LUTs may be programmed with arbitrary Boolean functions to implement combinational circuits. With the addition of flip-flops to the logic block, sequential circuits such as registers and distributed memories can also be implemented. Modern FPGA architectures feature significantly more complicated logic blocks than what is shown here. They may include structures allowing for the implementation of shift registers and distributed RAM, as well as a carry chain used to efficiently

Figure 2.1: Simplified FPGA architecture

implement arithmetic functions. Furthermore, modern architectures use fracturable LUTs that can either implement a single k-input LUT or two (k-1)-input LUTs with shared inputs.

The interconnect consists of routing tracks organized into horizontal and vertical *chan-nels*, used for routing signals between logic blocks. Logic blocks connect to this interconnect at a *connection block* and connections are made between intersecting channels at *switch blocks*. Connection and switch blocks contain programmable switches, allowing for arbitrary connections to be made by loading an FPGA configuration, known as a bitstream.

In addition to these configurable blocks, the FPGA fabric also includes various fixed logic blocks, used to implement functionality common to many classes of digital circuits. These include embedded memories known as block RAMs (BRAMs), digital signal processing (DSP) blocks for performing multiply-accumulate operations, analog-to-digital converters, high speed I/O blocks, such as PCI Express (PCIe) and DDR memory interfaces, and dedicated clock circuitry. Some FPGAs also contain embedded central processing unit (CPU) cores with a set of interfaces enabling communication to the remainder of the programmable fabric.

#### 2.1.2 Synthesis, Programming and Reconfiguration

Due to the size and complexity of the circuits that may be implemented on a modern FPGA, designers typically use hardware description languages (HDLs), such as VHDL and Verilog, to specify their designs. These languages describe circuits at the register-transfer level (RTL). Given a set of HDL design files, a CAD tool is used to synthesize a bitstream. This

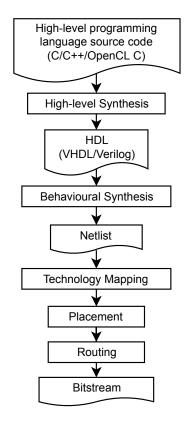

Figure 2.2: FPGA CAD tool flow

process involves the following steps, outlined in Figure 2.2: behavioural synthesis, technology mapping, placement and routing. In behavioural synthesis, RTL sources are transformed into a netlist, a generic circuit representation consisting of logic gates and connections. Device independent circuit optimizations may then be performed using this representation. These gates are then packed into the primitives (LUTs, flip-flops, BRAMs, DSP blocks etc.) available on the target FPGA device during technology mapping. During placement, specific locations are chosen for each element and these elements are wired together during the routing stage.

High-level synthesis (HLS) is the process of generating RTL code for hardware synthesis from a higher level programming language such as C, C++ or OpenCL C. Increasingly, FPGA-based design is performed using HLS tools. Such tools are useful to those without extensive knowledge of digital circuit design and RTL-based design entry. Advances in HLS optimization have brought the resulting circuit performance closer to what would be generated from hand-optimized RTL.

Once a bitstream is generated using HLS or from RTL sources, it must be programmed onto the FPGA for the device to implement the circuits in the design. This is typically done when the device is initially powered on, but may also be performed during runtime. Some FPGAs support dynamic partial reconfiguration, whereby a subset of the FPGA fabric may

be reconfigured, while the circuits in the remaining regions of the fabric continue to operate. To achieve this, the designer must use floorplanning CAD software to divide the device into partially reconfigurable and static regions. Then, multiple partial bitstreams are generated for the partially reconfigurable region as well as a bitstream for the static part of the design. These partial bitstreams are generally not portable between different partial reconfiguration regions.

### 2.2 OpenCL

OpenCL (Open Computing Language) [9] has begun to see widespread use for developing programs targeting heterogeneous systems, including those featuring graphics processing units (GPUs) and FPGAs. The OpenCL standard defines an application programming interface (API), implemented via a runtime library, and a portable, parallel programming language called OpenCL C. An OpenCL platform consists of a host processor that executes the runtime library and application code, and one or more computation devices. Devices execute specially qualified functions called kernels that are written in the OpenCL C language. Examples of such devices include multi-core CPUs, discrete GPUs, FPGAs and DSP chips.

#### 2.2.1 OpenCL Models

The OpenCL specification divides the OpenCL architecture into a hierarchy of four models:

- Platform model Divides the system into a host processor and devices.

- Execution model Defines the use of device command queues to control kernel execution.

- Memory model Defines memory regions and memory access rules for host applications and kernels.

- Programming model Defines the data-parallel and task-parallel models.

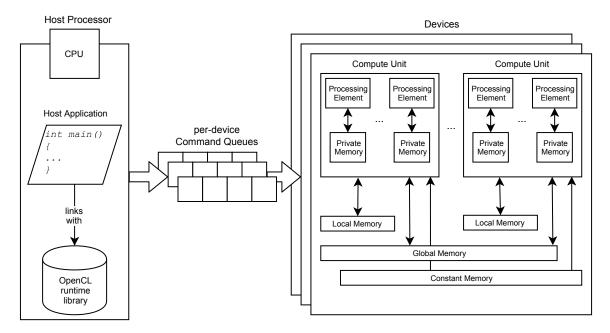

The platform model divides a system into a *host processor* and one or more compute *devices*. Devices are further divided into *compute units* that are themselves made up of *processing elements*. It is important to note that these divisions are logical abstractions and how a given device is subdivided into these components is defined by the specific implementation of OpenCL on a system. It is valid for a device to consist of a single compute unit with a single processing element.

The execution model logically divides application program execution. Kernels execute on devices, while the OpenCL API implementation and remaining application code execute on the host processor. All device interactions, including memory transfers between the

Figure 2.3: OpenCL platform and memory models

host processor and device as well as kernel executions, occur by submitting commands to a *command queue* data structure. A command queue is mapped to a specific device. Kernel invocations are defined over an index space called an *NDRange*, with a single kernel invocation being executed for each point in this index space. These kernel instances are called *work-items*, which are organized into *work-groups*. Each processing element executes a work-item, while each compute unit executes a work-group.

The memory model divides system memory into regions. *Global* and *constant* memories are accessible to both the host and device, while *local* and *private* memories are accessible only to work-groups and work-items respectively.

Finally, OpenCL distinguishes between two possible programming models: data-parallel and task-parallel. The data-parallel programming model involves kernel instructions operating concurrently on the elements of a memory object for points in an index space, with one point for each work-item. This model represents a single instruction multiple data (SIMD) approach to parallelism. Alternately, the task-parallel programming model uses single work-item kernels that execute without the need for an index space. In the task-parallel case, parallelism can be achieved by using vector data types or by enqueuing multiple kernels for concurrent execution. If supported by the specific OpenCL implementation, OpenCL extensions may be used via pragmas in kernel source code for device-specific optimizations such as loop unrolling and pipelining.

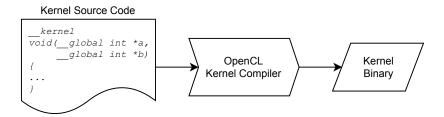

An OpenCL implementation is provided by a vendor and consists of both an OpenCL runtime library and a kernel compiler. The runtime library is an implementation of each function from the OpenCL C host API. This is provided as a shared object library. The

kernel compiler is used to generate device-specific kernel binaries from OpenCL C source code.

Figure 2.4: OpenCL kernel compilation. Kernel source code is compiled to a device-specific binary format either offline or during application runtime via the OpenCL host API.

### 2.2.2 Typical OpenCL Host Application Flow

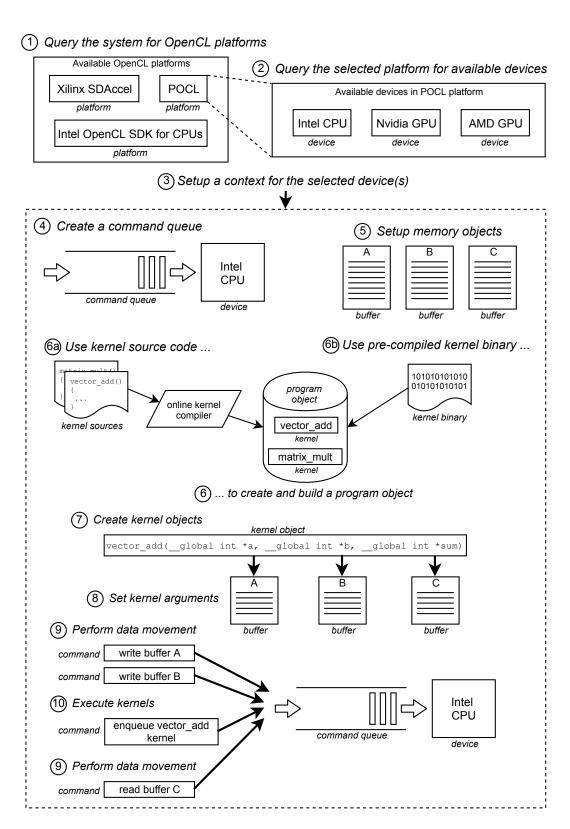

A typical OpenCL application will perform a number of steps to define kernel tasks, setup memory buffers, perform data transfers between the host processor and a device and finally launch kernels to be executed on a device. Host applications primarily interact with OpenCL devices via command queue objects. The application submits commands to device-specific queues to manage data within host and device memory and to launch kernels. The act of submitting a command generates an event object, which may be used to synchronize subsequent commands via an event wait list. Using events in this manner allows the programmer to specify dependencies between commands. Figure 2.5 outlines the primary actions taken by an OpenCL host application during its execution. These steps are as follows:

- 1. Query the system for OpenCL platforms. The OpenCL standard allows multiple platforms (OpenCL vendor implementations) to co-exist on a system. The host API provides functions to query the system for the available platforms and discover their capabilities.

- 2. Query the selected platform for available devices. Once a platform has been selected, the application will query the platform for a list of available compute devices. The application may also check device properties.

- 3. Setup a context for the selected device(s). An OpenCL context includes one or more devices and encapsulates other OpenCL objects: command queues, memory buffers, programs and kernels. These objects cannot be shared between contexts.

- 4. Create a command queue. In order to launch kernels on a device, a command queue must be created. Command queue objects are specific to a single device and context.

- 5. Setup memory objects. OpenCL buffers are specified as one-dimensional collections of elements and are used to specify input and output arguments to kernels. Buffer objects are specific to a context.

Figure 2.5: Typical OpenCL host application program flow

- 6. Create and build program objects. An OpenCL program object consists of a set of kernels, which are functions written in OpenCL C source code and identified with the \_\_kernel attribute. Program objects may be created from either (a) OpenCL C source code by using the vendor-supplied kernel compiler at application runtime or (b) from a prebuilt binary image generated prior to execution.

- 7. Create kernel objects. A kernel object encapsulates a specific \_\_kernel function that exists within a program object along with the argument values to be used during execution.

- 8. Set kernel arguments. Memory objects and plain data types are passed as arguments to a kernel function using the clSetKernelArgument function.

- 9. Perform data movement. Operations on memory buffers to move data between host and device memory are specified by submitting commands to the command queue.

The OpenCL host API defines a number of command-enqueuing functions for performing different memory operations. As with all command-enqueuing functions, the application can use event objects to specify dependencies between commands.

- 10. Execute kernels. Kernels are executed by calling the clEnqueueNDRangeKernel function and specifying a device command queue and a kernel object. This function also requires the specification of an N-dimensional index space (NDRange) on which to operate.

An NDRange is used to divide a kernel invocation into instances called work-items that are organized into work-groups. The OpenCL execution model views a device as being made up of one or more compute units, each containing one or more processing elements. Each compute unit of a device executes a work-group and each processing element within the compute unit executes a single work-item.

The source code for an example host application and corresponding kernel function is provided in Appendix A for reference.

### 2.2.3 OpenCL FPGA Implementations

FPGAs are fundamentally different from the more typical CPU and GPU OpenCL device types since their underlying architecture allows for the realization of custom hardware to implement kernel functions. Since kernel compilation for FPGAs involves the synthesis of kernel cores and bitstream generation, compilation times are orders of magnitude longer than for a CPU or GPU. Therefore, offline compilation must be used to create kernel binaries rather than performing compilation during application runtime. Furthermore, the OpenCL data-parallel programming model, while well suited for massively parallel devices such as GPUs, does not necessarily map well to FPGA hardware [10]. Instead, performance gains

on FPGA hardware are typically achieved through HLS-specific optimization techniques such as array partitioning, loop unrolling and pipelining [11] [12]. For this reason, kernels are usually written to use only a single work-item, therefore following the task-parallel programming model [13].

#### 2.3 Amdahl's Law

Amdahl's Law [14] is commonly used to estimate the potential speedup for parallel programs. However, it can also be used to determine the theoretical speedup for serial programs, where some portion of the program can be optimized or accelerated. With this formulation, the equation for program speedup is given in Equation 2.1.

$$Speedup = \frac{1}{(1-p) + \frac{p}{s}} \tag{2.1}$$

The theoretical speedup of the entire program is a function of p, the proportion of the original execution time that benefits from acceleration and s, the speedup of the accelerated portion.

### 2.4 Related Work

In this section, we discuss background and related work from academia, industry and the open source software community.

#### 2.4.1 POCL

Portable Computing Language (POCL) [8] is an open source implementation of the OpenCL standard, providing a portable OpenCL runtime library implementation and a kernel compiler. The POCL kernel compiler utilizes Clang [15] as a front end for OpenCL C code and LLVM [16] for optimization and code generation to binary formats for different device targets. One of the goals of the POCL project is to make it easy to add support for new devices. This is made possible by having their implementation of the OpenCL runtime library make calls to an intermediary device support API. POCL provides an implementation of this device API for a generic pthread CPU target that maps kernel work-items to Portable Operating System Interface (POSIX) threads. Furthermore, the LLVM-based compiler back end for the pthread device supports both online and offline use, as POCL defines a custom binary format for CPU kernels containing object code and kernel metadata. This allows POCL to be used on embedded platforms, which may not be able to host the complete kernel compiler.

#### 2.4.2 FUSE

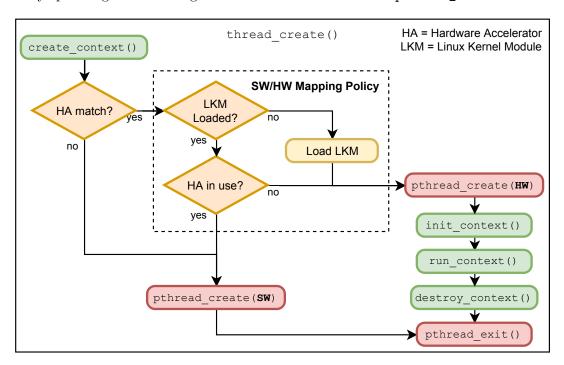

This work is based on the Front-end USEr framework (FUSE) architecture [4]. FUSE is a framework for abstracting the use of FPGA hardware accelerators. The concept of the FUSE architecture is to allow computation tasks to be executed either as software on a CPU or using an FPGA hardware accelerator, without an explicit choice being specified in the application source code. The decision on where to execute a computation task is made during application runtime by the FUSE scheduling policy and carried out by the mechanisms of the FUSE library. This architecture abstracts the use of hardware accelerators from the application programmer.

The implementation of the FUSE system uses the POSIX thread (pthread) library as the underlying model for describing computations. The programmer defines pthread functions to be used for CPU execution. Hardware accelerators providing the same functionality as their software counterparts are also required, along with a driver implemented as a Linux kernel module. A kernel table that maps thread functions to equivalent hardware accelerators is used by the FUSE scheduler when deciding where to execute a computation task.

A task is scheduled for execution by calling the FUSE library thread\_create function. An overview of the implementation of the thread\_create function is shown in Figure 2.6. The implementation is as follows. If a matching hardware accelerator is found and is not in use, FUSE loads the Linux kernel module driver for that accelerator (if necessary) and launches the task on the accelerator. Otherwise, the task is scheduled for execution on the CPU by spawning the matching software thread with a call to pthread\_create.

Figure 2.6: FUSE thread creation and scheduling. Adapted from [4].

Some limitations of the FUSE system implementation include the following:

- The target platform is an FPGA development board with a single-core soft processor and accelerators implemented in the FPGA fabric.

- There is no integration with HLS tools. Therefore, there is no means to generate hardware accelerators from software functions.

- Each hardware accelerator requires the development of a custom driver, implemented as a Linux kernel module.

- There is no support for accelerators to use direct memory access (DMA) operations. Data is transferred to accelerators using register accesses via the driver ioctl or mmap functions.

### 2.4.3 Task Scheduling in Heterogeneous Systems

Scheduling computation tasks onto the resources available within a heterogeneous system is a widely studied research area. Here we focus our discussion on prior work that utilizes OpenCL and OpenCL-like models.

Taylor et al. [17] develop a method for mapping kernels onto the ARM big.LITTLE mobile platform, a heterogeneous multicore architecture that combines small power efficient cores with larger high performance cores. They use an offline model, trained on OpenCL kernel features, that selects which processor and clock frequency to use for each kernel invocation. Their model performs a trade-off between kernel runtime and power consumption. The approach relies on a just-in-time (JIT) compilation of unseen kernels as they are submitted for execution.

Perina and Bonato [18] extract features from OpenCL code and use a machine learning framework to statically decide between GPU and FPGA accelerators based on estimated energy consumption. They use generic OpenCL kernel benchmarks without FPGA specific optimizations.

MultiCL [19] augments the OpenCL context and command queue objects with scheduling properties. These are used as hints to a runtime system that manages a pool of all device command queues. Their scheduler utilizes device and kernel profiling techniques that are possible only on devices that support online kernel compilation such as GPUs. Further, they restrict the scope of scheduling to kernels within a single application.

A number of related works extend the scope of kernel scheduling to multiple OpenCL applications. Wen et al. [20] use potential speedup as a heuristic for scheduling kernels from multiple applications onto a CPU or GPU. They use machine learning to train a predictor of performance speedup using features extracted from a static kernel code analysis. Their goal is to optimize throughput and application turnaround time. Unlike some other related work,

they do not split up kernel tasks, which they define as kernel executions plus associated data transfer.

Conversely, FluidiCL [21] splits kernel executions at the work-group level and enables cooperative kernel execution by CPU and GPU. It manages the extra data transfers to devices automatically and merges the partial results computed by each device. Unlike the work of Wen et al. it does not require an offline training step.

HeteroPDP [22] predicts performance degradation due to memory contention of colocated OpenCL and system applications. The model is based on regressions of performance characterization data and is capable of selecting between CPU and GPU execution within a single platform.

#### 2.4.4 Resource Managers for Clusters and Distributed Systems

A number of previous research projects have looked at enabling OpenCL for use in distributed systems, but only for clusters featuring GPUs. SnuCL [23] makes OpenCL devices on remote nodes available to the local OpenCL context and automatically manages data movement between nodes. However, the programmer must still manually determine the target for each kernel. Similarly, Hybrid OpenCL [24], dOpenCL [25] and Distributed OpenCL [26] all share in common the need to use separate buffers for each device and manually map kernels to devices.

Conversely, DistCL [27] abstracts the locality of the remote GPUs as well, treating all the cluster GPUs as a single device. The DistCL runtime requires that the programmer write kernel meta-functions that specify the memory access patterns of each kernel. These meta-functions are used to determine how kernel executions should be split and to assign work-items to devices while minimizing remote data transfers.

CloudCL [28] utilizes dOpenCL, and therefore also requires manual splitting of kernels, but adds a two-tier scheduler to maintain fairness among multiple executing kernels. The first tier schedules kernels without knowledge of the cluster or the kernel splitting and the second schedules to specific GPU devices using a policy based on recorded kernel performance history.

These distributed OpenCL works (SnuCL, Hybrid OpenCL, dOpenCL, Distributed OpenCL, DistCL and CloudCL) solve a related but distinctly different problem to ours. All of these works make remote devices available to a single OpenCL host application and split kernel tasks among the available devices. We do not split kernel tasks among devices, as we schedule kernels from multiple applications that execute concurrently. Furthermore, we provide an abstraction of the execution target type, by automatically selecting between a CPU or FPGA hardware accelerator at runtime.

The libwater [29] project also aims to ease development for heterogeneous clusters featuring GPUs. It provides a simplified library wrapper over the OpenCL host API and implements a device query language for selecting targets among the many potentially avail-

able within a cluster. Notably, the libwater runtime builds a directed acyclic graph (DAG) of commands as they are submitted, based on the dependencies between commands that are specified using event objects. In their initial work, the DAG is used to recognize individual point-to-point communications between nodes, so that they may be replaced with more efficient collective operations. Similarly to our work, kernels are not split over multiple devices. However, our framework abstracts execution targets for kernels as the runtime provides automatic device selection. With libwater, selecting an execution target for each kernel must be performed manually using the provided device query language.

In addition to the distributed OpenCL works, are a variety of commercial and open source cluster resource managers including TORQUE [30] and SLURM [31]. These resource managers are designed to enable batch processing of applications on large clusters. SLURM allocates cluster resources to user applications, provides a means for starting and monitoring work on these compute resources and also manages contention for shared resources using a work queue. The fundamental resource that can be allocated by SLURM is a compute node. Our work takes a more fine-grained approach to application task scheduling. Application kernels are individually scheduled as they are submitted for execution, instead of allocating cluster resources to an application for fixed time periods.

#### 2.4.5 FPGAs in the Data Centre

As mentioned in the introduction, the integration of FPGA hardware into data centre environments is an area of active research by both academia and industry. Here we outline a subset of previous work addressing the challenges of using FPGAs at data centre scale.

One of the first major deployments of reconfigurable hardware into a data centre was by Microsoft with the Catapult project [1]. The architecture consists of custom FPGA daughtercards attached to server systems with PCIe. Notably, these FPGA cards are directly connected to each other via a secondary 10 Gbit network, configured in a two-dimensional torus. The authors describe a thread-safe low latency communication interface between the CPU and local FPGA. Their method avoids system call overhead for data transfers by mapping user pages and supports concurrent buffer accesses by dividing buffers into slots and statically assigning slots to threads. We employ a similar memory mapping scheme in our DMA buffer implementation. Furthermore, we note the use of a Gigabit Ethernet network in our work is a limitation we seek to improve in future work.

The follow-up work to Catapult, the Configurable Cloud Architecture [3], removes the need for a secondary network by placing FPGA fabric between network switches and servers. This tightly couples accelerator hardware to the data centre network allowing for the acceleration of network functions such as encryption. The Configurable Cloud uses a global resource manager that tracks FPGA resources which is similar to our approach. However, we also track CPU availability, as our framework schedules kernel tasks to both CPU and FPGA devices.

Several academic works have investigated methods for integrating FPGAs with big data frameworks including Apache Spark. Since Apache Spark is hosted on the Java Virtual Machine (JVM), access to FPGA accelerators must occur over the Java Native Interface (JNI), which can involve significant overhead.

Chen et al. [32] explore the use of fine-grained accelerators within Apache Spark. These are accelerators where the execution time is short, but where the application requires many iterations. They use a DNA sequencing accelerator that exhibits this fine-grained behaviour and present a method for batching groups of tasks when offloading to the FPGA to minimize the JNI-FPGA data transfer overhead.

Ghasemi and Chow [33] also investigate integrating FPGA accelerators with Apache Spark. Notably, their integration method provides direct access to shared memory to limit the number of JNI-FPGA transfers. This enables the efficient transfer of large buffers, therefore limiting data transfer overheads.

Blaze [34] exemplifies a more general approach for integrating with big data frameworks by exposing FPGA accelerators as a service (FaaS). It provides APIs allowing big data processing applications to leverage FPGA accelerators and is demonstrated with Apache Spark. Blaze also extends the Hadoop YARN job scheduler to use accelerator-centric scheduling, allowing for multiple applications to share the use of accelerators. In the initial proof of concept, kernel tasks are only scheduled to FPGA accelerators, though the authors mention CPU and FPGA co-working as an improvement for future work.

Tarafdar et al. [35] present a cluster provisioning tool that provides client users a simple means to map streaming kernel functions to hardware accelerators spread across multiple FPGAs. Users of the framework describe a logical configuration and the communication between kernels in an application. Using this information, the framework allocates FPGA resources from within the cluster.

Eskandari et al. [36] introduce Galapagos, a modular hardware deployment stack for deploying FPGA accelerators in a heterogeneous data centre. This stack consists of communication, network/middleware, hypervisor and physical hardware layers. They provide a communication layer implementation called HUMboldt that utilizes HLS, allowing for applications that link against it to be portable between CPUs and FPGAs. We view the work of HUMboldt as complementary to ours, in that it seeks to provide means for enabling portability of applications between CPUs and FPGAs.

#### 2.4.6 OpenCL for FPGAs

Both the major FPGA vendors, Xilinx and Intel, provide OpenCL platform support for their devices via dedicated software tools: Xilinx SDAccel [5] and Intel OpenCL SDK for FPGAs [6], respectively. SDAccel targets PCIe attached FPGA cards on x86 platforms and uses an HLS back-end to generate accelerator cores to implement kernel functions using FPGA resources. A unique feature of SDAccel is that it allows kernel sources to be written

in C, C++ and OpenCL C or allows accelerators to be described directly in RTL, bypassing the HLS step [37]. Both FPGA vendor OpenCL implementations add some non-standard extensions, enabled via source code pragmas and new OpenCL host API functions. These enable further optimizations for the generated hardware but limit the portability of kernel sources between vendors.

In addition to the FPGA vendor OpenCL implementations, are several academic works exploring how best to support OpenCL on FPGAs. Both OpenRCL [38] and the work of Ma et al. [39] execute OpenCL kernel functions using soft processor cores on FPGAs, rather than using custom accelerators as in our approach. While the works of both Shagrithaya [40] and Hosseinabady [41] map kernel functions to accelerators generated by HLS, they require an initial source-to-source translation on the OpenCL C code. We avoid the need for source-to-source translations by using a more recent version of Xilinx Vivado HLS that natively supports OpenCL C as a source language. We use a similar integration of the hardware accelerators with the host CPU in our prototype platform to that of Hosseinabady, as they also target a Zynq device. UT-OCL [42] implements OpenCL for an embedded FPGA platform using a MicroBlaze soft processor as the host CPU with hardware accelerators also implemented in FPGA fabric. Communication between the host and the device subsystem is via a streaming interconnect.

## Chapter 3

## The CFUSE Framework

The main contribution of this thesis is the introduction of the Cluster Front-end USEr framework (CFUSE). CFUSE is a framework that allows kernels from multiple applications to be executed on the hardware resources available within a network cluster. The scheduling of kernels is handled dynamically as each kernel is submitted for execution by individual client applications. In this chapter, we provide a high-level design overview of the CFUSE framework. A more in-depth discussion of the prototype implementation is left for Chapter 4.

### 3.1 Background

The objective of our work is to develop an abstraction over the possible execution targets within a network cluster. As multiple applications queue work for execution, our abstraction must choose an execution target from the set of possible devices within the cluster. For the purposes of this work, we have chosen to use a cluster with heterogeneous nodes containing a central processing unit (CPU) and field-programmable gate array (FPGA) fabric, used to host custom hardware accelerator cores. While we could also investigate the use of graphics processing units (GPUs) in the cluster, we have restricted our scope to CPU and FPGA devices only.

To realize our abstraction model, which we name CFUSE, we seek to utilize a lower-level programming framework with the ability to specify application tasks and submit them for execution. For this purpose, we have chosen to create CFUSE using the OpenCL framework [9]. OpenCL kernels are application functions that are marked for acceleration and may be written in OpenCL C, a portable parallel programming language. OpenCL also defines a runtime application programming interface (API) used to submit kernels for execution on devices. However, there are several OpenCL limitations that we must overcome to make it suitable for use with our abstraction.

The OpenCL specification defines a platform model consisting of a host processor attached to one or more devices. The host processor runs the application code and manages the launching of kernels that are executed exclusively on devices. For a typical FPGA

OpenCL implementation, the host processor is the system CPU, while a device is a region of the FPGA fabric. Modern cluster system CPUs are generally multi-core processors, but since the system processor acts as the OpenCL host, these cores are not available to run application kernels. Furthermore, OpenCL restricts its platform model to a single network node and there is no method available for distributing kernel executions onto other nodes within a cluster. Finally, OpenCL is a low-level framework. The application programmer is responsible for managing device work queues and moving program data between the host processor and devices.

### 3.2 Execution Model

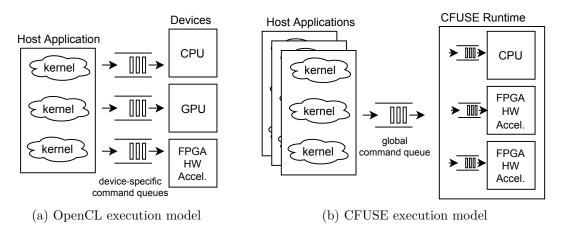

Figure 3.1: OpenCL and CFUSE execution models. OpenCL requires a command queue per device. CFUSE abstracts the use of a specific device using a global command queue.

CFUSE is designed to follow the OpenCL execution model, whereby applications specify kernel functions for accelerated execution on capable hardware devices. As with OpenCL, in the CFUSE framework, kernel functions are executed by submitting commands to a command queue. However, instead of selecting the target device explicitly by submitting to a device-specific queue, the CFUSE model uses a shared queue for all devices. In this way, CFUSE adapts the OpenCL execution model to the concept of the Front-end USEr framework (FUSE) [4], where the runtime system is responsible for choosing a suitable target device. The mapping of kernels onto specific devices is abstracted from the application developer.

CFUSE can be viewed as an extension of the original FUSE work for cluster systems, which has re-targeted the underlying execution model from pthreads to OpenCL. While the initial FUSE implementation managed CPU and FPGA-based hardware accelerators within a single network host for a single application, CFUSE provides multiple applications a means to execute kernels on these device types, both on the local host and remote nodes within a cluster.

## 3.3 Overview

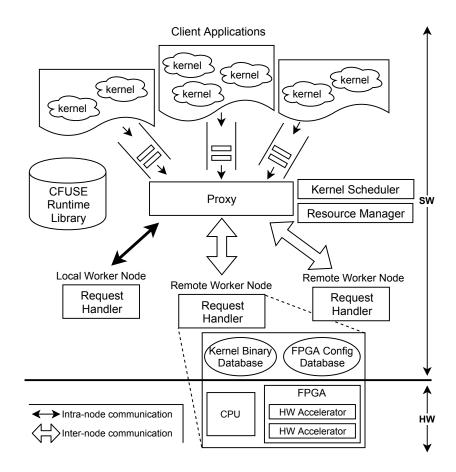

The runtime of the CFUSE framework consists of the following components:

- proxy

- kernel scheduler

- resource manager

- request handler

- runtime library

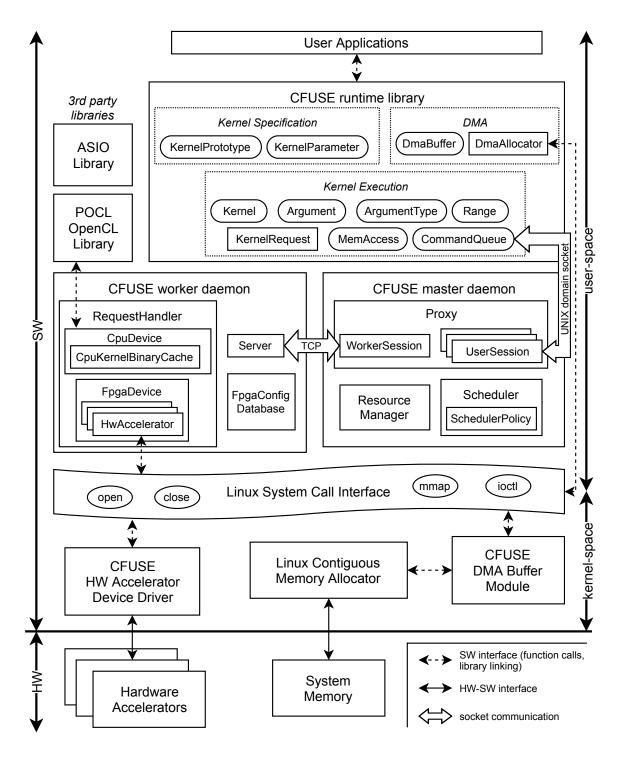

Figure 3.2: CFUSE runtime system overview

Figure 3.2 shows the interaction between these framework components and the basic process by which kernels are mapped to the compute resources. To summarize, a *runtime library* provides client applications with an interface to the facilities of the CFUSE runtime by exporting an object-oriented API. The main object provided by this library is a command queue, which client applications use to submit kernel requests for execution by the runtime. The *proxy* collects requests sent to these queues and forwards them to an appropriate *worker node*, where they are serviced by a *request handler*. The *kernel scheduler* is responsible

for selecting the most suitable target device for each request. To make this decision, the scheduler consults the current status of the possible target devices in the cluster. This status information is maintained by the *resource manager*.

A request handler running on a worker node is responsible for managing the devices on that node. The handler executes kernel requests as they are received and sends a response containing kernel output data back to the proxy. This response may be used to update the resource manager. Finally, the proxy forwards this response back to the client application which initiated the request.

# 3.4 Component Details

In the following subsections, we describe the function of each of the components of the CFUSE framework runtime in more detail.

#### 3.4.1 Proxy

The primary role of the proxy is to enable communication between client applications and the request handlers operating on each worker node. At system startup, the proxy establishes connections to each request handler and creates an endpoint that client applications use to establish connections to the proxy. Client applications submit kernel requests, which are sent to the proxy via these connections. The proxy then forwards these requests to an appropriate worker, as determined by the scheduler. The proxy is also responsible for forwarding kernel responses, which consist of kernel output argument data, back to the correct client application.

#### 3.4.2 Resource Manager

The resource manager is responsible for tracking the availability of all the possible execution devices in the cluster. For each network node, this includes the CPU device and any hardware accelerators that are currently configured in the FPGA fabric of that node. This device status information is maintained globally within the resource manager and made available to the kernel scheduler. Device status is initialized at system startup and then updated both when a kernel request is scheduled or a response is received.

A primary design choice for the resource manager is between a centralized or distributed design. For our implementation, we have elected to use a centralized resource manager hosted on a single network node. Therefore, the resource manager has a global view of the device status for each node in the cluster. However, maintaining status information with this approach is more expensive. Status updates take longer to complete since they must propagate through the network.

#### 3.4.3 Kernel Scheduler

The role of the kernel scheduler is to select a target device, either CPU or accelerator, for each kernel request received by the proxy. To do so, the scheduler uses kernel metadata stored within the request. This includes information such as the kernel function name used to find matching hardware accelerators, and the size of the kernel argument data that must be transferred. The scheduler uses this kernel metadata combined with the current device status information from the resource manager to make a scheduling decision based on a specific scheduling policy. The scheduler then adds the selected target device to the header of the request and informs the proxy of which node the request should be forwarded to for handling.

#### 3.4.4 Request Handler

A request handler running on a worker node manages access to the devices on that node. The request handler receives requests from the proxy, reads the execution target from the request header and signals the target device to execute the kernel. Once a kernel request is completed by the handler, a response is sent back to the proxy to be forwarded to the user application that originally sent the request. The request handler is also responsible for managing a database of compiled kernel binaries for the CPU targets, and a database of FPGA configurations containing accelerators. These databases are specific to each worker node.

#### 3.4.5 Runtime Library

The runtime library provides an object-oriented interface to the CFUSE framework for individual client applications. The main purpose of the library is to hide implementation details related to how the remaining components of the CFUSE framework interact to execute kernels on behalf of an application.

The API provided is designed as a light abstraction over the OpenCL execution model. User applications link against the runtime library which provides objects allowing for the specification of kernels, memory buffers to be passed as kernel arguments, and a command queue to which kernel requests are submitted for execution. This command queue is not associated with a specific device, as is the case with the OpenCL host API command queue. As previously mentioned, this allows the CFUSE runtime to select the most appropriate target device for kernel requests as they are received.

# Chapter 4

# CFUSE Prototype Implementation

This chapter discusses the prototype implementation of the CFUSE framework including the platform hardware and the software we developed. We present the implementation details beginning with a discussion of our cluster hardware and the accelerators used to implement kernel functions. We then describe the design of the various software components that make up the CFUSE framework, including the device drivers, system daemons and the runtime library for client applications. Finally, we provide an overview of the automation tool flow used to both simplify the creation of field-programmable gate array (FPGA) configurations, and to build the embedded Linux operating system (OS) that runs on each board.

#### 4.1 Cluster Hardware

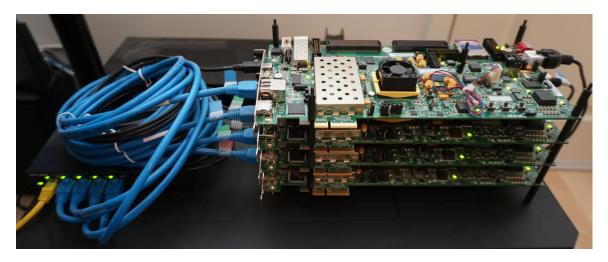

In order to have full control over the hardware interfaces and software stack used in the prototype, we opt not to use a public cloud such as a set of Amazon Web Services (AWS) Elastic Compute Cloud (EC2) F1 instances [2]. Instead, we use a custom-built cluster. Our target system for the prototype is a cluster consisting of four FPGA development boards that each contain a multi-core CPU and reconfigurable FPGA fabric. These boards are connected over a Gigabit Ethernet network formed by directly connecting each board to an Ethernet switch. Figure 4.1 shows a photograph of the prototype cluster system.

We have selected the Xilinx ZC706 Evaluation Kit [43] for the FPGA development boards in the cluster. The ZC706 board features a Xilinx Zynq-7000 XC7045 All Programmable system-on-chip (SoC) [44], which integrates a dual-core ARM processor system with FPGA fabric. These boards also feature a Gigabit Ethernet network interface, which is used to connect each board to a 8-port switch, forming the cluster network. We use a TP-Link TL-SG108 [45] for the network switch, which is an off-the-shelf unmanaged Gigabit switch. This switch offers a switching capacity of 16 Gbps with theoretically equal throughput for each port.

Figure 4.1: The target platform cluster for the CFUSE prototype implementation. Four Xilinx ZC706 FPGA development boards are connected to a TP-Link TL-SG108 8-port Gigabit Ethernet switch.

Note: Arrow direction shows control (master to slave)

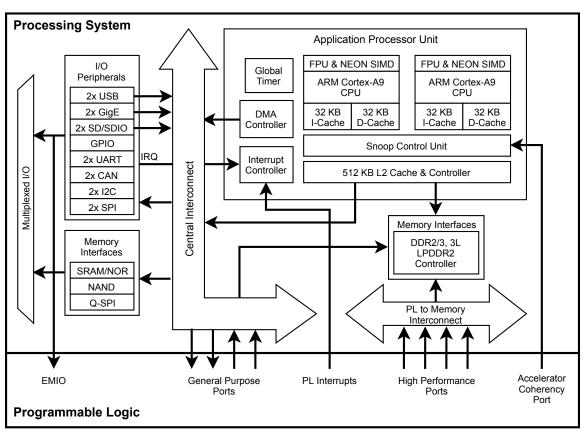

Figure 4.2: Zynq-7000 device block diagram. Adapted from [44].

## 4.1.1 Zynq-7000 System-on-Chip

A simplified block diagram of the Xilinx Zynq-7000 family of devices is shown in Figure 4.2. The Zynq device is divided into the *Processing System (PS)* and *Programmable Logic (PL)* regions. The Processing System contains the ARM multiprocessor system-on-chip (MP-SoC), which includes the Application Processor Unit (APU), memory interfaces to off-chip memory, and I/O peripheral cores. The Programmable Logic contains the FPGA fabric and reconfiguration hardware. For the prototype, we configure the processors to use a clock speed of 667 MHz and the logic in the PL uses a common 100 MHz clock. We selected this fabric clock speed as it is a reasonable frequency target for the accelerator cores of our benchmark applications.

The Application Processor Unit includes two ARM Cortex-A9 processors which feature 32 KB L1 instruction and data caches, a floating-point unit (FPU) and a NEON single instruction multiple data (SIMD) media engine. The APU also contains a unified 512 KB L2 cache and Snoop Control Unit (SCU), which manages processor cache coherency and enables coherent access to the L2 cache from the PL via the Accelerator Coherency Port (ACP).

The Zynq device uses hardware interfaces following the Advanced eXtensible Interface (AXI) protocol throughout. The AXI protocol is a bus architecture that defines three related interfaces [46]. Memory-mapped AXI is a high performance interface supporting variable sized burst transfers and interface data widths ranging from 8 to 1024 bits. AXI Lite is a simplified version of the full AXI protocol without burst transfer support and is intended for low throughput applications. AXI Stream is a point to point streaming protocol without address channels.

Three sets of AXI interfaces enable communication across the PS-PL boundary: four *High Performance (HP) ports*, four *General Purpose (GP) ports* and one *Accelerator Coherency Port (ACP)*. Each of these interfaces is intended for a particular use case. The High Performance ports provide high bandwidth access from the Programmable Logic to external DDR memory. The General Purpose ports are meant for register style accesses between the Processing System and Programmable Logic. Finally, the Accelerator Coherency Port provides low latency, coherent access to the APU L2 cache from the Programmable Logic. A set of PS-PL interrupts are also available, allowing for custom hardware in the Programmable Logic to use interrupt-driven I/O. In the following section, we describe how we use these PS-PL interfaces to integrate custom hardware accelerators.

## 4.2 Hardware Accelerators

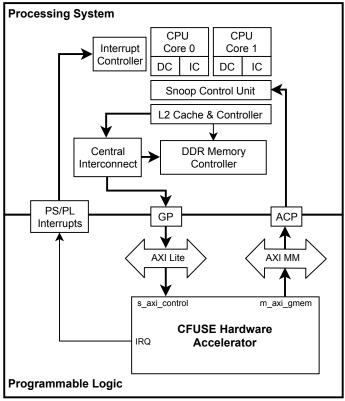

In the CFUSE framework, custom hardware accelerators are used to implement kernel functions in hardware. For the prototype, these are instantiated in the Programmable Logic of the Zynq device and connected to the Processing System, as shown in Figure 4.3. CFUSE

utilizes high-level synthesis (HLS) to produce synthesizeable HDL (hardware description language) code from kernel function source code written in either C++ or OpenCL C. We use the Xilinx Vivado HLS 2016.4 tool to perform this conversion [7]. Vivado HLS is capable of generating hardware Intellectual Property (IP) cores with a variety of different hardware interfaces both for controlling the IP core and transferring data to and from the core. While the design of each individual interface is fixed and specified by Vivado HLS, the specific interfaces to use for a given accelerator may be customized.

Note: Arrow direction shows control (master to slave)

Figure 4.3: CFUSE hardware accelerator architecture

We choose to use a common interface for all the hardware accelerators we generate for the prototype. A common interface allows a single OS device driver to control each accelerator instance from software. This accelerator interface consists of the following:

- An AXI Lite slave for register based control (s\_axi\_control) that connects to a General Purpose port.

- A memory-mapped AXI master interface (m\_axi\_gmem) that connects to the Accelerator Coherency Port.

- An interrupt request output (IRQ).