# Generalized methods for application specific hardware specialization

by

#### Snehasish Kumar

M. Sc., Simon Fraser University, 2013B. Tech., Biju Patnaik University of Technology, 2010

Dissertation Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

> in the School of Computing Science Faculty of Applied Sciences

© Snehasish Kumar 2017 SIMON FRASER UNIVERSITY Spring 2017

All rights reserved.

However, in accordance with the Copyright Act of Canada, this work may be reproduced without authorization under the conditions for "Fair Dealing." Therefore, limited reproduction of this work for the purposes of private study, research, education, satire, parody, criticism, review and news reporting is likely to be in accordance with the law, particularly if cited appropriately.

# Approval

| Name:                                                                                     | Snehas                                                               | ish Kumar                         |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------|

| Degree:                                                                                   | Doctor                                                               | of Philosophy (Computing Science) |

| Title:                                                                                    | Generalized methods for application specific hardware specialization |                                   |

| Examining Committee:                                                                      | Chair:                                                               | Binay Bhattacharyya<br>Professor  |

| Arrvindh Shriraman<br>Senior Supervisor<br>Associate Professor<br>Simon Fraser University |                                                                      |                                   |

| William Sumner Supervisor Assistant Professor Simon Fraser University                     |                                                                      |                                   |

| Vijayalakshmi Srinivasa<br>Supervisor<br>Research Staff Member,<br>IBM Research           | n                                                                    |                                   |

| Alexandra Fedorova Supervisor Associate Professor University of British Colum             | ıbia                                                                 |                                   |

| Richard Vaughan Internal Examiner Associate Professor Simon Fraser University             |                                                                      |                                   |

| Andreas Moshovos External Examiner Professor University of Toronto                        |                                                                      |                                   |

| Data Dafandad                                                                             |                                                                      | November 21, 2016                 |

## Abstract

Since the invention of the microprocessor in 1971, the computational capacity of the microprocessor has scaled over 1000× with Moore and Dennard scaling. Dennard scaling ended with a rapid increase in leakage power 30 years after it was proposed. This ushered in the era of multiprocessing where additional transistors afforded by Moore's scaling were put to use. With the scaling of computational capacity no longer guaranteed every generation, application specific hardware specialization is an attractive alternative to sustain scaling trends. Hardware specialization broadly refers to the identification and optimization of recurrent patterns, dynamic and static, in software via integrated circuitry.

This dissertation describes a two-pronged approach to architectural specialization. First, a top down approach uses program analysis to determine code regions amenable for specialization. We have implemented a prototype compiler tool-chain to automatically identify, analyze, extract and grow code segments which are amenable to specialization in a methodical manner. Second, a bottom up approach evaluated particular hardware enhancements to enable the efficient data movement of specialized regions. We have devised and evaluated coherence protocols and flexible caching mechanisms to reduce the overhead of data movement within specialized regions.

The former workload centric approach analyses programs at the *path* granularity. Our observations show that analysis of amenability for specialization along the path granularity yield different conclusions than prior work. We analyse the potential for performance and energy improvement via specialization at the path granularity. We develop mechanisms to extract and merge amenable paths into segments called *Braids*. This allows for increased offload opportunity while retaining the same interface as path granularity specialization.

To address the challenges of data movement, the latter micro-architecture first approach, proposes a specialized coherence protocol tailored for accelerators and an adaptive granularity caching mechanism. The hybrid coherence protocol localizes data movement to a specialized accelerator-only tile reducing energy consumption and improving performance. Modern workloads have varied program characteristics where fixed granularity caching often introduces waste in the cache hierarchy. We propose a variable granularity caching mechanism which reduces energy consumption while improving performance via better utilization of the available storage space.

$\textbf{Keywords:} \ \ \text{hardware accelerators, program analysis, energy efficiency, caching, accelerator benchmark, coherence protocol}$

# Dedication

Dedicated to Baba, Ma, Bukum and Tinki

# Acknowledgements

I would like to thank my supervisors, Dr. Arrvindh Shriraman, Dr. Nick Sumner, Dr. Viji Srinivasan and Dr. Alexandra Fedorova for their guidance, motivation and support. I would like to thank my colleagues, Amirali Sharifian, Naveen Vedula, Steve Margerm and Dr. Apala Guha for their help and support. I would also like to thank Dr. Andreas Moshovos for serving as examiner on such short notice. Additionally, the departmental staff, Melissa and David, have been very helpful in the final stages of preparing the thesis. Finally, I would like to thank my lovely wife, Tinki, for her patience as I worked my way through graduate school instead of getting a real job.

# **Table of Contents**

| A  | ppro                   | val                                                              | ii        |

|----|------------------------|------------------------------------------------------------------|-----------|

| A  | bstra                  | ct                                                               | iii       |

| D  | edica                  | tion                                                             | v         |

| A  | cknov                  | wledgements                                                      | vi        |

| Ta | able o                 | of Contents                                                      | vii       |

| Li | st of                  | Tables                                                           | xi        |

| Li | st of                  | Figures                                                          | xii       |

| 1  | Intr                   | roduction                                                        | 1         |

|    | 1.1                    | The breakdown of technology scaling                              | 1         |

|    | 1.2                    | Challenges                                                       | 6         |

|    | 1.3                    | Approach                                                         | 7         |

|    | 1.4                    | Dissertation Organisation                                        | 9         |

| 2  | Bac                    | kground                                                          | 11        |

|    | 2.1                    | Application Specific Hardware Specialization                     | 14        |

|    | 2.2                    | Challenges                                                       | 15        |

|    |                        | 2.2.1 Challenge 1: What to specialize?                           | 15        |

|    |                        | 2.2.2 Challenge 2: How to specialize?                            | 17        |

|    |                        | 2.2.3 Challenge 3: Integration                                   | 18        |

|    | 2.3                    | Thesis Contributions                                             | 19        |

|    | 2.4                    | Relationship to published work                                   | 21        |

| 3  | $\mathbf{W}\mathbf{h}$ | at to specialize – Extracting Accelerator Benchmarks from Micro- |           |

|    | pro                    | cessor Benchmarks                                                | <b>23</b> |

|    | 3.1                    | Introduction                                                     | 23        |

|    | 3.2                    | Motivation & Methodology                                         | 25        |

|    |                        | 3.2.1 Acyclic Program Paths [15]                                 | 25        |

|   |      | 3.2.2 Selecting Paths to Characterize                              |

|---|------|--------------------------------------------------------------------|

|   |      | 3.2.3 Extracting identified paths                                  |

|   |      | 3.2.4 Metrics & ISA-independence                                   |

|   |      | 3.2.5 Characterizing at the Path Level                             |

|   |      | 3.2.6 Benchmarks                                                   |

|   | 3.3  | Characterization                                                   |

|   |      | 3.3.1 Making a case for Path-based Acceleration                    |

|   |      | 3.3.2 Characteristics Summary                                      |

|   | 3.4  | Path Characteristic Variability                                    |

|   | 3.5  | Path Derived Workload Suite                                        |

|   |      | 3.5.1 Memory Address Entropy Analysis                              |

|   | 3.6  | Related Work                                                       |

|   | 3.7  | Conclusion                                                         |

| 4 | Hov  | v to specialize – Leveraging Program Analysis to Extract Accelera- |

|   | tors | from Whole Programs 45                                             |

|   | 4.1  | Introduction                                                       |

|   | 4.2  | Scope and Related Work                                             |

|   |      | 4.2.1 Hardware Accelerator Perspective                             |

|   |      | 4.2.2 Compilers for VLIW processors                                |

|   | 4.3  | BL-Path Accelerators                                               |

|   |      | 4.3.1 Path Ranking                                                 |

|   |      | 4.3.2 BL-Path Properties                                           |

|   | 4.4  | BL-Path Expansion and Braids                                       |

|   |      | 4.4.1 BL-Path Target Expansion                                     |

|   |      | 4.4.2 Braids – Merging BL-Paths                                    |

|   | 4.5  | Execution Model                                                    |

|   | 4.6  | Evaluation                                                         |

|   |      | 4.6.1 Performance                                                  |

|   |      | 4.6.2 Energy Evaluation                                            |

|   | 4.7  | Conclusion                                                         |

| 5 | Inte | egration – Coherent Cache Hierarchies for Accelerators 68          |

|   | 5.1  | Introduction                                                       |

|   | 5.2  | Background and Motivation                                          |

|   |      | 5.2.1 Baseline Architectures                                       |

|   | 5.3  | FUSION: A Coherent Accelerator Cache Hierarchy                     |

|   |      | 5.3.1 Design Overview                                              |

|   |      | 5.3.2 <i>FUSION</i> Architecture                                   |

|   | 5.4  | Toolchain and Benchmarks                                           |

|   | 5.5  | Evaluation                                                     |

|---|------|----------------------------------------------------------------|

|   |      | 5.5.1 Performance                                              |

|   |      | 5.5.2 Energy                                                   |

|   |      | 5.5.3 Writeback vs Write-Through at L0X                        |

|   |      | 5.5.4 FUSION-Dx: Write Forwarding                              |

|   |      | 5.5.5 Larger AXC caches                                        |

|   |      | 5.5.6 Address Translation                                      |

|   | 5.6  | Related Work                                                   |

|   | 5.7  | Summary                                                        |

| 6 | Inte | gration – Adaptive Granularity Caching 9                       |

|   | 6.1  | Introduction                                                   |

|   | 6.2  | Motivation for Adaptive Blocks                                 |

|   |      | 6.2.1 Cache Utilization                                        |

|   |      | 6.2.2 Effect of Block Granularity on Miss Rate and Bandwidth 9 |

|   |      | 6.2.3 Need for adaptive cache blocks                           |

|   | 6.3  | Amoeba-Cache: Architecture                                     |

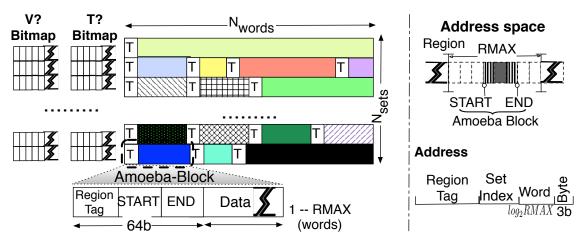

|   |      | 6.3.1 Amoeba Blocks and Set-Indexing                           |

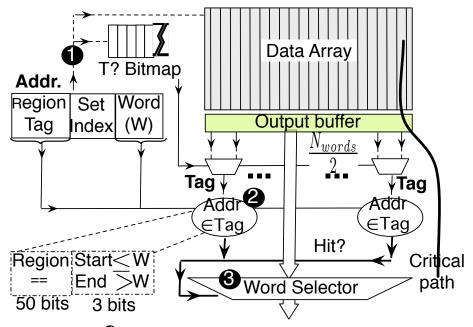

|   |      | 6.3.2 Data Lookup                                              |

|   |      | 6.3.3 Amoeba Block Insertion                                   |

|   |      | 6.3.4 Replacement: Pseudo LRU                                  |

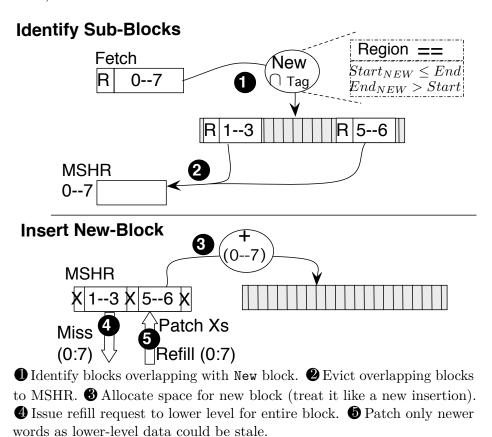

|   |      | 6.3.5 Partial Misses                                           |

|   | 6.4  | Hardware Complexity                                            |

|   |      | 6.4.1 Cache Controller                                         |

|   |      | 6.4.2 Area, Latency, and Energy Overhead                       |

|   |      | 6.4.3 Tag-only Operations                                      |

|   |      | 6.4.4 Tradeoff with Large Caches                               |

|   | 6.5  | Chip-Level Issues                                              |

|   |      | 6.5.1 Spatial Patterns Prediction                              |

|   |      | 6.5.2 Multi-level Caches                                       |

|   |      | 6.5.3 Cache Coherence                                          |

|   | 6.6  | Evaluation                                                     |

|   |      | 6.6.1 Improved Memory Hierarchy Efficiency                     |

|   |      | 6.6.2 Overall Performance and Energy                           |

|   | 6.7  | Spatial Predictor Tradeoffs                                    |

|   |      | 6.7.1 Predictor Indexing                                       |

|   |      | 6.7.2 Predictor Table                                          |

|   |      | 6.7.3 Spatial Pattern Training                                 |

|   |      | 6.7.4 Predictor Summary                                        |

|    | 6.8   | Amoeba-Cache Adaptivity                                         | 119          |

|----|-------|-----------------------------------------------------------------|--------------|

|    | 6.9   | Amoeba-Cache vs other approaches                                | 120          |

|    | 6.10  | Multicore Shared Cache                                          | 122          |

|    | 6.11  | Related Work                                                    | 123          |

|    | 6.12  | Conclusion                                                      | 124          |

| 7  | Soft  | ware Release                                                    | L <b>25</b>  |

|    | 7.1   | Path Profiling                                                  | 125          |

|    | 7.2   | Path Derived Workload Suite                                     | 125          |

|    | 7.3   | Needle                                                          | 126          |

|    | 7.4   | Fusion Simulator                                                | 127          |

|    | 7.5   | Amoeba Simulator                                                | 127          |

| 8  | Futi  | are Work and Conclusion                                         | L <b>2</b> 8 |

|    | 8.1   | Concurrent and Future Work                                      | 128          |

|    |       | 8.1.1 Macro Instructions from Sequentially Dependent Operations | 128          |

|    |       | 8.1.2 Eliminating the Load-Store Queue for Specialized Units    | 129          |

|    |       | 8.1.3 Software specialization based on dynamic profiling        | 129          |

|    |       | 8.1.4 Micro-Workload Generation                                 | 131          |

|    | 8.2   | Summary of contributions                                        | 131          |

| Bi | bliog | raphy 1                                                         | 133          |

# List of Tables

| Table 3.1 | Workload Characteristics                                                                                                                           | 34  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2 | Path Predictability                                                                                                                                | 38  |

| Table 4.1 | Comparison of sequential programs on spatial architectures                                                                                         | 48  |

| Table 4.2 | Control flow Characteristics                                                                                                                       | 49  |

| Table 4.3 | Path Characteristics                                                                                                                               | 56  |

| Table 4.4 | Next Path Target Expansion                                                                                                                         | 58  |

| Table 4.5 | Braid Characteristics                                                                                                                              | 60  |

| Table 4.6 | System parameters                                                                                                                                  | 63  |

| Table 5.1 | Accelerator Characteristics                                                                                                                        | 75  |

| Table 5.2 | System parameters                                                                                                                                  | 83  |

| Table 5.3 | Accelerator Execution Metrics                                                                                                                      | 84  |

| Table 5.4 | Bandwidth in Flits (8bytes/flit)                                                                                                                   | 88  |

| Table 5.5 | Inter-AXC forwarded blocks and percentage reduction in energy con-                                                                                 |     |

|           | sumption per component                                                                                                                             | 89  |

| Table 5.6 | Virtual memory table look up count                                                                                                                 | 89  |

| Table 6.1 | Benchmark Groups                                                                                                                                   | 96  |

| Table 6.2 | Optimal block size. Metric: $\frac{1}{\text{Miss-rate} \times \text{Bandwidth}} \cdot \cdot$ | 98  |

| Table 6.3 | Amoeba-Cache Hardware Complexity                                                                                                                   | 105 |

| Table 6.4 | % of direct accesses with fast tags                                                                                                                | 108 |

| Table 6.5 | Avg. # of Amoeba-Block / Set                                                                                                                       | 113 |

| Table 6.6 | Amoeba-Cache Performance. Absolute #s                                                                                                              | 118 |

| Table 6.7 | Predictor Policy Comparison                                                                                                                        | 120 |

| Table 6.8 | Multiprogrammed Workloads on 1M Shared $Amoeba\text{-}Cache\dot{\%}$ reduction                                                                     |     |

|           | in miss rate and bandwidth. Baseline: Fixed 1M                                                                                                     | 123 |

# List of Figures

| Figure 1.1 | Moore's Law [122]                                                                                                                                                  | 2  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 | Moore's Cost Data [122]                                                                                                                                            | 2  |

| Figure 1.3 | Transistor Size Scaling [25]                                                                                                                                       | 3  |

| Figure 1.4 | Transistor Cost Scaling [123]                                                                                                                                      | 3  |

| Figure 1.5 | Voltage Scaling [44]                                                                                                                                               | 4  |

| Figure 1.6 | Frequency Scaling [44]                                                                                                                                             | 4  |

| Figure 2.1 | Amdahl's Projection [6]                                                                                                                                            | 12 |

| Figure 2.2 | Multicore Scaling [49]                                                                                                                                             | 12 |

| Figure 2.3 | Intel Tick [7, 147]                                                                                                                                                | 12 |

| Figure 2.4 | Cost/Transistor stops scaling [149]                                                                                                                                | 12 |

| Figure 2.5 | Performance increase more than technology scaling [44]                                                                                                             | 13 |

| Figure 3.1 | Using program analysis to demarcate and extract code paths [15] for accelerators within CPU programs                                                               | 25 |

| Figure 3.2 | Acyclic paths in a control flow graph                                                                                                                              | 26 |

| Figure 3.3 | Path Bias                                                                                                                                                          | 27 |

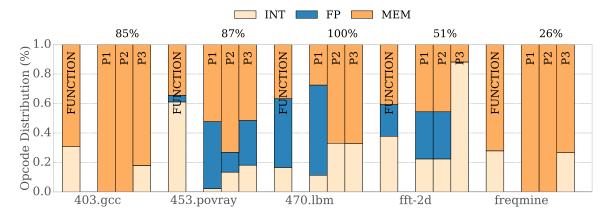

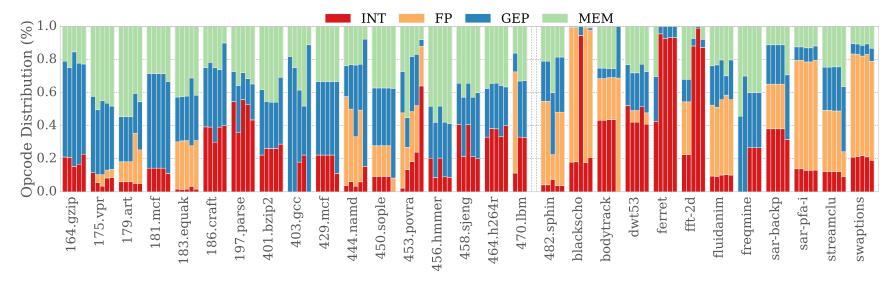

| Figure 3.4 | Benefits of Path-Based Execution. We have only shown a few work-loads due to lack of space. Opcode histogram of paths within a function of indicates are severe as | 31 |

| Figure 3.5 | function; % indicates exec coverage                                                                                                                                | 91 |

| rigure 5.5 | top-5 hot paths (L-R), GEP=pointer access                                                                                                                          | 32 |

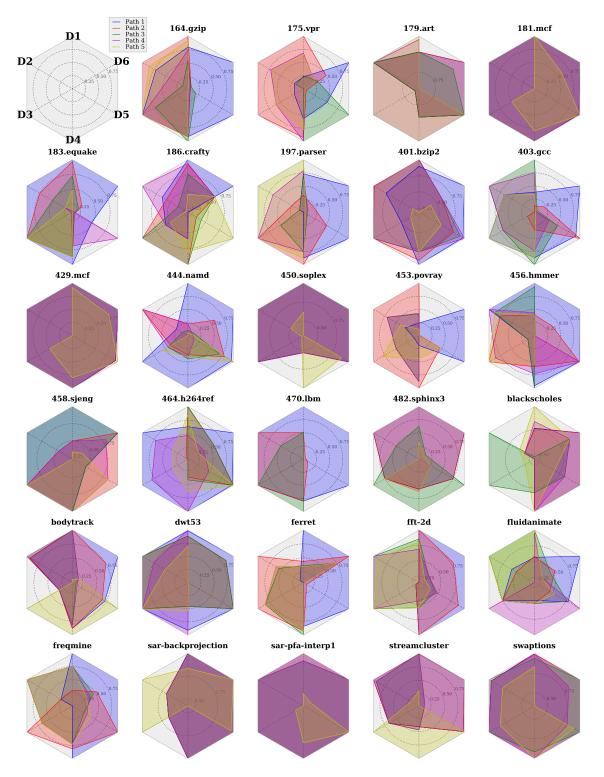

| Figure 3.6 | <b>D1</b> : Total Ins, <b>D2</b> : Guards, <b>D3</b> : $\phi$ 's Simplified, <b>D4</b> : Total Live Vals,                                                          |    |

| J          | <b>D5</b> : Path Predictability <b>D6</b> : Path Coverage                                                                                                          | 39 |

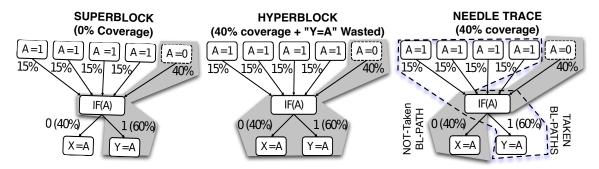

| Figure 4.1 | Superblock and Hyperblock construction for overlapped paths. $\%$                                                                                                  |    |

|            | indicates the relative frequency                                                                                                                                   | 51 |

| Figure 4.2 | The distribution of biased branches in the application. Applications not shown in the plot have 99% of the branches with each branch                               |    |

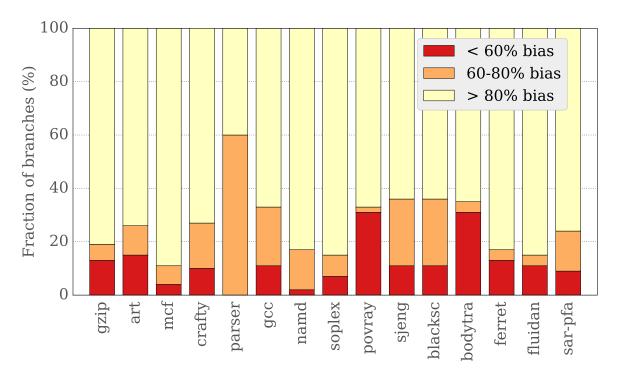

|            | > 80% bias                                                                                                                                                         | 52 |

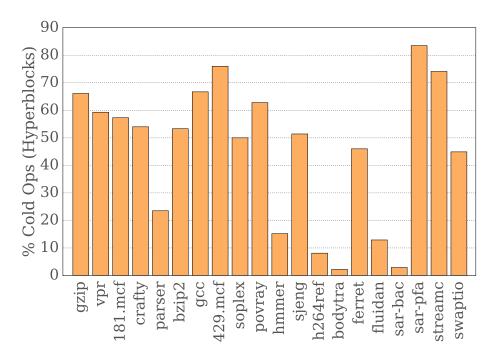

| Figure 4.3 | Fraction of "cold" ops included in Hyperblocks                                                                                                                     | 53 |

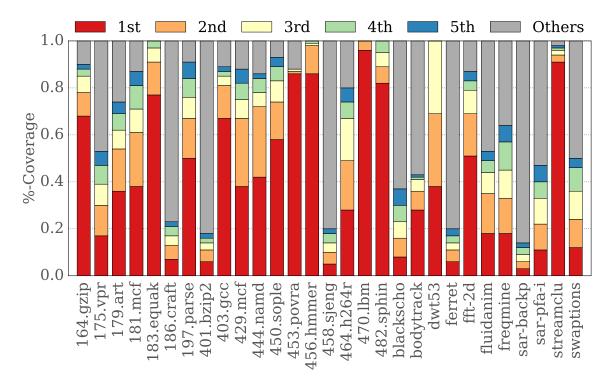

| Figure 4.4 | Path Coverage: Path weight $(P_{wt})$ by rank                                                                                                                      | 54 |

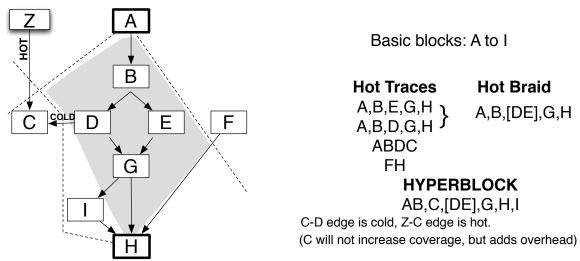

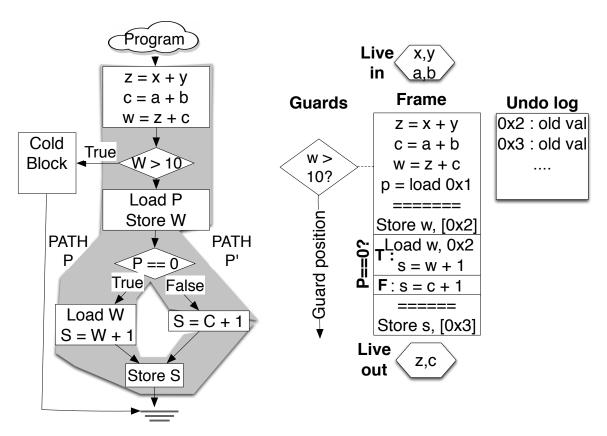

| Figure 4.5 | Braid construction from BL-Paths                                                                                                                                   | 59 |

| 5 410 1.0  |                                                                                                                                                                    | 00 |

| Figure 4.6 | Frame construction from Braid                                                                                                     | 62  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

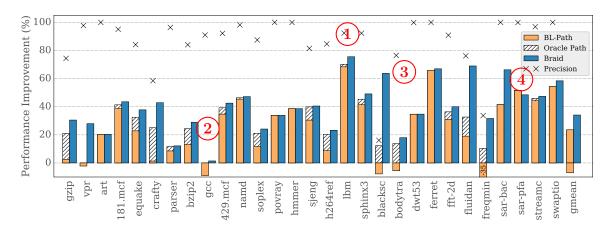

| Figure 4.7 | Performance Improvement                                                                                                           | 63  |

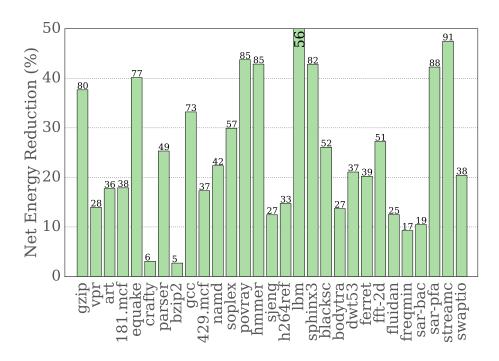

| Figure 4.8 | Net Energy Reduction for Braid                                                                                                    | 66  |

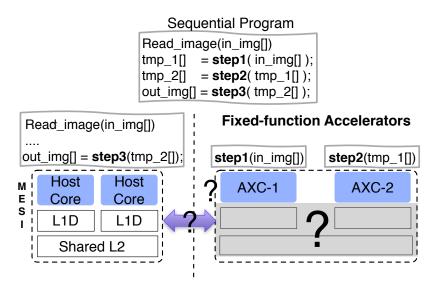

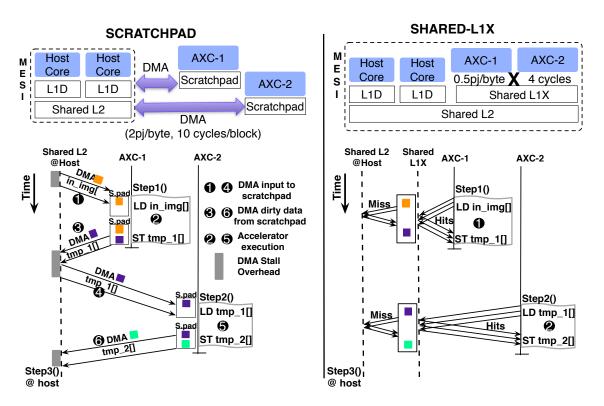

| Figure 5.1 | Offloading Sequential Program to Accelerators                                                                                     | 69  |

| Figure 5.2 | Left: SCRATCH Architecture. Per-accelerator scratchpads into which DMA transfers data. Switches to a different accelerator Right: |     |

|            | SHARED. Shared L1 cache between the accelerators in a tile. The Shared L1 cache is kept coherent with the host multicore through  |     |

|            | MESI protocol. Host shared L2 maintains inclusion with the acceler-                                                               |     |

|            | ators shared L1X                                                                                                                  | 71  |

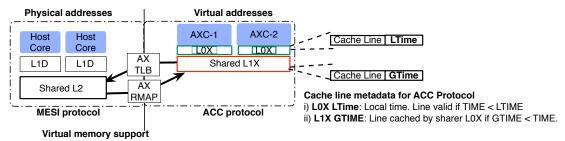

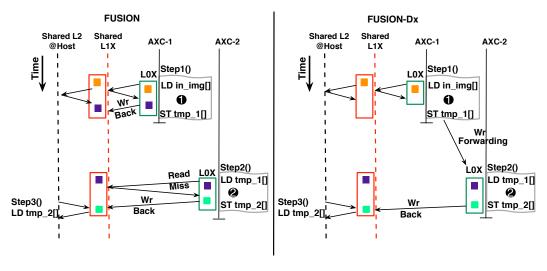

| Figure 5.3 | $\operatorname{Top}:FUSION$ Architecture. Bottom: Timeline for image processing                                                   |     |

|            | example on $FUSION$ and $FUSION-Dx$                                                                                               | 77  |

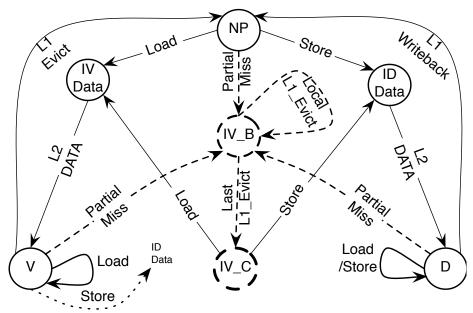

| Figure 5.4 | Left: ACC protocol servicing requests from accelerator and interaction                                                            |     |

|            | with MESI. Right: ACC Protocol servicing forwarded requests from                                                                  |     |

|            | MESI                                                                                                                              | 80  |

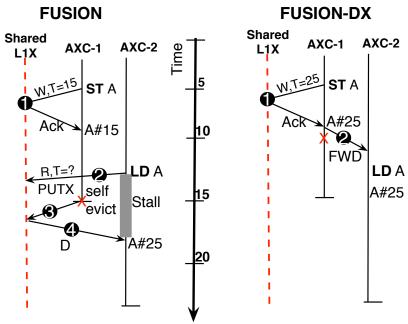

| Figure 5.5 | Left: FUSION without write forwarding. Right: FUSION-Dx. ACC                                                                      |     |

|            | protocol with write forwarding                                                                                                    | 82  |

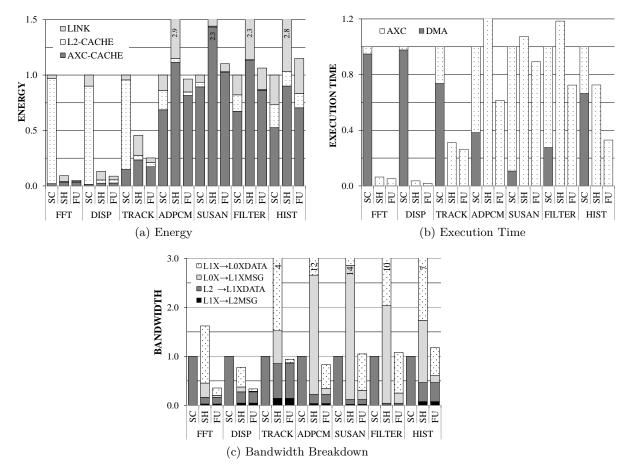

| Figure 5.6 | Design tradeoffs in the accelerator cache hierarchy. X-Axis SC:                                                                   |     |

|            | SCRATCH, SH: SHARED, FU: FUSION. Y-Axis: All plots/fusion,                                                                        |     |

|            | lower is better and values are normalized to SCRATCH system. Note                                                                 |     |

|            | for the $SHARED$ design, the L1X $\rightarrow$ L0XDATA represents response                                                        |     |

|            | from shared L1X to AXC and L0X $\rightarrow$ L1XMSG represents requests                                                           |     |

|            | from AXC to the shared L1X. For the <i>SCRATCH</i> design, there is                                                               |     |

|            | only one link for data from L2 to the local scratchpad                                                                            | 86  |

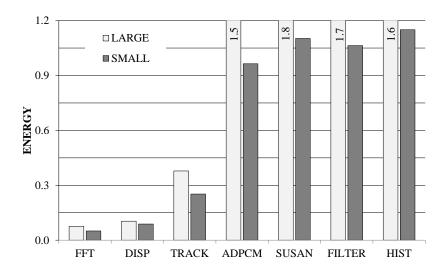

| Figure 5.7 | Comparing the benefits of LARGE (L0X:8KB,L1X:256KB) vs SMALL                                                                      |     |

|            | (L0X:4KB,L1X:64KB)                                                                                                                | 90  |

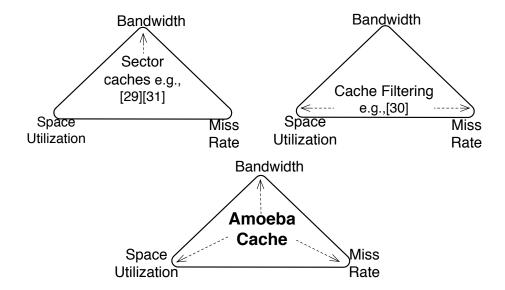

| Figure 6.1 | Cache designs optimizing different memory hierarchy parameters.                                                                   |     |

|            | Arrows indicate the parameters that are targeted and improved                                                                     |     |

|            | compared to a conventional cache.                                                                                                 | 94  |

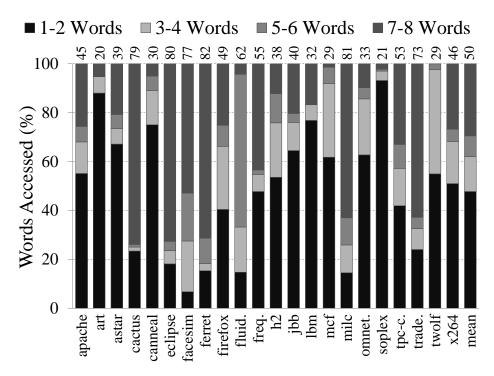

| Figure 6.2 | Distribution of words touched in a cache block. Avg. utilization is                                                               |     |

|            | on top. (Config: 64K, 4 way, 64-byte block.)                                                                                      | 97  |

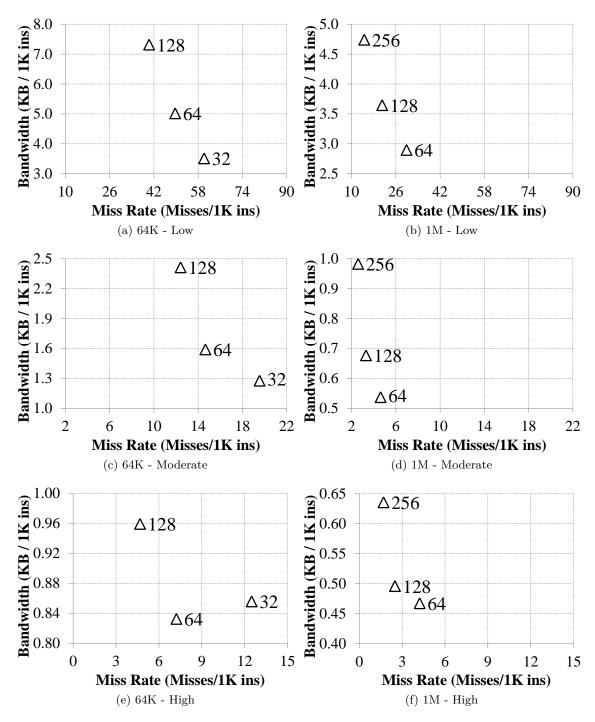

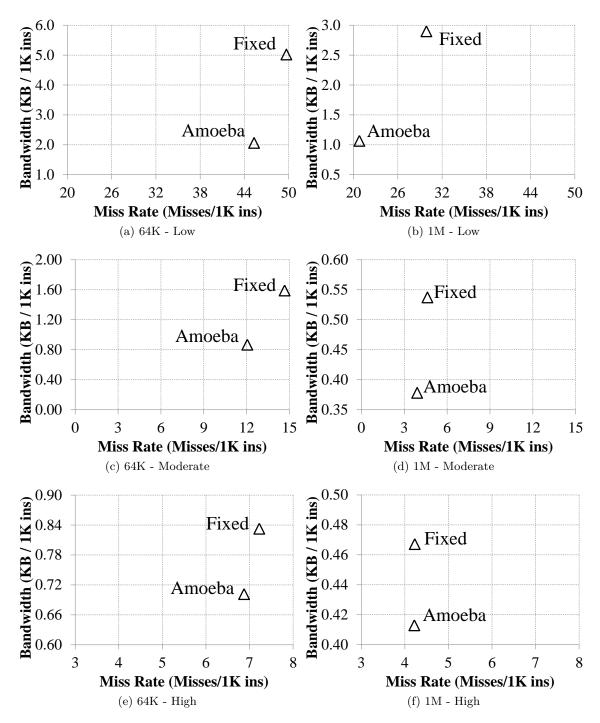

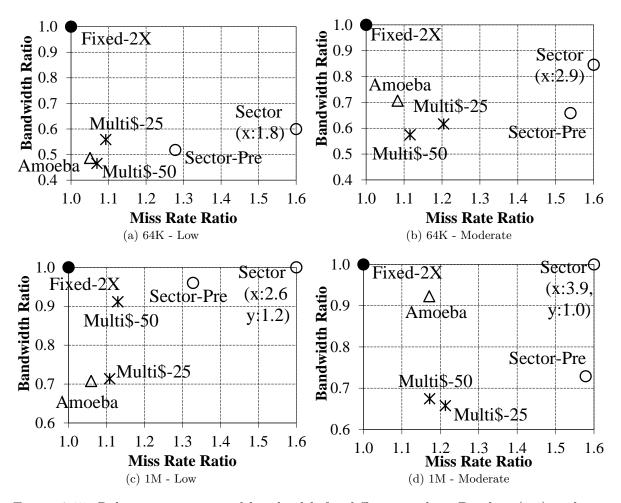

| Figure 6.3 | Bandwidth vs. Miss Rate. $(a)$ , $(c)$ , $(e)$ : $64K$ , $4$ -way L1. $(b)$ , $(d)$ , $(f)$ :                                     |     |

|            | 1M, 8-way LLC. Markers on the plot indicate cache block size. Note                                                                |     |

|            | the different scales for different groups                                                                                         | 99  |

| Figure 6.4 | Amoeba-Cache Architecture                                                                                                         | 100 |

| Figure 6.5 | Lookup Logic                                                                                                                      | 101 |

| Figure 6.6  | Partial Miss Handling. Upper: Identify relevant sub-blocks. Useful                         |     |

|-------------|--------------------------------------------------------------------------------------------|-----|

|             | for other cache controller events as well, e.g., recalls. Lower: Refill of                 |     |

|             | words and insertion                                                                        | 103 |

| Figure 6.7  | Amoeba Cache Controller (L1 level)                                                         | 104 |

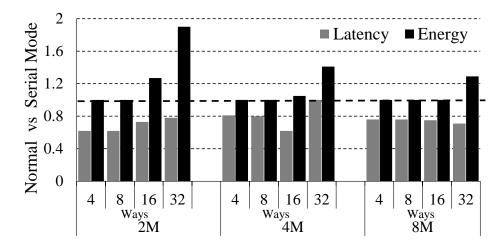

| Figure 6.8  | Serial vs Normal mode cache                                                                | 107 |

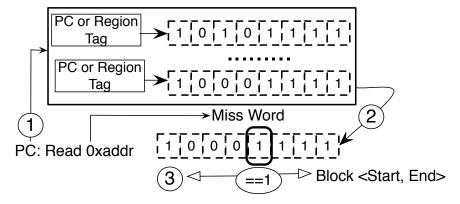

| Figure 6.9  | Spatial Predictor invoked on a <i>Amoeba-Cache</i> miss                                    | 109 |

| Figure 6.10 | Fixed vs. Amoeba (Bandwidth and Miss Rate). Note the different                             |     |

|             | scale for different application groups                                                     | 112 |

| Figure 6.11 | Distribution of cache line granularities in the 64K L1 and 1M L2                           |     |

|             | Amoeba-Cache. Avg. utilization is on top                                                   | 114 |

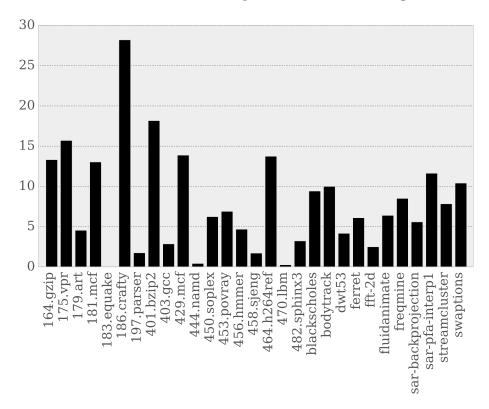

| Figure 6.12 | % improvement in performance and $%$ reduction in on-chip memory                           |     |

|             | hierarchy energy. Higher is better. Y-axis terminated to illustrate                        |     |

|             | bars clearly. Baseline: Fixed, 64K L1, 1M L2                                               | 115 |

| Figure 6.13 | Spatial Predictor Performance Comparison                                                   | 117 |

| Figure 6.14 | Effect of increase in block size from $64$ to $128$ bytes in a 1 MB cache                  | 120 |

| Figure 6.15 | Relative miss rate and bandwidth for different caches. Baseline (1,1)                      |     |

|             | is the Fixed-2x design. Labels:<br>$\bullet$ Fixed-2x,<br>$\circ$ Sector approaches.<br>*: |     |

|             | Multi\$, $\triangle$ Amoeba. (a),(b) 64K cache (c),(d) 1M cache. Note the                  |     |

|             | different Y-axis scale for each group                                                      | 122 |

| Figure 8.1  | % Reduction in IR Instructions                                                             | 130 |

### Chapter 1

# Introduction

Since the invention of the microprocessor, it is unlikely that the role of a computer architect has ever been as important as it is now. The breakdown of Dennard's scaling led to the multi-core revolution [57]. Mark Bohr, Intel Fellow and recipient of the IEEE Jun-ichi Nishizawa Medal [82], reflecting on the breakdown of Dennard scaling [25] stated –

... ours is a very inventive industry and new transistor technologies such as strained silicon, high-dielectrics, metal gates and multiple-gate devices have been or will be introduced to continue scaling. So although the letter of Dennard's Law can no longer be followed, it has gotten us very far over the past 30 years and the spirit is alive and well in transistor R&D facilities around the world.

As of 2016, the breakdown of Moore's Law seems inevitable [4]. This marks the second time computer architects are called upon to devise novel technologies that deliver performance improvements and reduced energy consumption. Arguably, it is even more challenging than the crisis faced at the onset of the 21st century.

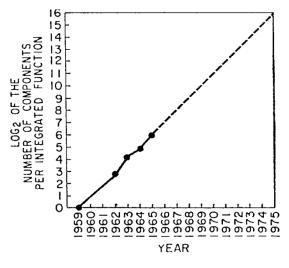

#### 1.1 The breakdown of technology scaling

Gordon Moore's seminal work in 1965 defined the law that governed semiconductor cost scaling for the next five decades. Primarily interested in shrinking transistor costs, Moore formulated the law based on empirical data presented in his paper. The plot which extrapolates the exponential transistor count increase as a function of time is reproduced in Figure 1.1. Based on the observations from 1959 to 1965, he predicted a doubling of the transistor count every  $\simeq 2$  years [122]. It is an impressive achievement of the semiconductor industry to have borne out five decades of scaling in accordance to Moore's law. The increased transistor count in each generation has been the primary driving force for increased computational efficiency.

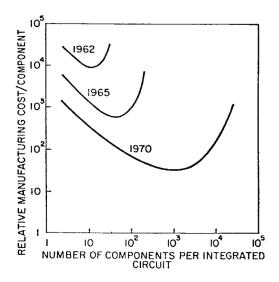

Furthermore Moore describes cost scaling as shown in Figure 1.2. Moore stated –

Figure 1.1: Moore's Law [122]

Figure 1.2: Moore's Cost Data [122]

"For simple circuits, the cost per component is nearly inversely proportional to the number of components, the result of the equivalent piece of semiconductor in the equivalent package containing more components. But as components are added, decreased yields more than compensate for the increased complexity, tending to raise the cost per component. Thus there is a minimum cost at any given time in the evolution of the technology." [122]

Moore observed that the overall cost is dependent on two factors: the density of transistors on a single chip and the reliability of the fabrication process. The reliability is also known as the *yield rate*. Increasing the number of transistors for a given area makes them cheaper; however it increases the chance of defects. The presence of fabrication process induced defects on wafers reduces yield rate and drives up cost. This net effect results in an optimal number of components per integrated circuit, as shown in Figure 1.2. To maintain fabrication cost scaling of microelectronics as described by Moore, two sizes need to be considered a) the wafer size and b) the transistor size. A single wafer contains multiple *dies*, small block of semiconducting material on which a functional circuit is etched. As of 2016, the current industry standard wafer is 300mm in diameter. A simple estimation of the number of processing dies per wafer for the Haswell 4 core configuration at 22nm is  $\simeq$  400 dies (not accounting for fabrication defects).

Larger wafers are preferred, as a fixed number of steps are required to produce a single wafer, and cost is amortized. Additionally, defects are often found on the edges which also favours larger wafers to improve yield. There have been efforts to move to a 450mm size wafer, and estimated use in volume production is projected to start in 2020.

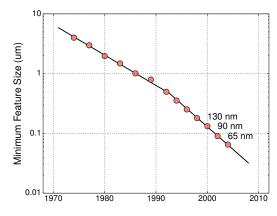

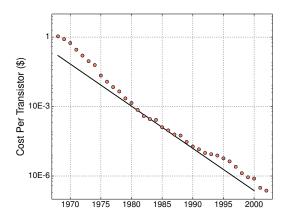

Figures 1.3 and 1.4 show the scaling of transistors in terms of a) size and b) cost from the year 1970 onwards. We can see that transistor sizes have scaled linearly on the log scale

Figure 1.3: Transistor Size Scaling [25]

Figure 1.4: Transistor Cost Scaling [123]

as shown in Figure 1.3. Similarly, the number of transistors has doubled every two years in this time frame. The cost has decreased from 1 transistor for \$1 in 1970 to  $10^6$  transistors for \$1 in 2000 due to advances in VLSI technology [123].

Dennard Scaling: Moore's scaling for cost motivates the need to make smaller transistors but it is Robert Dennard who outlined the implications of semiconductor scaling in 1974 [46]. In his work, Dennard showed that as transistors get smaller, they switch faster and use less power. Thus power density remains constant in spite of increased transistor density. This implies that smaller chips consume less power whereas similar sized chips could run faster. Dennard's scaling has set the roadmap for the semiconductor industry for each generation of process technology, with a concrete transistor scaling formula to move each generation forward. From the early 70's with the invention of the microprocessor till the early 2000's, improvements in computational efficiency were primarily afforded by Dennard Scaling [46]. With Dennard scaling, the computing industry reaped the benefits of improved silicon fabrication methodologies year on year. A 1000× improvement in performance has been realized since 1970. The scaling described a 30% reduction in transistor size every 18 months. Their area shrinks by 50% thus doubling transistor density. A commensurate 30% reduction in supply voltage is also necessary to maintain reliability. Thus transistor density doubles while reducing delay by 30%. The power consumption is reduced by 50%and energy by 65% [26]. Additionally, the larger number of available transistors contributed to micro-architectural innovations.

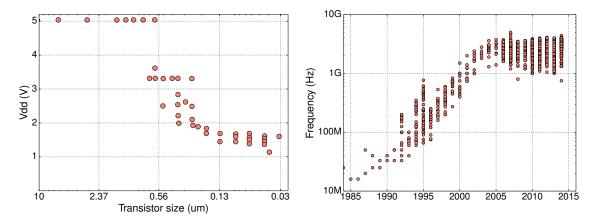

In the early 2000s the industry found that the current scaling trends showed increased power consumption inconsistent with the trend forecast by Dennard. While Dennard scaling projections for transistor feature sizes held, the chip supply voltage did not. This in turn made it difficult to provide economically viable cooling solutions to new power hungry chips. Figure 1.5 shows the how supply voltage scales with respect to transistor feature size. On reducing the feature size from  $0.13\,\mu\mathrm{m}$  to  $0.03\,\mu\mathrm{m}$  there has been little change in the supply

Figure 1.5: Voltage Scaling [44]

Figure 1.6: Frequency Scaling [44]

voltage. This manifests as a lack of threshold voltage (minimum gate-to-source voltage differential) scaling. Thus a significant amount of sub-threshold leakage current counts against the overall consumed power. The impact of this issue is reflected in Figure 1.6. The frequency of microprocessors reached a plateau in the early 2000s. In fact, even 15 years later, consumer Intel microprocessors are clocked in the 2.4-3.4 GHz range similar to their Pentium 4 microprocessor released in 2004 (Prescott).

Smarter utilization of silicon is imperative with the growing menace of the *Utilization Wall* [171]. The utilization wall is a consequence of CMOS scaling theory and current-day technology constraints, assuming fixed power and chip area. In 2010, researchers showed that less than 7% of the chip can be utilized in order to maintain power consumption below 80W. Should the entire chip be use, using the 45nm TSMC process, a staggering 1225W of power is consumed! The consequence of the utilization wall is *dark silicon*, silicon that cannot be powered-on at the operating voltage for a given thermal design power (TDP) constraint.

Implications of technology scaling breakdown: Dark silicon is not a new phenomenon. Rather the rapid increase,  $2\times$  per process generation, is the cause for concern. There is often circuitry available on the chip which is not used by all workloads. A simple example is the presence of hardware floating point units which are not used by the linux kernel [109]. To mitigate dark silicon, four approaches have emerged as potential candidates [166]. The first approach is to shrink the size of the chip itself. Compromising on performance to decrease the size of the chip is a non sequitur for chipmakers. The second approach is to wait for a breakthrough in semiconductor devices. Two candidates are Tunnel Field Effect Transistors (TFETS) [84], and Nano-Electro-Mechanical switches [41, 35]. Both of them hint at orders-of-magnitude improvements in leakage power consumption, but remain to be realized as economic alternatives. The third approach is increased usage of dim silicon, general purpose logic which is underclocked or used infrequently to meet the

constrained power budget. This introduces heterogeneity in the chip and has been explored by chipmakers. For example, NVidia used a "low power companion core" in the Tegra architecture [168]. While this approach counters the utilization wall, it is not a measure targeted at increasing performance. The final approach is the usage of *specialized* circuitry. This approach can provide much faster performance, much lower energy consumption or even both [171, 70]. The dark silicon is used to implement specialized co-processors. Execution migrates to a particular co-processor while power and clock gating the primary core. As of 2016, an increasing number of chips are dominated by specialized co-processors [66].

With the migration of execution across the chip, data movement becomes an additional cause for concern in specialized architectures. Using dedicated wires have long been deprecated in favour of on-chip networks [148, 43]. Published research by Intel in 2004 showed up to 50% of the dynamic power consumption in their microprocessor can be attributed to the network-on-chip (NOC) [112] The 80-core Intel TERAFLOPs chip expends 39% of the dynamic power per node in the NOC [75]. In the current generation, often the energy cost of data movement is as high as the computation itself leading to significant overheads in dynamic power consumption [11, 42]. In effect, wires have not scaled in power consumption with respect to the rest of the system.

To summarize, the implications of the breakdown of technology scaling are

#### 1. Favouring *specialization* to increase performance/watt

Hardware specialization is the use of circuitry or mechanisms which target a particular pattern in a workload. With knowledge of the pattern, a hardware specialized unit can provide faster performance and/or energy efficient execution. For example, vector units (SIMD) optimize for data parallel code segments within a program. With the transistors afforded by Moore's law scaling, multiple patterns can be targeted by different specialized units. We see this trend in modern, low power processors where more than 50% of the chip area is dedicated to specialized co-processors [66].

#### 2. Optimizing for data movement is necessary:

Von-Neumann architectures fetch data from memory to perform computation. However, due to deep memory hierarchies and increased efficiency for compute operations, a significant part of the dynamic energy consumption within a chip is due to the movement of data. Eliminating waste or unused data can reduce overall energy consumption, particularly in the memory hierarchy. With the use of specialized compute units, the problem is aggravated. Compute units consume less energy while data movement is increased as the execution of the workload migrates across the chip to utilize varied specialized hardware units.

#### 1.2 Challenges

The use of specialized co-processors introduces three significant challenges.

What to specialize? Figuring out the target for specialization within a large workload can be a daunting task. Computer architects often use dynamic profilers to identify important functions. Profilers such as gprof [65] can identify the fraction of execution time consumed by each function. However, their insights are tied to a particular architecture and yield no information about the amenability for specialization.

Domain experts can be consulted to provide insight to the engineers as to which segments of an algorithm are amenable to specialization. This implies a large investment in time and money for the industry. Researchers have proposed the use of standardized kernels to study specialization [142]. However, it relies on manual culling of kernels and may not be representative of complicated real work workloads. Prior work focused on specialized co-processors [64, 127, 39, 68] have obliquely addressed this problem. Unfortunately, the regions of interest selected by the authors for specialization is constrained by their accelerator micro-architecture. Considerations regarding the amenability and profitability of selected regions further complicate the issue.

How to specialize? Often there is no clear distinction in prior works between what to specialize and how to specialize. For example, the DySER [64] and CCA [39] architectures target computation only in their specialized regions. Thus their choice of what to specialize is constrained by their specialized architecture, i.e. how to specialize. There is a lack of research into how a target region should be specialized. This is exacerbated by the focus on irregular, general purpose applications with the focus on specialization to improve performance and energy efficiency.

High level synthesis tools such as LegUp [32], Bambu [134] and Vivado [52] require programmer annotations at the function level to identify the region to be specialized. Additional hints may be inferred by the usage of the function. Parallel invocation of the specialized unit can be derived from the use of the identified function in the pthread [126] (POSIX thread) programming model.

Integration Introducing heterogeneity in the system introduces additional challenges. In this thesis we study the challenge of data movement introduced by the integration of specialized units. Traditional methods of transferring data to specialized co-processors employ direct memory access (DMA). Initializing such transfers introduce delays. The performance obtained from the specialized unit must amortize the setup costs. Newer architectures such as the Intel HARP, Xilinx Zynq and Altera Cyclone, allow closer integration of reconfigurable accelerators. They add FPGAs on the same chip which have coherent access to the cache

memory hierarchy. Close integration allows for the use of "pull" based coherence protocols as opposed to "push" based DMA transfers.

#### 1.3 Approach

This dissertation adopts generalized methods to address the challenges of application specific hardware specialization. In this section we introduce terminology and techniques used in this thesis. We discuss how the work presented in this dissertation leverages existing techniques and builds upon them.

#### We use program analysis driven workload characterization

Program analysis can be defined as –

... the process of automatically analyzing the behavior of computer programs regarding a property such as correctness, robustness, safety and liveness. [179]

Software engineering disciplines have established varied program analysis techniques to address primarily issues related to program optimization or program correctness. We use program analysis to identify frequently executed code segments for further characterization. The workloads we study are programs which are representative of a group programs. They serve as benchmarks for computing systems and are crucial for performance engineering. Herein we describe our approach and rationale.

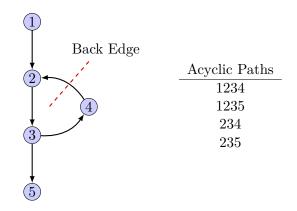

Program analysis can be *static* or *dynamic* in nature. Static program analysis is performed without executing the program, for example at compile time. Dynamic analysis is performed at runtime. We implement *efficient path profiling* [15, 13]. A path can be loosely defined as an acyclic sequence of basic blocks. A basic block is a sequence of instructions terminated by a branch. A more precise description is provided in section 3.2.1. In the work presented in chapter 3 we adopt a hybrid approach. We use *dynamic* path profiling to identify the "hot" paths in the program. We use *static* reconstruction of the hot paths for characterization. The characterization serves as a first order metric for assessing the amenability of the regions with respect to specialization.

The rationale behind our approach is the need for scalability. Prior works such as [151, 76] have adopted fine-grained instruction granularity profiling to characterize workloads. We find that these approaches impose a high runtime overhead. In contrast, our approach imposes a 30-40% overhead at runtime with no loss of control flow information. The low overhead and granularity of abstraction allows our approach to be flexible. The bane of dynamic analysis is input dependence. With dynamic analyses we can derive properties of programs observed for a particular input. Dynamic analysis cannot prove that a particular program satisfies a certain property [14]. However, using our approach we can mitigate the impact of input dependence by aggregating profiles collected for different inputs. We

study the program behavior across a set of representative inputs rather than a single one. The static reconstruction for characterization is fast, on the order of 10s of seconds for our largest workloads.

We target specialized units, i.e. "accelerators" With the breakdown of technology scaling, computer architects have resorted to the use of specialized units, i.e. accelerators to provide increased performance and energy efficiency. An accelerator is any unit tailored to optimize execution for a particular program pattern. For example, vector extensions (SIMD) to the x86 ISA serve to accelerate data parallel program segments. Thus accelerators can be broadly defined as any specialized circuitry which targets particular program characteristics. SIMD and floating point units can be classified as programmable accelerators. The research presented in chapters 3 and 3 focuses on reconfigurable accelerators. Reconfigurable accelerators can be Coarse Grain Reconfigurable Arrays [45], or Field Programmable Gate Arrays [28]. Reconfigurable accelerators that stem from academia such as DySER [64], CCA [39] and BERET [68] can also leverage our work.

We define program abstractions for accelerators Program abstractions are essential for scalable techniques be developed. For example, a function is an abstraction a programmer may use to group code which serves a singular purpose. Similarly, abstractions such as the control flow graph and program dependence graph [54] offer representations on which analyses can be performed. In this thesis (chapter 4) we describe a program abstraction, ("Braid", Section 4.4.2) to target for specialization. This abstraction builds upon program paths. It merges paths which start and end at the same basic block. Paths which contain features that are not supported on accelerators are left to execute on the host. We use a software based speculative execution model as the basis for the abstraction.

Speculative execution is a technique by which the microprocessor executes instructions past a branch without knowing the outcome of the branch. Effective hardware speculation is enabled by accurate branch predictors. Paths are composed of basic blocks spanning across several branches at a time. Executing a path at a time speculates on all the branches in the path. Merging paths to construct "Braids" speculates on branches which are never taken for the profiling input. Hardware speculation includes support for rolling back changes to program state if the wrong path is executed. We construct software "frames" that include instrumentation for checkpointing state. Our implementation of software speculation eliminates branches, reduces control flow complexity and provides software support for rollback in case of wrong path execution. More details are provided in section 4.5.

We propose coherence protocols for accelerators Coherence protocols allow shared memory multiprocessors to have a synchronized view of memory. Updates issued from a processor are propagated to all processors which access the same datum. Coherence protocols enforce the contract established by the consistency model [162]. Data movement in accelerators have traditionally used non-coherent interfaces such as direct memory access (DMA). These require manual effort for the programmer to restructure the code so that data can be shipped to the accelerator for processing and then back again. This type of interface also has a high overhead; thus the accelerator must perform a significant amount of cost to amortize the cost of data transfer. This type of model is also referred to as a "push" based model. We design coherence protocols for accelerators, which allow for a "pull" based model. Accelerators are allowed to request for and cache data exclusively in our proposed protocol. We mitigate the overheads of data movement by using a specialized coherence protocol for accelerators.

We describe mechanisms for adaptive granularity caching Caching mechanisms in modern processors save data at a fixed granularity. Modern consumer microprocessor's cache data at the 64B or 32B granularity [44]. However, the design decisions for cache line sizes do not take into account the memory access behavior of modern workloads. Prior researchers [141, 150] have looked at caches which support block sizes of varied size. Our approach detailed in chapter 6 allows for variable sized cache blocks in multiples of 8B in size.

#### 1.4 Dissertation Organisation

With the breakdown of technology scaling, computer architects have resorted to specialization as a means to provide the scaling in performance and energy benefits consumers have experienced since the invention of the microprocessor. The overarching theme of this dissertation addresses the challenges of application specific hardware specialization. The underlying motifs of the work presented in this dissertation are automation and generality. The tools and techniques are application agnostic and operate via automated compiler analyses or via transparent hardware mechanisms.

Chapter 2 discusses the current challenges faced by computer architects with the breakdown of transistor scaling. It puts the new challenge of harnessing specialized units in contrast to the dawn of the multi-core era in computing. Section 2.2 enumerates the challenges of what to specialize, how to specialize and integration issues. Section 2.3 lists the contributions made and finally, section 2.4 discusses the relationship of thesis content to prior peer reviewed published work.

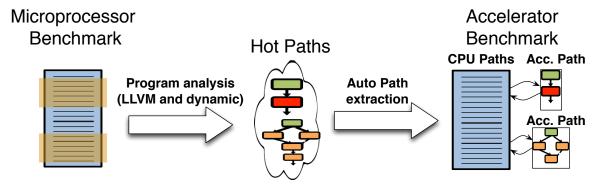

Chapter 3 describes our work on extracting accelerator benchmarks from microprocessor benchmarks. We show the scalability and precision of analysis at the granularity of program paths. We present our characterization of workloads drawn from established microprocessor benchmark suites. In this chapter we present our approach to address the challenge of what to specialize. Section 3.2.1 provides a primer on path profiling and motivates its use

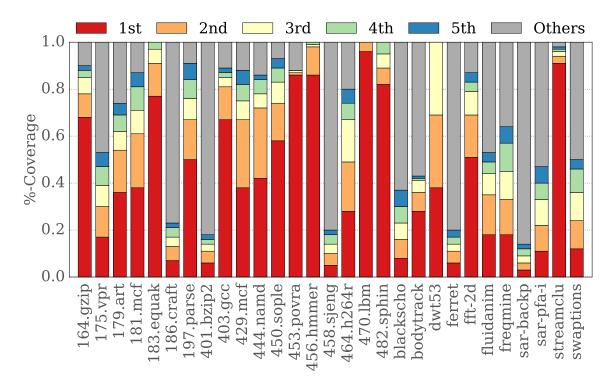

as an abstraction for characterization with the end goal of specialization. We study of 29 workloads drawn from prevalent microprocessor benchmark suites. Sections 3.3 and 3.4 present the data collected and discuss the implications on specialization.

Chapter 4 builds upon the path based characterization to demonstrate the feasibility of path based specialization in terms of performance and energy efficiency. Building upon paths, we describe a new abstraction for hardware specialization called "Braids". We evaluate and discuss the opportunities of leveraging Braids for hardware specialization. In this chapter we present our approach to address the challenge of how to specialize. Section 4.2 discusses related work showing how heuristic based approaches tailored for VLIW processors may fail when reused as specialization targets. Section 4.4.2 presents our methodology for the construction of "Braids". We describe the construction of speculative software frames in Section 4.5. We model the performance and energy implications of specialization for the abstractions described. We present our results in section 4.6.

Chapters 5 and 6 tackle the challenge of *integration*. We study issues with respect to data movement. We discuss coherence protocols tailored for specialized hardware. They allow for low overhead data movement as execution of the workload migrates across the host and the accelerators. Section 5.3 describes the hybrid coherence protocol. We develop a cycle accurate simulator to study the impact of using time stamp based coherence within the accelerator domain. Section 5.5 presents our results showing the reduced energy consumption for data movement in the workloads we study. We also study the utilization of cache lines based on workload behaviour. We look at the amount of data accessed by the processor while the line is cached. We describe an adaptive granularity cache memory hierarchy in section 6.3. We evaluate two dynamic predictors and present the results we observe across a diverse set of workloads including desktop applications such as Firefox. The results are presented in section 6.6.

Chapter 7 outlines the software developed to conduct the research presented herein. Finally, chapter 8 presents concluding thoughts and directions for future work.

### Chapter 2

# Background

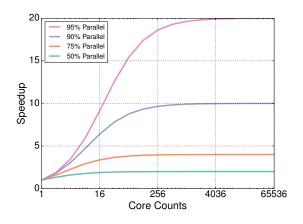

In 2006, the industry shifted focus to shared memory multiprocessing as a means to scale computational throughput, marking the end of Dennard scaling. Shared memory multiprocessing was proposed in academia as early as 1996 [71] and well studied. Figure 2.1 shows the maximum possible speedup given what fraction of the program can be executed in parallel. The curves represent the parallel fraction and even the largest depicted in the graph (95\% parallel) plateau after 256 cores. A more realistic 50-75\% parallel fraction benefits very little overall with more than 16 cores. The shift to a parallel paradigm for consumer applications brought along with it a whole host of issues. Developers long accustomed to reasoning about sequential execution now have to deal with more complex multi-threaded code to extract performance from the hardware provided. In work by Blake et al. [23] available thread level parallelism in desktop applications was studied. Their exhaustive analysis across a wide range of applications such as gaming, office, web browsing and more showed little available thread level parallelism (TLP) that can be exploited for improved performance within a workload. For instance they found that for office, gaming and web browsing the average TLP was 1.2, 1.6 and 2 respectively. Only video processing applications showed the need for many cores with an average TLP of 7.4.

High Performance Computing (HPC) applications are often data parallel problems. In the effort to extract performance, GPUs have been repurposed to accelerate HPC workloads. This paradigm represents the extreme end of the TLP spectrum using many parallel yet simple processors that maintain a *Thermal Dissipation Power* close to a general purpose core. Their use however is via tailored programming models such as CUDA or OpenCL, thus requiring a rewrite of existing programs to take advantage of their processing power.

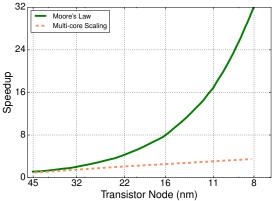

Figure 2.2 shows the stark contrast between Moore's law scaling and actual multi-core scaling as overall application speedup. While multi-core scaling has utilized the transistors afforded by Moore's law, it is infeasible to sustain with transistor feature sizes reaching single digits. At that nanometer scale, transistor sizes are comparable to a few atoms. Until late 2016, Intel followed the "Tick-Tock", two stage model of micro-architecture updates. A

Figure 2.1: Amdahl's Projection [6]

Figure 2.2: Multicore Scaling [49]

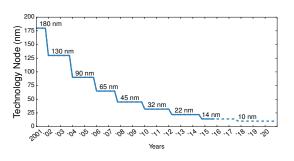

"Tick" in the model, represented a shift to a smaller process technology whereas a "Tock" represented a change in the micro-architecture design. Figure 2.3 shows the fabrication process used by Intel over the years and their projected usage. Reliability and yield at such small feature sizes has forced Intel to abandon the two stage "Tick-Tock" model in 2016. Going forward, Intel has announced the introduction of a second "Tock" which focuses on the optimization of the micro-architecture introduced previously.

0.1 2005 2007 2009 2011 2013 2015 2017

Figure 2.3: Intel Tick [7, 147]

Figure 2.4: Cost/Transistor stops scaling [149]

The semiconductor industry has largely been affected by the increase in costs of research required for next generation semiconducting fabs (fabrication facilities). For example, FinFET technology allows for smaller feature sizes but requires more fabrication steps and supporting tools. This has forced many semiconductor companies to become "fab-less", i.e. they only provide the design and rely on other manufacturers to realize the design at a desired technology node. Larger wafer size can lower fabrication costs by increasing the number of dies per wafer and providing better yields. However, as mentioned previously, wafer sizes are not expected to change until 2020 due to the significant investment required to upgrade fab lines.

Figure 2.4 (data from NVidia), shows the cost of transistors for different technology nodes. It shows limited cost benefit after scaling past the 28nm technology node (curves normalized to 28nm). Smaller feature sizes will no longer provide an economic benefit for

fab-less semiconductor companies. This heralds the end of economic scaling and thus the breakdown of Moore's Law.

Scaling via specialization: With the imminent collapse of Moore's Law scaling, the semiconductor industry has begun efforts to compensate. Without either Dennard or Moore's scaling, there is a risk that the industry will stagnate. While a driving force for consolidation, i.e fewer companies can afford fabs, it also leads to increased research in technologies which offer more scaling at the micro-architecture level. It is expected that companies will increasingly adopt solutions which provide performance by the use of innovative hardware architectures. One such example is the success of the GPGPU computation. The massively parallel processing power of the GPU can only be harnessed by a specific programming model coupled with the target architecture. Furthermore, application and domain-specific accelerators become more attractive as it is able to provide the performance improvement no longer provided by device technology scaling, i.e increase in transistor density.

Figure 2.5: Performance increase more than technology scaling [44]

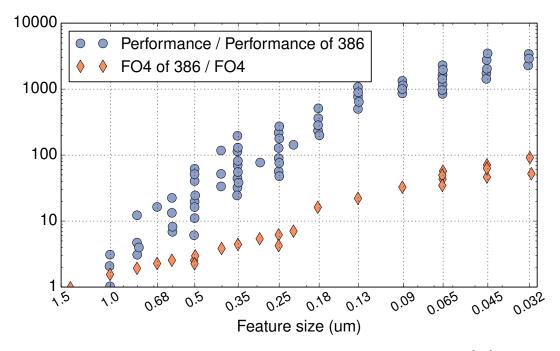

Figure 2.5 shows the normalized performance of microprocessors since Intel's 80386. Blue circles indicate normalized overall performance while the orange diamonds indicate the FO4 delay. The FO4 delay (process-dependent delay metric used in digital CMOS technologies) serves as a proxy for Dennard's transistor performance scaling. From the trends indicated on the graph, we see that the actual performance improvement outstrips the predicted performance from Dennard's scaling law. A significant amount of performance improvement is afforded by micro-architecture innovations, also known as architectural scaling. Computer architects have put the extra transistors afforded by Moore's law to use

in the design of subsystems such as superscalar and out-of-order (OOO) execution, cache memory hierarchies and specialized units such as vector extensions. These improvements target different characteristics of modern workloads such as the presence of instruction level parallelism (ILP) using superscalar and OOO execution. Data level parallelism is targeted using Single Instruction Multiple Data (SIMD) units, which introduce vector extensions to the ISA which the compiler or programmer can use while implementing their algorithms. These are fundamental advances which have provided performance increase over and above device scaling. In the future, computer architects may have to work with the assumption that no performance improvements will be from device scaling, and it is architectural scaling which carries the burden. As the blue squares show how processor performance scaled over time, the orange diamonds indicate how much of it came from device scaling. This graph is derived from [44]. Overall, the figure indicates the need for an order of magnitude improvement to be derived from architectural scaling due to the loss of device scaling.

#### 2.1 Application Specific Hardware Specialization

Hardware accelerators are increasingly being adopted to mitigate the loss of device scaling. The term accelerator is loosely defined and alludes to any specialized architecture which provides a performance and/or energy efficiency benefit when compared to execution on a general purpose CPU. For specialized circuitry, often orders of magnitude greater performance can be obtained as indicated by research presented in [185, 70]. Compared to general-purpose processors, customized processors like DSPs deliver from  $10 \times$  to  $100 \times$  more energy efficiency, while dedicated application-specific accelerators (ASICs) are  $1000 \times$  more energy efficient [185].

Customized architectures composed of CPUs, GPUs, and accelerators are already seen in mobile systems and are beginning to emerge in servers and desktops. Analysis of die photos from three generations of Apple's SoCs: A6 (iPhone 5), A7 (iPhone 5S), and A8 (iPhone 6), shows that more than half of the die area is dedicated to non-CPU, non-GPU blocks Most of these blocks are application-specific hardware accelerators. Customized hardware accelerators, implemented as application specific integrated circuits (ASICs) efficiently perform key kernel computations within larger applications. However, flexibility is sacrificed. After fabrication, an ASIC's custom datapath cannot be modified to meet new requirements. ASICs also have high non-recurring engineering (NRE) costs associated with manufacturing and long development cycles.

Heterogeneous systems combine general purpose processing cores with diverse characteristics. Architectures such as the ARM big.LITTLE target energy efficient execution based on workload characteristics. They target sequential sections of code with large OOO cores which can extract finer grain ILP. Many small cores are used for parallel portions of the workload as indicated by the programmer. Additionally, GPGPU accelerators have become

ubiquitous. Modern artificial intelligence methods have become increasingly reliant on neural architectures. Neural architectures are data parallel with a large amount of floating point computations. NVidia has made great strides in tailored GPGPU accelerators for neural networks.

A radical approach to the heterogeneous system model is the integration of reconfigurable FPGAs. IBM has developed CAPI (Coherent Accelerator Peripheral Interface) for the Power8 architecture. This allows for the addition of reconfigurable FPGA based accelerators over PCIe with ease. The CAPI model allows for shared virtual memory between the accelerator and the host without complicated DMA transfers. Intel has announced plans to release a Xeon server with an FPGA on chip (HARP). The Intel HARP project arises from the Altera's acquisition by Intel. It allows for even tighter integration of accelerators with the CPU. The HARP architecture utilizes QPI (Intel Quick Path Interconnect) to access the FPGA. The FPGA accelerator is also provided coherent access to memory. Similar SoCs have been previously developed by Altera and Xilinx which couple ARM cores with FPGAs on a coherent interconnect via the ACP (Accelerator Coherence Port).

While academia has explored coarse grain reconfigurable architectures (CGRAs) practical reconfigurable accelerators available today are primarily FPGAs. FPGAs allow engineers to design custom circuitry after manufacturing. FPGAs are configured using a hardware description language such as Verilog. They contain arrays of programmable logic blocks and interconnects to route data. Historically, FPGAs were primarily used in telecommunications and networking. In recent times, they are found everywhere from the automobiles to mobile phones. The primary benefit of a hardware accelerator is the elimination of core frontend costs incurred in a traditional OOO processor. Research indicates that the more than 40% of the power consumption in an OOO frontend is due to instruction fetch and control, considering pipeline registers as well this can be as high as 60% [70]. The energy consumed in the execution per operation is also generally lower than that of an OOO core. Furthermore there are many optimizations available such as the bitwidth reduction and fusion of operations when targeting an FPGA.

#### 2.2 Challenges

With the flexibility afforded by reconfigurable FPGA accelerators come a host of challenges which need to be addressed to extract performance while retaining the energy benefits of specialized computation. In this section we enumerate and outline the challenges of harnessing hardware accelerators.

#### 2.2.1 Challenge 1: What to specialize?

The foremost challenge is what should developers target for specialization? For the most part engineers have relied on domain experts to indicate what parts of an algorithm are

beneficial and amenable. This has been the de facto approach where a large non-recurring investment is made in terms of man-hours to understand and rewrite the algorithm to target a particular FPGA accelerator. Often such an effort will consist of multi-person teams over a project which lasts a few months. However, with the pressing need for more workloads to be accelerated, few companies can afford such a long turn around time on accelerator synthesis. An additional concern is the rate of evolution of the algorithm itself. This particular concern was discussed at length when Microsoft offloaded part of their machine learning for Bing search to FPGAs (Catapult [137]). Rapid evolution of the algorithm meant that the hardware design often lagged behind the software implementation. The inherent challenge is to eliminate the reliance on expert guidance while building accelerators. To address the question of what to specialize, two aspects must be taken into consideration.

- a) Amenability FPGA accelerators are not yet first class citizens in the SoC. There are many operations with well defined semantics on CPUs which are undefined on FPGAs. A simple example is the usage of exceptions. While software has well defined interfaces to halt and deal with exceptions, such support is not present on the FPGA. Furthermore, whether such a construct is feasible to implement on an FPGA is questionable. There are more examples such as dynamic memory allocation, runtime shared library invocation, etc which software developers take for granted but are difficult to mimic on an FPGA. Thus existing implementations of algorithms cannot be blindly used as templates to generate FPGA accelerators. The standard approach to understand what parts of the algorithm are amenable is to refer to an expert. Engineers often use statistical profilers (eg. gprof) to understand which parts of a program consume the largest amount of time. With this information they can then dissect the program to separate out the parts which are amenable from those that are not. For automated analyses, the key to assessing amenability is the choice of abstraction. Having a robust abstraction which represents the workload at a fine granularity lends scalability to automated analyses.

- b) Profitability The second and arguably more critical aspect of what to accelerate is to assess the profitability of offloading computation to a target accelerator. There are inherent overheads to any heterogeneous execution model when execution migrates from one substrate to another. For example, the overheads of kickstarting computation on an FPGA need to be understood in order to assess profitability. Often, benefits of fine grained acceleration can be nullified by associated overheads. The overheads themselves can be categorised as system dependent and workload dependent. System dependent overheads are those which are inherent to the offload model adopted by the SoC. For example, IBM CAPI simplifies the address translation and memory interface but latency of each access is in the order of 1000s of CPU cycles due to the PCIe interconnect. SoCs from Altera and Xilinx do not offer address translation but do have coherent access to the last level of cache in the

order of 20-50 cycles. Finally the key to understanding the workload overheads is the use of a proper abstraction. Given an abstraction, automated analyses can model the potential gain from offloading work to the accelerator.

#### 2.2.2 Challenge 2: How to specialize?

It is imperative that we clearly distinguish the *how* from the *what*. It is easy to redefine *what* based on *how* a particular algorithm is accelerated. To demonstrate this potential pitfall, consider the following example. If a high level synthesis tool does not support dynamic memory allocation, it may discard any program region which has such operations. Thus the inability of an automated tool to target operations to run on an FPGA may determine what should be targeted at a coarser granularity. Once again the selection of a proper abstraction is paramount to achieving a clean partitioning of program regions to offload to a reconfigurable accelerator.

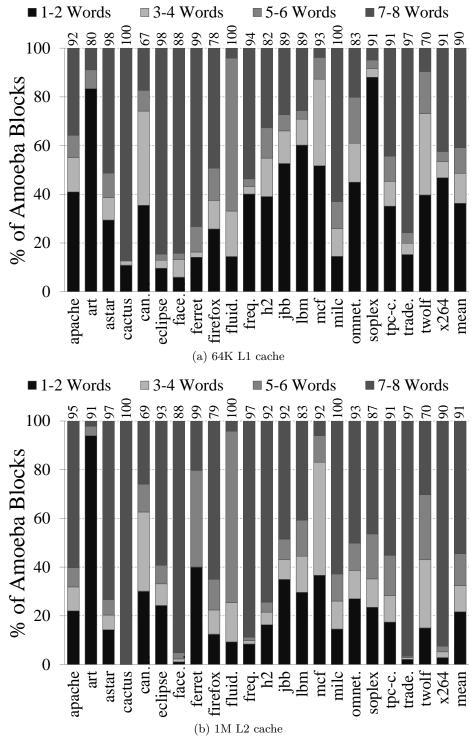

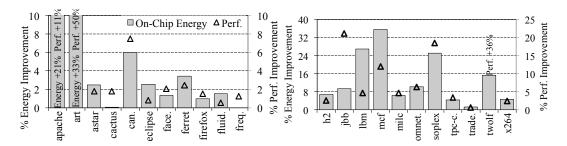

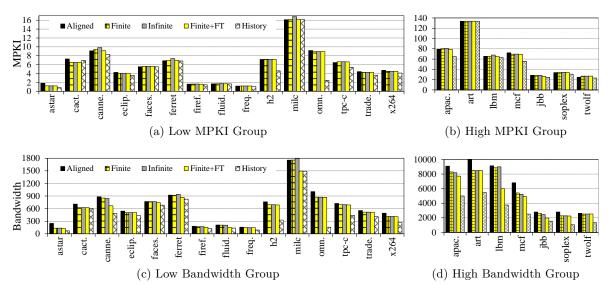

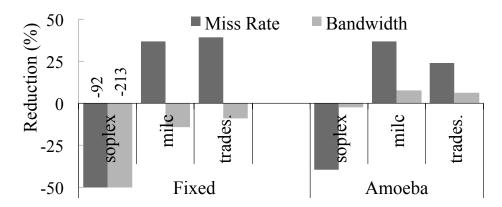

- a) Compiler Analysis There is a paucity of research on appropriate abstractions that allow for flexible representations of work to be offloaded to a target accelerator. Prior work such as Spatial Computation [29] and BERET [68] have repurposed Hyperblocks [114] and Superblocks [117] respectively. Both these abstractions were originally designed for VLIW processors. Often these heuristic based abstractions yield poor results. See Section 4.2.2 for more details. Meanwhile standard compiler research has made great progress. There are many robust building blocks available to the developer to work with. Yet, there are no techniques that target accelerators which take advantage of recent advances in compiler techniques and program analysis. Another potential application of compiler analyses is the detection of coarse grain parallelism. All the tools available rely on programmer annotations such as OpenMP pragmas or pthread invocations. There is a rich body of auto parallelization compiler analyses [57, 86, 103] which can be leveraged for the detection of coarse grain parallelism.