### Asymmetric Coherent Configurable Caches for PolyBlaze Multicore Processor

by

Ziaeddin Jalali B.Sc., Sharif University of Technology, 2010

### THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

In the

School of Engineering Science

© Ziaeddin Jalali 2015 SIMON FRASER UNIVERSITY Fall 2014

All rights reserved. However, in accordance with the Copyright Act of Canada, this work may be reproduced, without authorization, under the conditions for Fair Dealing. Therefore, limited reproduction of this work for the purposes of private study, research, criticism, review, and news reporting is likely to be in accordance with the law, particularly if cited appropriately.

## APPROVAL

| Name:                | Ziaeddin Jalali                                                                                                 |

|----------------------|-----------------------------------------------------------------------------------------------------------------|

| Degree:              | Master of Applied Science                                                                                       |

| Title of Thesis:     | Asymmetric Coherent Configurable Caches for Poly-Blaze Multicore Processor                                      |

| Examining Committee: | <b>Dr. Ivan Bajic</b><br>Associate Professor, School of Engineering Science<br>Chair                            |

|                      | <b>Dr. Lesley Shannon, P.Eng.</b><br>Associate Professor, School of Engineering<br>Science<br>Senior Supervisor |

|                      | <b>Dr. Alexandra Fedorova</b><br>Associate Professor, School of Computing<br>Science<br>Supervisor              |

|                      | <b>Dr. Fabio Campi</b><br>Lecturer, School of Engineering Science<br>Internal Examiner                          |

Date Defended:

28 November 2014\_\_\_\_\_

### **Partial Copyright Licence**

The author, whose copyright is declared on the title page of this work, has granted to Simon Fraser University the non-exclusive, royalty-free right to include a digital copy of this thesis, project or extended essay[s] and associated supplemental files ("Work") (title[s] below) in Summit, the Institutional Research Repository at SFU. SFU may also make copies of the Work for purposes of a scholarly or research nature; for users of the SFU Library; or in response to a request from another library, or educational institution, on SFU's own behalf or for one of its users. Distribution may be in any form.

The author has further agreed that SFU may keep more than one copy of the Work for purposes of back-up and security; and that SFU may, without changing the content, translate, if technically possible, the Work to any medium or format for the purpose of preserving the Work and facilitating the exercise of SFU's rights under this licence.

It is understood that copying, publication, or public performance of the Work for commercial purposes shall not be allowed without the author's written permission.

While granting the above uses to SFU, the author retains copyright ownership and moral rights in the Work, and may deal with the copyright in the Work in any way consistent with the terms of this licence, including the right to change the Work for subsequent purposes, including editing and publishing the Work in whole or in part, and licensing the content to other parties as the author may desire.

The author represents and warrants that he/she has the right to grant the rights contained in this licence and that the Work does not, to the best of the author's knowledge, infringe upon anyone's copyright. The author has obtained written copyright permission, where required, for the use of any third-party copyrighted material contained in the Work. The author represents and warrants that the Work is his/her own original work and that he/she has not previously assigned or relinquished the rights conferred in this licence.

Simon Fraser University Library Burnaby, British Columbia, Canada

revised Fall 2013

## Abstract

Modern computing systems gain performance by several means such as increased parallelism through using Chip-level Multiprocessor (CMP) systems. Symmetric Multiprocessor (SMP) systems use uniform processing cores to form a CMP in which all cores are identical in every aspect. Conversely, Asymmetric Multiprocessor (AMP) systems consist of processing cores with variable configurations such as different cache configurations, co-processors, and cache sizes. AMP systems coupled with such smart scheduling algorithms can improve resource utilization while maintaining overall system performance because real-time profiling in a computing system using light-weight hardware profilers can help smart scheduling algorithms make meaningful decisions. In other words, the vision into an application's behavior helps in the decision making process on how to allocate available resources for different applications without penalizing the performance by putting too much overhead on the system. Currently, there is no AMP research framework available that allows us to look into asymmetry in processing systems.

In this thesis, we present an extension on PolyBlaze framework for asymmetric coherent Level-1 (L1) caches. Our implementation in this work includes other arbiter and prefetching units as well. We measure data cache read miss rates and application run-times for select benchmarks from SPEC CPU2006 executed in a Linux environment on top of a variety of cache configurations. In the scope of this work, we manually assign applications to cores to take advantage of AMP configurations. Our results show that in a AMP system, different applications can benefit from various configurations to complete their work faster using less resources. To Yasaman.

## Acknowledgments

First, I would like to thank my supervisor, Dr. Lesley Shannon who patiently provided me guidance, support, and encouragement, particularly when the project was not going well. My main takings from this degree are the many lessons I learned from her.

Additionally, I would like to thank Dr. Alexandra Fedorova, Dr. Fabio Campi, and Dr. Ivan Bajic for serving on my defense committee.

Also, I want to thank my friends and colleagues in the RCL lab, especially Eric Matthews and Nicholas Doyle who helped, supported and answered my many questions. I had the most wonderful time there.

Finally, to my lovely wife, Yasaman, and my parents whose support throughout this journey was priceless. I will never be able to thank you enough.

## Contents

1

| Approval                  | ii  |

|---------------------------|-----|

| Partial Copyright License | iii |

| Abstract                  | iv  |

| Dedication                | v   |

| Acknowledgments           | vi  |

| Contents                  | vii |

| List of Tables            | x   |

| List of Figures           | xi  |

| Glossary                  | xv  |

| Introduction              | 1   |

| 1.1 Motivation            | 2   |

| 1.2 Objective             | 3   |

| 1.3 Contributions         | 3   |

| 1.4 Thesis Organization   | 4   |

| 2 | Ba                     | ckgro        | ound and Related Work                       | 5    |  |  |  |  |

|---|------------------------|--------------|---------------------------------------------|------|--|--|--|--|

|   | 2.1                    | Mult         | ticore Computer Architecture                | 6    |  |  |  |  |

|   |                        | 2.1.1        | Memory and Cache Coherence                  | 8    |  |  |  |  |

|   | 2.2                    | Soft         | Processors and Processor Emulators          | 10   |  |  |  |  |

|   | 2.3                    | Poly         | 'Blaze                                      | 13   |  |  |  |  |

|   |                        | 2.3.1        | Overall Architecture                        | 13   |  |  |  |  |

|   |                        | 2.3.2        | MicroBlaze                                  | 14   |  |  |  |  |

|   |                        | 2.3.3        | L2 Arbiter                                  | 23   |  |  |  |  |

|   |                        | 2.3.4        | Semaphore Synchronization                   | 25   |  |  |  |  |

|   | 2.4                    | Cacł         | he and Scratchpad Implementation on FPGAs   | 26   |  |  |  |  |

|   |                        | 2.4.1        | Configurability                             | 27   |  |  |  |  |

|   | 2.5                    | Asyr         | mmetric Caches in Multiprocessors           | 28   |  |  |  |  |

| 2 | ٨'n                    | Δον          | mmetric Cache Coherent Architecture for Po  | slv. |  |  |  |  |

| 3 |                        | Blaze System |                                             |      |  |  |  |  |

|   | 3.1 Level-1 Data Cache |              |                                             |      |  |  |  |  |

|   |                        | 3.1.1        | Design Process                              | 37   |  |  |  |  |

|   | 3.2                    | Leve         | el-1 Instruction Cache                      | 38   |  |  |  |  |

|   | 3.3                    | A co         | omparison of L1 Data and Instruction Caches | 42   |  |  |  |  |

| 4 | Me                     | mory         | y Architecture in PolyBlaze System          | 44   |  |  |  |  |

|   | 4.1                    | Leve         | el 1 Arbiter                                | 45   |  |  |  |  |

|   | 4.2                    | Leve         | el 2 Cache/Memory Interface                 | 48   |  |  |  |  |

|   | 4.3                    |              | Blaze Memory Link.                          |      |  |  |  |  |

|   | 4.4                    |              | etching Unit.                               |      |  |  |  |  |

| 5 | Eva                    | aluati       | ion and Experimental Results                | 50   |  |  |  |  |

|   | 5.1                    | Resc         | purce Usage                                 | 50   |  |  |  |  |

|   | 5.2                    | Timi         | ing Analysis                                | 62   |  |  |  |  |

|   | 5.3                    | Late         | ency                                        | 63   |  |  |  |  |

|   | 5.4                        | Appli  | ication Performance Study                       |   | 69 |  |

|---|----------------------------|--------|-------------------------------------------------|---|----|--|

|   |                            | 5.4.1  | Phase 1: Single-Process Application Performance |   | 70 |  |

|   |                            | 5.4.2  | Phase 2: Multi-Process Application Performance  |   | 72 |  |

| 6 | Conclusion and Future Work |        |                                                 |   |    |  |

|   | 6.1                        | Conc   | lusions                                         |   | 78 |  |

|   | 6.2                        | Futu   | re Work                                         |   | 79 |  |

|   | Bib                        | liogra | aphy                                            | 8 | 30 |  |

## **List of Tables**

| 2.1 | MicroBlaze core's three-stage pipeline optimized for minimum area/hardware cost [1]                                                                                         | 15 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | MicroBlaze core's five-stage pipeline optimized for maximum performance [1]                                                                                                 | 15 |

| 5.1 | Post place and route resource usage for different data cache configurations with 4kB direct-mapped instruction cache in a single core MicroBlaze system                     | 51 |

| 5.2 | Post place and route resource usage for different instruction cache configura-<br>tions with 4kB direct-mapped data cache in a single core MicroBlaze system<br>51          |    |

| 5.3 | Post place and route resource usage for different modules in a single core MicroBlaze system with 4kB direct-mapped (4 words per line) instruction and data caches.         | 52 |

| 5.4 | Post place and route resource usage for different modules in a single core<br>MicroBlaze system with several cache configurations (4kB direct-mapped, 4<br>words per line). | 53 |

| 5.5 | Post place and route resource usage for MicroBlaze caches with 4kB direct-<br>mapped 4 words per lines compared to the no cache baseline                                    | 54 |

| 5.6 | Post place and route resource usage for different modules in a single core MicroBlaze system with 4 kB or 16 kB direct-mapped (4 words per line) data caches.               | 55 |

| 5.7 | Post place and route resource usage for different data cache configurations with 4kB direct-mapped instruction cache in a dual core PolyBlaze system.                       | 56 |

| 5.8 | Post place and route resource usage for different instruction cache configu-<br>rations with 4kB direct-mapped data cache in a dual core PolyBlaze system.<br>57            |    |

| 5.9 | Post place and route resource usage for different data cache configurations with 4kB direct-mapped instruction cache in a quad core PolyBlaze system.                       | 58 |

| 5.10 | Post place and route resource usage for different instruction cache configu-<br>rations with 4kB direct-mapped data cache in a quad core PolyBlaze system.<br>59 |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.11 | Post place and route resource usage for different modules in a dual core<br>PolyBlaze system.                                                                    | 60 |

| 5.12 | Increased resource usage (after place and route) for PolyBlaze compared to MicroBlaze                                                                            | 61 |

| 5.13 | Maximum operating frequencies from different systems.                                                                                                            | 63 |

| 5.14 | Maximum operating frequencies of different modules in a dual core PolyBlaze system.                                                                              | 63 |

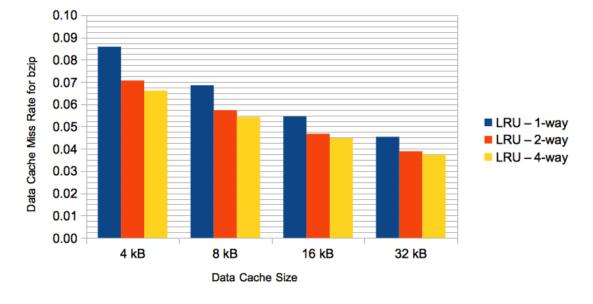

| 5.15 | Data cache read miss rate for bzip                                                                                                                               | 70 |

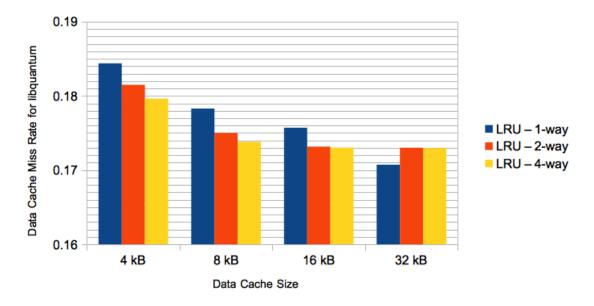

| 5.16 | Data cache read miss rate for libquantum                                                                                                                         | 70 |

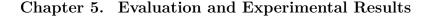

| 5.17 | Data cache read miss rate for specrand                                                                                                                           | 70 |

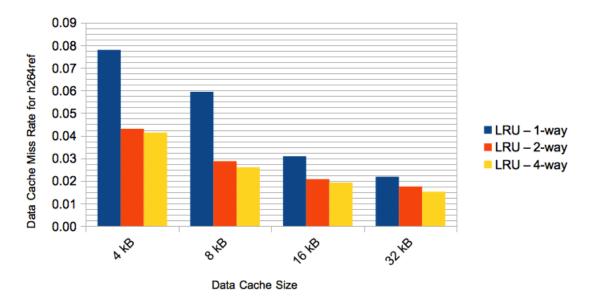

| 5.18 | Data cache read miss rate for h264ref.                                                                                                                           | 71 |

| 5.19 | Number of Load/Store instructions and their ratio in each benchmark appli-<br>cation during its execution time                                                   | 72 |

| 5.20 | Data cache read miss rate of the four benchmark applications for the two selected cache configurations. Optimal assignments are shown in bold.                   | 74 |

| 5.21 | Data cache read miss rate of the two-process experiments with optimal assignments.                                                                               | 75 |

| 5.22 | Data cache read miss rate of the two-process experiments with suboptimal assignments.                                                                            | 75 |

| 5.23 | Run time difference in seconds between optimal and suboptimal assignments in presence of different interfering applications                                      | 76 |

| 5.24 | Percentage of increased run time for different assignments in presence of various interfering applications.                                                      | 77 |

# **List of Figures**

| 2.1  | PolyBlaze: the multiple MicroBlaze platform                                       | 14 |

|------|-----------------------------------------------------------------------------------|----|

| 2.2  | MicroBlaze Core Block Diagram [1]                                                 | 16 |

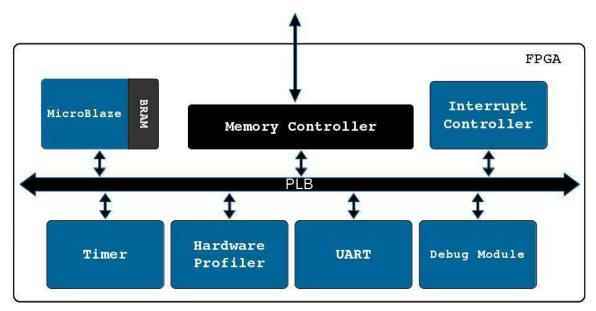

| 2.3  | A block diagram of a Linux capable MicroBlaze system.                             | 17 |

| 2.4  | Instruction Cache Organization in the MicroBlaze [1]                              | 19 |

| 2.5  | Data Cache Organization in the MicroBlaze [1]                                     | 21 |

| 3.1  | PolyBlaze's Data cache overview                                                   | 30 |

| 3.2  | PolyBlaze's PBML connections                                                      | 36 |

| 3.3  | Instruction cache's overview in PolyBlaze                                         | 39 |

| 4.1  | Memory Architecture in a PolyBlaze System                                         | 45 |

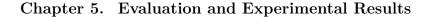

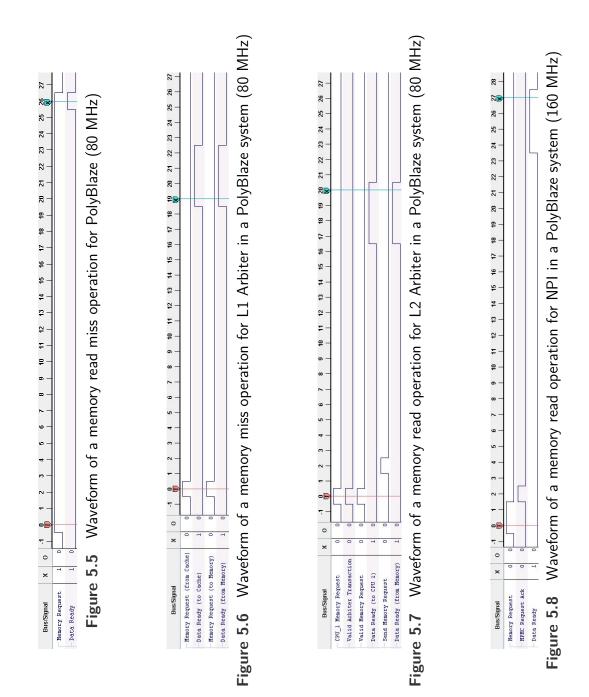

| 5.1  | Memory Read Operation Latencies                                                   | 64 |

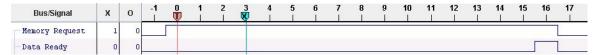

| 5.2  | Waveform of a memory read miss operation for MicroBlaze                           | 65 |

| 5.3  | Waveform of a memory read hit operation for MicroBlaze                            | 66 |

| 5.4  | Waveform of a memory read hit operation for PolyBlaze                             | 67 |

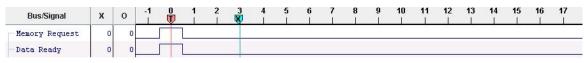

| 5.5  | Waveform of a memory read miss operation for PolyBlaze (80 MHz)                   | 68 |

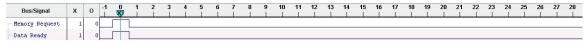

| 5.6  | Waveform of a memory miss operation for L1 Arbiter in a PolyBlaze system (80 MHz) | 68 |

| 5.7  | Waveform of a memory read operation for L2 Arbiter in a PolyBlaze system (80 MHz) | 68 |

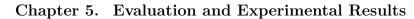

| 5.8  | Waveform of a memory read operation for NPI in a PolyBlaze system (160 MHz)       | 68 |

| 5.9  | Data cache read miss rate for bzip                                                | 71 |

| 5.10 | Data cache read miss rate for libquantum                                          | 72 |

| 5.11 | Data cache read miss rate for specrand                                            | 73 |

| 5.12 | Data cache read miss rate for h264ref. |  |

|------|----------------------------------------|--|

|------|----------------------------------------|--|

## Glossary

| ABACUS             | hArdware Based Accelerator for Characterization of User Software. 13, 29, 34, 40, 63, 64, 69, 78                                                   |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| AMP                | Asymmetric Multiprocessor. iv, 1–3, 6, 27, 28                                                                                                      |

| BRAM               | Block RAM. 10, 31, 37, 38, 50–61                                                                                                                   |

|                    |                                                                                                                                                    |

| CLB                | Configurable Logic Block. 10                                                                                                                       |

| CMP                | Chip-level Multiprocessor. iv, 1                                                                                                                   |

| COMA               | Cache-Only Memory Architecture. 7                                                                                                                  |

| DMA                | Direct Memory Access. 25, 26                                                                                                                       |

| DSP                | Digital Signal Processing. 10                                                                                                                      |

| FF<br>FIFO<br>FPGA | Flip-Flop. 10<br>First-In-First-Out. 23, 35, 41, 47, 48, 66, 67<br>Field Programmable Gate Array. viii, 2, 3, 10–14, 26, 28, 37, 51, 62,<br>63, 67 |

| FPGAs              | Field Programmable Gate Arrays. 5                                                                                                                  |

| FPU                | Floating Point Unit. 11, 14, 27                                                                                                                    |

| FSL                | Fast Simplex Link. 23, 48                                                                                                                          |

| GTS                | Global Task Scheduling. 28                                                                                                                         |

| I/O                | Input/Output. 6, 10                                                                                                                                |

| IC                 | Integrated Circuit. 10                                                                                                                             |

| IP                 | Intellectual Property. 10                                                                                                                          |

| ISA                | Instruction Set Architecture. 1, 3, 6, 28                                                                                                          |

| L1                 | Level-1. iv, viii, xii, 3, 4, 7, 9, 27, 30, 35–38, 41, 42, 44–50, 57, 60, 61, 63, 66–68, 78                                                        |

| L2                 | Level-2. viii, xii, 7, 23–25, 32, 33, 37, 44–48, 58, 60, 62, 63, 66–68, 78, 79                                                                     |

| LCC                | Library Cache Coherence. 9, 10                                                                                                                     |

| LMB                | Local Memory Bus. 18, 20, 23, 52, 53, 55, 60                                                                                                       |

| LRU                | Least Recently Used. 32, 39, 56–60, 63, 64, 69, 70, 72–74                                                                                          |

| LUT                | Look-up Table. 10, 31, 38, 51–61                                                                                                                   |

| LWX  | Load Word Exclusive. 17, 18, 25, 32                                             |

|------|---------------------------------------------------------------------------------|

| MMU  | Memory Management Unit. 13, 14, 17, 20, 22, 42                                  |

| MPMC | Multi-Port Memory Controller. 23, 35, 41, 44, 48, 54, 57, 63, 65–67             |

| MSR  | Machine Status Register. 18                                                     |

| NPI  | Native Port Interface. xii, 44, 48, 57, 58, 60, 63, 67, 68                      |

| NUMA | Non-uniform Memory Access. 7                                                    |

| OS   | Operating System. 2, 3, 6, 7, 12, 13, 28, 29, 38, 43, 64, 78, 79                |

| PBML | PolyBlaze Memory Link. xii, 4, 33–37, 40, 41, 44–46, 48, 57, 60, 61, 63, 66, 67 |

| PLB  | Processor Local Bus. 23, 52, 53, 55                                             |

| PVR  | Processor Version Register. 13                                                  |

| RAMP | Research Accelerator for Multiple Processors. 11                                |

| RISC | Reduced Instruction Set Computing. 13, 14                                       |

| SMP  | Symmetric Multiprocessor. iv, 1, 6, 13, 28                                      |

| SOCs | Systems-on-Chip. 5                                                              |

| SWX  | Store Word Exclusive. 17, 18, 25, 26, 32, 36, 47                                |

| TLB  | Translation Look-aside Buffer. 17                                               |

| UMA  | Uniform Memory Access. 7                                                        |

| WDC  | Write to Data Cache. 22, 31, 34, 35, 40                                         |

| WIC  | Write to Instruction Cache. 20, 40, 41                                          |

| XCL  | Xilinx CacheLink. 16, 18, 20, 23, 35, 41, 48, 54, 57, 61                        |

# **1** Introduction

Over the past decades, performance in modern computing systems has increased by several means including increasing operating frequencies. However, as processor frequencies reach their limits, a popular solution to increase performance has been adding more processors to increase parallelism. Today, a Chip-level Multiprocessor (CMP) provides two or more processing cores on a single chip that permit even greater performance due to reduced memory latency.

CMPs fall into two main categories: Symmetric Multiprocessor (SMP) and Asymmetric Multiprocessor (AMP). A SMP architecture comprises identical cores with equivalent frequencies, Instruction Set Architecture (ISA), cache sizes, functions, etc. Processing cores in a AMP architecture still have a common ISA, but they can utilize different configurations in their caches (different cache sizes, replacement policies, cache-line sizes, etc.), different operating frequencies, and reduced instruction support (e.g. no floating point operations).

Research on AMP systems is difficult as they are not widely available. Most commercial processors are often SMP with different cores possibly clocking at different rates. Moreover, detailed information about the internal architecture in AMP systems is sometimes proprietary. Also, these systems are not necessarily configurable. Therefore, system research has to rely on high-level information gathered from limited resources available about real-world behaviour of these processors. To solve this problem, we need a framework that provides configurable processor and cache architecture.

#### Chapter 1. Introduction

#### 1.1 Motivation

An Operating System (OS) uses different methods to balance its workload based on the demands of running applications and available resources (processors, their local cache memories, and the amount of physical memory). For instance, when assigning tasks to available processors, it is important to balance the workload as assigning too many tasks to a processor will impose an overload from context-switches; conversely, assigning not enough tasks would waste processor cycles while the processor is idle. Maintaining this balance is even more complicated in an AMP environment since some tasks can utilize certain resources better than others, e.g. some applications can utilize processor cache better than others. In such cases, analyzing system behavior in presence of multiple tasks requires insight as to the nature of the current tasks and the availability of resources in the system.

Modelling an AMP system on a FPGA can provide a rich framework for more research in this area. Having access to such a system with fully configurable caches allows the user to gather lots of data on complex interactions while having negligible impact on the software. Achieving this goal is not necessarily feasible on commercial processors or system simulators. Commercial multicore processors often include hardware registers that can be used to measure different events in the life time of an application. For instance, by measuring the number of cache hits and memory requests, we can obtain the hit ratio of an application. However, the number of hardware registers in commercial processors is limited and the measurements have to be taken from multiple independent executions of the application. Conversely, system simulators would execute the application in an emulated environment and capture the required information while running the application. Therefore, they can give us as much visibility as we need in the runtime of an application, but they impose a lot of overhead.

#### Chapter 1. Introduction

Developing an AMP framework comprising cores with identical ISA and asymmetric configurable caches that supports an OS, provides real-time visibility into how the system is actually working. Therefore, it allows us to investigate cache asymmetry and its impact on a multiprocessor system.

#### 1.2 Objective

PolyBlaze is a configurable research framework for systems research [2]. In this thesis, our objective is to develop an asymmetric Level-1 (L1) cache extension for the PolyBlaze research framework. In order to achieve this goal, we need modules such as configurable caches with a built-in coherency mechanism. Arbitration modules are also needed to provide the interconnection between processors and main memory and support the coherency mechanism. Additionally, implementing optional prefetching units can provide better insight into this AMP system. Since PolyBlaze is a FPGA system, we can create the whole hardware system with the desired configuration and run the OS on this platform. Then we can execute benchmark applications such as SPEC CPU2006 [3] to measure the impact of different configurations (symmetric and/or asymmetric) on the overall system performance.

#### **1.3 Contributions**

The main contribution of this thesis is the development of the necessary hardware infrastructure for the PolyBlaze framework to support L1 caches that may be asymmetrically configured. The proposed infrastructure addresses the necessary requirements for integrating caches into the PolyBlaze framework. Our cache infrastructure is also designed to be as configurable and scalable as possible. The following modules are presented in this thesis:

#### Chapter 1. Introduction

- Configurable asymmetric level-1 data and instruction caches,

- L1 arbiter,

- PolyBlaze Memory Link (PBML), and

- Prefetching units.

### 1.4 Thesis Organization

The remainder of the thesis is structured as follows. Chapter 2 describes the background on multicore system architectures, memory and cache coherence mechanisms, and PolyBlaze system. The new cache coherent architecture for the PolyBlaze processor is presented in Chapter 3. Chapter 4 outlines the memory architecture of the PolyBlaze processor and the roles of the added modules in the processor's memory path. Chapter 5 discusses the experimental framework and the experiments run to validate and evaluate our system. Finally, Chapter 6 concludes the thesis and outlines future work.

# 2 Background and Related Work

In 1965, Gordon E. Moore presented his observation, later known as Moore's law, that the number of transistors on integrated circuits doubles approximately every two years [4]. Later on, Intel executive David House predicted that chip performance, being a combination of the increase in the number of transistors and their operating frequency, would double every 18 months. On the other hand, in 1974, Robert H. Dennard et al. [5] stated that as transistors get smaller their power use stays constant (power use stays in proportion to area). This statement, later know as Dennard Scaling, was true until about 2005-2007. As such, while it is possible to shrink transistor sizes and put more and more transistors need to operate reliably at the same rate. Therefore, it is necessary to come up with other solutions to enable continued performance growth.

The remainder of this chapter presents the relevant background material and previous work for this thesis. First, in Section 2.1, we discuss multicore computer architectures, their memory infrastructure, memory coherency and synchronization in these systems. Then, we provide an overview of Systems-on-Chip (SOCs), Field Programmable Gate Arrays (FPGAs), soft processors and processor emulators in Section 2.2. Next, in Section 2.3, we describe the PolyBlaze framework and its development from the MicroBlaze soft processor and its internal architecture. Afterwards, we provide a brief overview of cache and scratchpad memories in different processors and the use of asymmetric caches in current processors.

#### 2.1 Multicore Computer Architecture

One of the solutions to the Dennard Scaling problem is to use parallel processing. Increased use of parallel computing in the form of multicore processors is one of the approaches that has been pursued to improve overall processing performance. Parallel processing in its simplest form is the use of two or more processing cores to execute simultaneous instructions in a single computer system [6] and share some or all of available memory and Input/Output (I/O) facilities in the system [7].

Multiprocessing systems are often designed in two different methods: 1) shared memory architecture vs. 2) distributed memory architecture. In shared memory models, there is one common shared memory for all cores and processors. This memory is usually very large since it will be the main memory in the system. In distributed memory models, on the other hand, each processor has its own, local memory. In this case, the content of each memory is not necessarily replicated anywhere else.

Shared memory architecture designs usually follow two different processor architectures. The first method is SMP in which all of the processing units are identical, i.e. they all have the same ISA, frequency, caches, memory, etc. In SMP systems, the OS can treat all the cores equally and if there are multiple processes running in parallel, the OS can run them on different processor cores.

The second method, AMP, is slightly different from SMP. The cores in these processors, still share the same ISA and operating frequency, but some configurations such as cache sizes or cache line sizes can be different. In these systems, the OS can still ignore the difference between processing cores and assign tasks to them. However, it is possible to take advantage of these different configurations and gain better performance from the whole system.

Distributed memory architecture designs have a different processing architecture method. Different processing units in these systems, use message passing mechanisms to communicate with each other. Therefore, they can have different processor architectures and even different formats for the methods as long as the interconnect network can translate the messages for the corresponding processors.

In this thesis, we focus on shared memory architectures. Globally shared memory architectures often use one of the following three organizations: 1) Uniform Memory Access (UMA) in which all the processors share the physical memory uniformly [8], 2) Non-uniform Memory Access (NUMA), which is similar to UMA except memory access time depends on the memory location relative to a processor [9, 8], and 3) Cache-Only Memory Architecture (COMA), in which the local memories for the processors at each node is used as a cache memory [8].

In shared memory architecture systems, the communication between processors is done by reading and writing memory locations [10]. However, there are two key problems regarding the scalability of a shared memory architecture system:

- 1. **Performance Degradation**: when several processors try to access the same memory location, we will have contention on the memory interface.

- 2. **Coherency**: modifications often cause different cached memories to have different values and loose consistency between different copies.

To address the performance degradation problem, we often try to balance the tasks assigned to each processor such that they can take advantage of their local private memories, e.g. L1 caches and sometimes L2 caches, so that the need to access the shared main memory is reduced. Typically, this problem is handled in the OS using different software algorithms, making it outside of the scope of this thesis. Instead, we focus on the second problem, i.e. memory coherency. This is often handled in

different layers of software and hardware, depending on the system architecture and consistency model. Sections 2.3.3 and 3.1 will discuss how we handle this problem in more detail withing different modules.

#### 2.1.1 Memory and Cache Coherence

When two or more processors or cores share a common area of memory, they have to consider the coherence of memory regions shared between themselves. This issue does not exist in a single-core system because when a value is modified by the processor, all subsequent reads of that memory location will see the updated value, regardless of the data being cached anywhere or not.

In a multicore system, many processors can access the same location of shared memory. In this case, so long as none of them tries to modify this location and everyone is only reading from it, they can share it indefinitely. However, as soon as one of them updates the shared location, the others will have to be notified in order to use the updated value. Otherwise, the other processors might go on using their out-of-date copy of the data that could reside in their local caches.

Overall, in a multicore system, the time window during which different processors might have inconsistent views of the shared memory could vary. This time could be as low as a few cycles, even zero in some cases, to an indeterminate length of time. The size of this window usually depends on the coherency protocol implemented in the system. Systems that have strict memory consistency between processors and will not allow any sort of caching, will always have a coherent memory. Systems that allow simple caches with write-through policy, i.e. every write to the cache will be sent to memory right away, usually need a few cycles for the memory synchronization to complete [11]. In these systems, because of the write-through policy, all the store operations will be passed to the main memory right away. The SPARC T1 [12],

with its L1 caches, is an example of this style of architecture. An alternate system architecture uses write-back caches and has more sophisticated caching techniques, which requires more complex coherency mechanisms as well. In these systems with write-back caches, memory will not be updated with the most up-to-date data until that data is evicted from cache and written back into memory. Intel and AMD processors have L1 caches that use a Write-back policy. In addition, these systems require extra software support to force coherency when atomic instructions are issued [13, 14].

#### **Coherence Mechanisms**

There are four different coherency mechanisms: 1) Snooping (or *write-invalidate*) [15], 2) Snarfing (or *write-update*) [15], 3) Directory-based [16, 15], and 4) Library Cache Coherence (LCC) [17]. In systems that use snooping, individual cache controllers will continuously monitor the memory accesses from every other processor. When a memory location is modified, the cache controller will invalidate its own copy of that location if it has a copy. This protocol is sometimes called a *write invalidate protocol* [18]. The second mechanism, Snarfing, is similar to Snooping in behaviour. In this mechanism, the cache controller will look at address and data. When another processor tries to update a memory location, the cache controller will grab the new data and update its own copy if it has any. Therefore, it will use the updated copy next time the processor asks for that cache line.

In systems with directory-based coherency mechanisms, a common directory will be used to keep track of data shared between caches to maintain coherency. When a processor needs to access shared data, it will ask the directory for permission and then loads the data entry from main memory into its cache. Upon modification of shared data in one of the caches, the directory will notify the other caches and either

update or invalidate their data.

The LCC mechanism is based on directory-based methods, but with less broadcasted messages. In this mechanism, libraries are sets of timestamps that are used to autoinvalidate shared cache lines. These timestamps are also used to prevent writes on the lines from happening until all shared copies expire. There are a few advantage to use LCC methods instead of directory-based mechanisms. One of advantages is elimination of need to broadcast a lot of messages and therefore simplifying the interconnection network. Additionally, LCC also allows reads on a cache block to take place while a write to the block is being delayed while memory consistency is still in tact [17].

#### 2.2 Soft Processors and Processor Emulators

FPGAs are Integrated Circuit (IC) devices that consist of arrays of logic resources that are designed to be configured by customers after manufacturing. For instance, a typical FPGA introduced by Xilinx [19], consists of several components including Configurable Logic Block (CLB) connected by an interconnection network of wiring channels and routing blocks (switch matrices).

FPGAs are heterogeneous arrays of configurable logic blocks (CLB) and other Intellectual Property (IP) blocks that can be programmed by customers to implement their desired circuits after manufacturing. Each CLB in turn is comprised of logic cells containing Look-up Table (LUT)s and registers or Flip-Flop (FF). The other IP cores commonly found in modern FPGAs include processors, Digital Signal Processing (DSP) blocks, Block RAMs (BRAMs), and I/O blocks. Developers can combine these components with user-defined modules to build complicated designs.

Along with the hard processors embedded in some FPGA fabrics, we can also instan-

tiate processors in the reconfigurable fabric. Reconfigurable fabric in FPGA enables us to investigate architectural and simulation research questions. For instance, we can accelerate the simulation of traditional architectures as done in [20] or open more research areas into soft processor architectures [21]. Additionally, soft processors allow us to create far better emulation platforms for the design of commercial multicore processors [22, 23].

The complexity of the tasks for soft processors in a system will define the complexity of the processor itself or the features that it might have. The PicoBlaze [24], for instance, is a simple 8-bit soft processor developed by Xilinx [19] that is suitable for designing simple state-machines. Xilinx's other soft processor, the MicroBlaze [1], and Altera Inc.'s NIOS II [25] are two other examples of commercial soft processors that are designed specifically to target their company's FPGA architecture.

Although hard processors on FPGAs support higher operating frequencies than soft processors, their configurability is limited compared to soft processors. For example, if for a particular task, we have to do some floating point calculations, we can simply add a Floating Point Unit (FPU) to the processor.

Additionally, soft processors open areas of research into multicore processor architecture. The Research Accelerator for Multiple Processors (RAMP) project [26] as one of the works done in multicore processor architecture research areas, focuses on multiple lightweight processors on tens and hundreds of FPGAs [27]. The Beehive Project enables multiple lightweight processors on a single FPGA[28]. The project Hthreads provides support for threads in hardware and software along with a hardware based OS [29]; Xilinx provides a lightweight xilkernel based multicore MicroBlaze system [30]. Also, on a larger scale, there are some emulation platforms for design of commercial multicore processors, e.g. a FPGA-synthesizable Intel®Atom<sup>™</sup>processor core, a

FPGA-synthesizable Intel®Nehalem<sup>™</sup> processor core, etc. [22, 23, 31]

One of these research areas looks into load balancing and workload behaviour in multicore architectures. Approaches taken by some multicore processor emulators based on FPGA platforms such as OpenSparc and LEON3 [32, 33] take advantage of access to the hardware implementation of the emulator. In these cases, the hardware implementation provides cycle-accurate visibility into the microachitecure of the system. On the software side, the capacity to run a full OS provides full access to the features that might be of interest in the operating system.

The OpenSPARC based systems support a simple version of the Linux distribution (based on Ubuntu Linux distribution) for a single-core or dual-core setup. These systems, however, have limited scalability. The memory hierarchy in dual-core systems requires a single MicroBlaze to process all memory requests. Moreover, if we want a multicore system, we have to use separate FPGA boards, which in turn can impose other restrictions on the system. Another SPARC-based platform is the LEON3. It supports up to a dual-core setup. However, the memory controller support for different boards is incomplete. Furthermore, due to the hardware resource usage, LEON3 has a large processor design such that we can only fit two processors on a Virtex 5 110t FPGA from Xilinx.

There are other soft processors that have Linux support. NIOS II from Altera Inc. is one of these soft processors [25]. Xilinx's MicroBlaze is another soft processor that supports Linux [1]. PetaLogix [34], an embedded Linux solutions provider that was acquired by Xilinx, has been providing Linux support for MicroBlaze soft processor and PowerPC processors since the 2.6.30 version of the Linux kernel. The latest version of this distribution was released in February 2014. A multicore version of MicroBlaze is PolyBlaze [2]. We can fit up to an eight core PolyBlaze (four cores

with medium-sized caches) in a Virtex 5 110t FPGA from Xilinx.

### 2.3 PolyBlaze

PolyBlaze is a 32-bit Reduced Instruction Set Computing (RISC) embedded multicore soft processor based on the MicroBlaze core. It consists of several instances of slightly modified MicroBlaze cores and a few new modules. These new modules exist to provide the required hardware support for sharing resources in a multicore processor. Without this hardware infrastructure, it is still possible to run applications on this processor, but we cannot support booting an SMP OS and run general applications [2, 35]. The modifications on the processor are ranged from minor additions, such as processor identification through existing Processor Version Register (PVR), to more extensive modifications on interrupts, timers, atomic operations and Memory Management Unit (MMU) [2].

#### 2.3.1 Overall Architecture

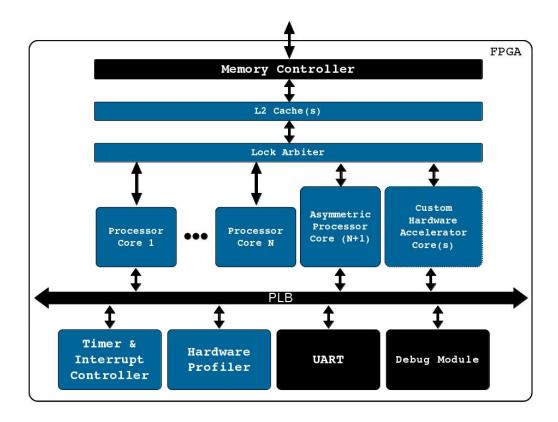

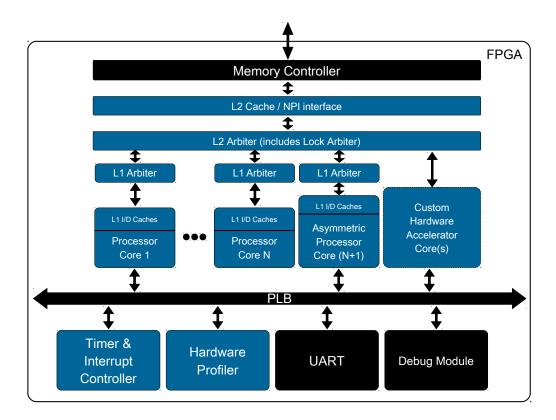

Figure 2.1 provides an example PolyBlaze system that consists of multiple processor cores with symmetric or asymmetric configurations, multiple levels of cache memory, and potential custom hardware accelerator cores. Symmetric processor cores by themselves allow a simple SMP system, while asymmetric processor cores and custom hardware accelerator cores enable a more complex heterogeneous system. Multiple levels of cache memory are common in systems, especially when some of them are shared while the rest are private. On top of these, the hArdware Based Accelerator for Characterization of User Software (ABACUS) hardware profiler can hook into many of these modules and gather useful information about their operation.

Figure 2.1 PolyBlaze: the multiple MicroBlaze platform

#### 2.3.2 MicroBlaze

MicroBlaze is a 32-bit RISC embedded processor soft-core. It is optimized for implementation in Xilinx FPGAs [1] and is highly configurable. Features such as MMU, FPU, instruction and data caches, dedicated hardware multiplier and divider, hardware barrel shifter and several bus connections are just some examples of the options that we can use for an instance of MicroBlaze soft processor [1].

MicroBlaze instruction execution is pipelined. There are two configurations for the processor pipeline:

- Three-stage pipeline: if we optimize the processor implementation to reduce the hardware cost, we will have three stages in the pipeline: 1) Fetch, 2) Decode, and 3) Execute [1]. Figure 2.1 illustrates a three stage pipeline example with two stall slots.

- Five-stage pipeline: if we optimize the processor implementation to maximize performance, we will have five stages in the pipeline: 1) Fetch (IF), 2) Decode (OF), 3) Execute (EX), 4) Access Memory (MEM), and 5) Writeback (WB) [1]. Figure 2.2 illustrates a five stage pipeline example with two stall slots.

Table 2.1

MicroBlaze core's three-stage pipeline optimized for minimum area/hardware

cost [1]

| cycle number    | 1     | 2      | 3       | 4       | 5       | 6       | 7       |

|-----------------|-------|--------|---------|---------|---------|---------|---------|

| instruction 1   | Fetch | Decode | Execute |         |         |         |         |

| instruction $2$ |       | Fetch  | Decode  | Execute | Execute | Execute |         |

| instruction $3$ |       |        | Fetch   | Decode  | Stall   | Stall   | Execute |

**Table 2.2** MicroBlaze core's five-stage pipeline optimized for maximum performance [1]

| cycle number    | 1  | 2  | 3  | 4   | 5   | 6     | 7     | 8   | 9  |

|-----------------|----|----|----|-----|-----|-------|-------|-----|----|

| instruction 1   | IF | OF | EX | MEM | WB  |       |       |     |    |

| instruction $2$ |    | IF | OF | EX  | MEM | MEM   | MEM   | WB  |    |

| instruction $3$ |    |    | IF | OF  | EX  | Stall | Stall | MEM | WB |

In any case, most of instructions require one clock cycle in each pipeline stage. There are also a few instructions that require multiple clock cycles (in execution stage) to complete. In those cases, bubbles are used to stall the pipeline.

Additionally, there are some instructions that require multiple cycles in other stages, e.g. memory stage. Load instructions fall into this last category. This additional latency can significantly affect the pipeline efficiency especially while reading instructions from external memory. In order to mitigate this problem, MicroBlaze implements an instruction prefetch buffer. This prefetch buffer can significantly reduce the impact of such multi-cycle instruction memory latencies.

#### **Overall Architecture**

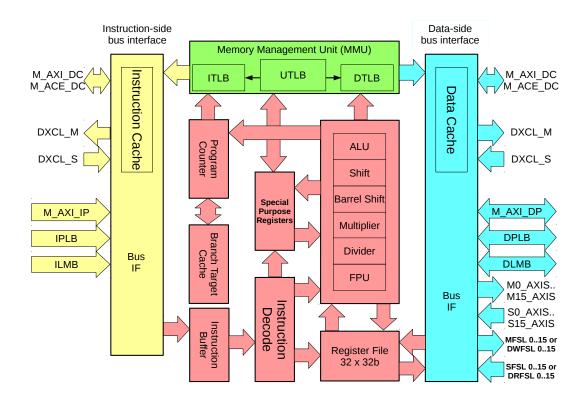

Figure 2.2 illustrates a functional block diagram of the MicroBlaze core. As we can see in this figure, MicroBlaze has a Harvard memory architecture. Modules shown with darker background are optional and can be excluded from the processor if not necessary. The processor has up to three interfaces for memory accesses:

- Local Memory Bus (LMB)

- Advanced eXtensible Interface (AXI4) or Processor Local Bus (PLB)

- Advanced eXtensible Interface (AXI4) or Xilinx CacheLink (XCL)

Figure 2.2 MicroBlaze Core Block Diagram [1]

Figure 2.3 A block diagram of a Linux capable MicroBlaze system.

Moreover, MicroBlaze has a MMU that is based upon the PowerPC 405 [1] MMU. The MMU in MicroBlaze is software managed, i.e. on Translation Look-aside Buffer (TLB) misses, software subroutines will add or remove entries in TLB.

#### Semaphore Synchronization

In a system based on MicroBlaze soft processors, programs can implement semaphore operations such as spin locks, test and set, compare and swap, exchange memory, and fetch and add, using Load Word Exclusive (LWX) and Store Word Exclusive (SWX) instructions.

In order to implement an atomic operation, the program should first use LWX to load a semaphore from memory and set an internal reservation bit in the processor. Then the program tries to write the result back to the same memory location using a SWX instruction. If the internal reservation bit is set, the SWX will go through. Otherwise, if for any reason this internal reservation bit has been cleared, the SWX

will fail to go through, which means the atomic operation has failed. The internal reservation bit can be cleared on different conditions such as an exception, interrupt or another condition store to the same location. The success or failure of a SWX instruction will be stored in the carry bit in Machine Status Register (MSR) [1].

There are some limitations for semaphore synchronization in MicroBlaze, however. The first limitation is that we can only maintain one reservation at a time. So if we want to change the address associated with the reservation, we have to use another LWX instruction. Also, executing a SWX always clears the reservation bit regardless of what the associated address is, i.e. no address matching check happens.

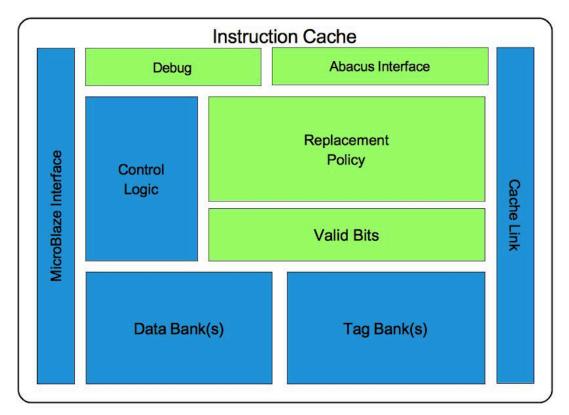

#### **Instruction Cache**

MicroBlaze has an optional instruction cache. This instruction cache can be used for improved performance when the processors is executing code that resides outside the Local Memory Bus (LMB) address range<sup>1</sup>. As mentioned before, MicroBlaze is designed to be very configurable. To that end, its instruction cache is also very configurable. Some of the features in the instruction cache are as follows [1]:

- Direct mapped (1-way associative)

- User selectable cacheable memory address range

- Configurable cache, tag, and cache-line (4 or 8 words) sizes

- Caching over AXI4 interface or XCL interface

- Optional stream buffers to improve performance by speculatively prefetching instructions

- Optional victim cache to improve performance by saving evicted cache lines upon replacement and reduce the number of conflict misses

<sup>&</sup>lt;sup>1</sup>The access time for reading from or writing into LMB is just one cycle.

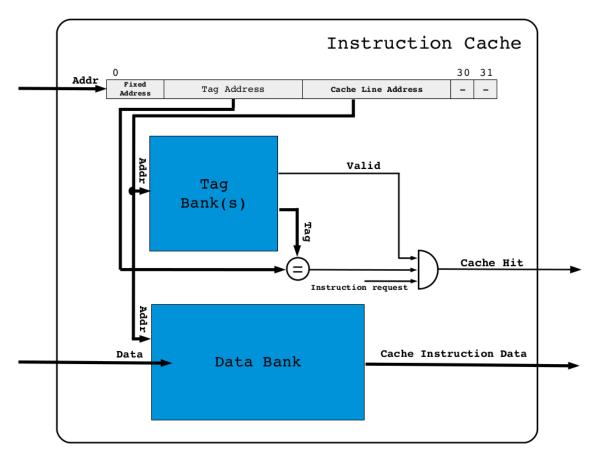

The following Figure 2.4 illustrates the organization of instruction cache in MicroBlaze. The cacheable instruction address consists of two parts: 1) the cache address, and 2) the tag address. Since the instruction cache can be configured from 64 bytes to 64 kB, a cache address will be between 6 to 16 bits. In addition to that, the tag address together with the cache address should match the full address of cacheable memory. Since MicroBlaze instructions are single words (four bytes), then instruction cache will ignore the two least significant bits [1].

Figure 2.4 Instruction Cache Organization in the MicroBlaze [1]

The instruction cache in the MicroBlaze has optional stream buffers. When the stream buffers are enabled, the cache will fetch subsequent cache lines in advance,

until the stream buffer is full (up to two cache lines). If the processor requests for subsequent instructions from a cache line, they will be immediately available [1].

There is an optional instruction, Write to Instruction Cache (WIC), that applications can use to invalidate cache lines in the instruction cache from within the software. WIC will be considered as a privileged instruction when MicroBlaze is configured to use MMU [1].

#### Data Cache

MicroBlaze has an optional data cache. This data cache can be used for improved performance when the processors is accessing data that resides outside the LMB address range<sup>2</sup>. As mentioned before, MicroBlaze is designed to be very configurable. To that end, its data cache is also very configurable. Some of the features in the data cache are as follows [1]:

- Direct mapped (1-way associative)

- Write-through or Write-back

- User selectable cacheable memory address range

- Configurable cache, tag, and cache-line (4 or 8 words) size

- Caching over AXI4 interface or XCL interface

- Optional victim cache to improve performance by saving evicted cache lines

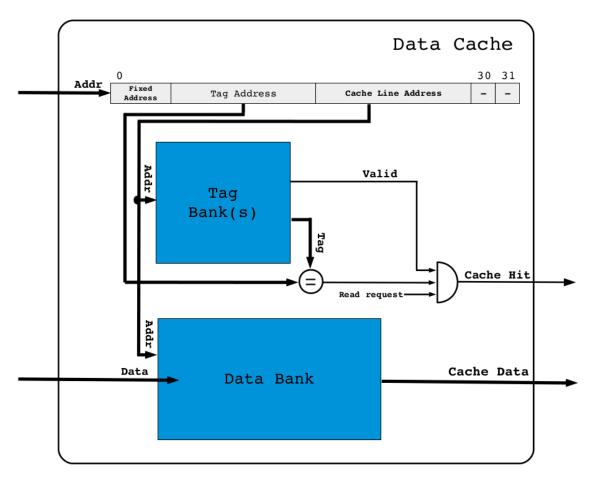

Figure 2.5 illustrates the organization of data cache in the MicroBlaze. Similar to the instruction cache, the cacheable data address consists of two parts: 1) the cache address, and 2) the tag address. The data cache can be configured from 64 bytes to 64 kB, so a cache address will be between 6 to 16 bits. In addition to that, the tag address together with the cache address should match the full address of cacheable memory [1].

$<sup>^{2}</sup>$ As mentioned before, the access time for reading from or writing into LMB is just one cycle.

Chapter 2. Background and Related Work

**Figure 2.5** Data Cache Organization in the MicroBlaze [1]

When the data cache is configured to use the write-through protocol, a store to an address within the cacheable range generates an equivalent write request over the data interface to external memory. In case of a write cache-hit, i.e. the target address word is in the cache, the write also updates the cached data. A write cache-miss does not load the associated cache line into the cache [1].

When the data cache is configured to use the write-back protocol, a store to an address within the cacheable range always updates the cached data. Therefore, if the target address word is in the cache, i.e. a write cache-hit, the data will be updated in the

cache. In this case, no equivalent write will be sent over the data interface to external memory. On the other hand, if the target address word is not in the cache, i.e. a write cache-miss, the data will be updated in the cache, the address is first requested over the data interface from external memory and written into the cache. Then the cache will update the data as if it is a write cache-hit. In case of a write cache-miss, if the cache line that is being brought to the cache is already occupied by another line of data that has already been modified, the cache has to evict the occupying line and write it to the external memory before overwriting it with the incoming data [1].

In both write-through and write-back protocols, when processor wants to read some data from cacheable address range, the cache triggers a check to determine if the requested data is currently cached. If the requested data is caches, then we will have a read cache-hit and the requested data will be retrieved from the cache. Otherwise, the address will be requested over the data interface from the external memory on a read cache-miss. In this case, the processor pipeline has to be stalled until the cache line is returned from the external memory controller [1].

Similar to instruction cache, there is an optional instruction, Write to Data Cache (WDC), that applications can use to invalidate cache lines in data cache from within the software. When MicroBlaze is configured to use MMU, WDC will be treated as a privileged instruction. Additionally, when the data cache is using a write back protocol, this instruction can be used to force cache line flushes [1].

Over all, the instruction and data caches in MicroBlaze behave similarly in many ways. However, there are some key differences between them. The first difference is that instruction cache is read only whereas data cache can be modified through the applications<sup>3</sup>. The second difference is that instruction cache works with both virtual

$<sup>^{3}</sup>$ It is possible to update instruction cache through the application (self-modifying code), but in order to actually update the instruction cache, we have to invalidate the desired cache lines and force

and physical addresses while data cache only works with physical addresses.

# XCL

XCL is a high performance interface for external memory accesses. MicroBlaze's XCL interface is designed to connect directly to a memory controller such as Multi-Port Memory Controller (MPMC) that supports integrated First-In-First-Out (FIFO)s (Fast Simplex Link (FSL) buffers).

The XCL interface is only available on MicroBlaze when at least one of the caches is enabled. Memory locations that reside outside the cacheable range will be accessed over other bus interfaces such as Processor Local Bus (PLB) or LMB. The XCL controllers can handle 4 or 8-word cache lines. Moreover, they can be configured to use either critical word first or linear fetch depending on the selected protocol. When selected protocol is critical word first, when processor is requesting a second word in a cache line, that word is what will be brought into the cache through XCL first and the rest of the words follow it. For example. when the processor request the third word in a cache line, the words fetched for the cache line will arrive in this order: 3, 4, 1, 2. Conversely, in a linear fetch protocol, the words in a cache line will always get to the cache in order from the first to the last word. Regardless, the separation of XCL from PLB bus reduces contention for non-cached memory accesses.

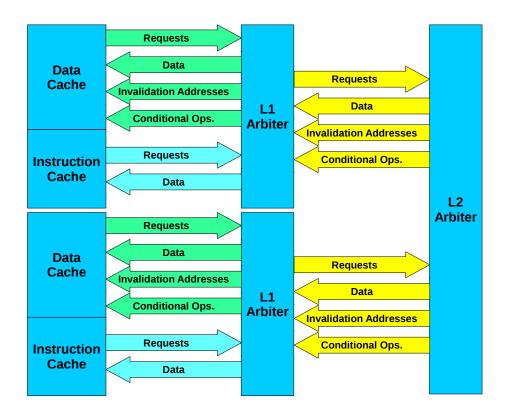

## 2.3.3 L2 Arbiter

L2 Arbiter is an important module in PolyBlaze's memory hierarchy. This module has three main purposes: 1) receive all the requests and pass them on to memory in order, 2) broadcast invalidation requests to maintain memory coherency, and 3) handle reservations and conditional operations (which is done by Lock Arbiter as

the program to continue executing from there. Then the instruction cache will read the updated values from memory.

#### described in Section 2.3.4).

As mentioned before, the first purpose of the L2 Arbiter is to receive requests from all of the connected processors and hardware accelerators and pass them on to memory in order. In order to achieve this goal, the L2 Arbiter scans its input ports one by one using a round robin method so that every connected processor gets their fair share of requests. On any given cycle, if the selected processor does not have any requests, the L2 Arbiter will consider other ports that come after the selected processor until it detects a request or until it determines that no one has any requests. This method allows a fair memory access for every port, so no port will be waiting for its turn while other ports keep sending memory requests. Also, if one port does not have any request on its turn, another port can use the cycle to send a request to memory, hence the cycle will not go to waste.

The second purpose of the L2 Abiter is to broadcast invalidation requests to maintain memory coherency between connected ports. Since the L2 Arbiter is the central point through which all memory requests are sent, it can broadcast invalidation requests correctly. To achieve this goal, the L2 Arbiter will generate an invalidation packet whenever it is issuing a write request on behalf of a port. These invalidation packets will be broadcast to every other port. When the broadcasting is complete and the write request has been written to memory queues, the L2 Arbiter considers the write operation successful and removes it from processor's queue.

The third role of the L2 Arbiter is to handle reservations and conditional requests. Each port in the L2 Arbiter has its own reservation bit and reservation address register. Upon receiving a conditional load request from a processor, the L2 Arbiter sets the corresponding reservation bit and registers the address of load operation into the corresponding reservation address register. In addition, the load request is passed

on to memory. Upon receiving a conditional store request, the L2 Arbiter checks the reservation bit and looks for a match between reserved address and conditional store's address. If the address matches and the reservation bit is set, then conditional store request is considered successful; otherwise it is considered as a failed request. Successful requests are passed on to memory and failed requests will be dropped. Additionally, the L2 Arbiter sends a notification to the corresponding processor and notifies them of the result of the conditional store. There are other features in later versions of the L2 Arbiter including burst writes and Direct Memory Access (DMA) support. However, they are not required in this work.

#### 2.3.4 Semaphore Synchronization

As discussed earlier, the MicroBlaze performs atomic operations with conditional load/store instructions: LWX and SWX. First LWX is used to load from memory, e.g. a semaphore's location, and set the internal reservation bit. Then, a SWX will be used to write a new value to that location if the reservation bit is still set. If this bit is cleared for any reason, interrupts, exceptions, or other conditional stores to any memory location, the conditional store will not happen [1]. This design is perfectly suitable for a single-core system, but it cannot guarantee that no other processor will modify the memory location. In other words, this behaviour will not be able to guarantee the atomicity of operation.

In a multicore system, several memory requests can be in progress at a given time. Therefore, PolyBlaze has to take a slightly different approach to this problem. In PolyBlaze, the Lock Arbiter, as shown in Figure 2.1, will take care of reservation handling for each processor and acts as the central synchronization point between all the processors. In this system, all the store operations will be passed to the Lock Arbiter along with extra signals indicating that they are regular or conditional stores.

Then the Lock Arbiter will decide whether to put the write request to main memory or to drop the request because the reservation bit has been cleared before the store reaches the Lock Arbiter. Then the Lock Arbiter will notify the processor of the result of its conditional store via some other extra signals. The result of this operation is then fed back into the processors logic the execution of the SWX instruction will be complete [2].

Beside moving the reservation bit to the Lock Arbiter, PolyBlaze improves the performance of lock arbitration by adding one reservation bit per processor and a matching address for each reservation bit. The extra logic used here helps with performance and scalability of the Lock Arbiter. Since each processor has its own reservation bit and reservation address registers, multiple processors can work with different semaphores and locks at the same time without interferring with each other. However, it is worth noting that in this system, when we have any store operation to memory, if someone else has tried to set a reservation on that location, we will clear their reservation bit so they will fail and have to try again [2].

# 2.4 Cache and Scratchpad Implementation on FPGAs

Memory hierarchies in modern multicore computing systems are based on one of the following schemes: 1) multi-level coherent caches, or 2) scratchpad memories with DMA support. Systems that use caches are often general purpose systems as the software programmer does not need to know where the data is actually stored or how the hardware is handling the data movements in the system. Such data movements are indirect results of cache misses and coherence events. In contrast, software developers for systems that use scratchpads, need to know how the data is supposed to be stored in memory [36]. This knowledge, obviously, can lead to much better performance. Moreover, the user control over the scratchpads eliminates the

need for coherency mechanisms between multiple scratchpads and, therefore, such systems require less additional inter-processor communications. These optimizations become especially important in large-scale systems since coherency mechanisms, due to their need for inter-processor communications, can have dramatic effects on the scalability of a system [37].

Many of the soft processors mentioned in Section 2.2 either do not implement L1 caches at all or implement a single core system, without any coherency mechanisms. MicroBlaze [1] and NIOS II [25] only provide single core systems. These processors are highly configurable but their L1 cache implementations use only a direct-mapped approach. Also, since they only support a single core system, they do not implement any coherency mechanisms [1, 25].

Conversely, OpenSPARC T1[32] supports coherent L1 caches, but it is not very configurable. However, an OpenSPARC core is large enough to use almost all of available resources in a Virtex 5 110LXT. Moreover, the memory controller in OpenSPARC system is emulated using the firmware on a MicroBlaze processor. Therefore, the setup for a multicore OpenSPARC system requires multiple FPGA boards due to the size of the processor and limits the system scalability. Another SPARC-based system supporting multicore setup uses LEON3 soft processors [33], but board memory controller support for LEON3 processor is limited.

## 2.4.1 Configurability

As mentioned earlier, MicroBlaze and NIOS II are two highly configurable soft processors [1, 25]. The built-in configurability in these cores permits more options for an AMP system. For instance, we can turn on a FPU in one of the cores, use hardware multipliers and dividers in another, and keep the rest simple to reduce the resource usage in the whole system. However, not all soft processors, regardless of being a

single-core or multicore processor, support enough configurability for our purpose. Nikiforos et al. present a local memory design that can be configured to behave as a cache and a scratchpad at the same time to support implicit communications via caches and explicit communications via scrachpads. In their work, it is possible to lock parts of cache and prevent that part from evicting data, hence treating it as an scratchpad memory [38].

# 2.5 Asymmetric Caches in Multiprocessors

Most of the work done on caches either target single core computing systems or SMP systems. ARM's *little.BIG* architecture is one of the commercial movements towards AMP systems. In this architecture, two types of processors exist. "big" processors are designed to provide maximum compute performance while "LITTLE" processors are designed for maximum power efficiency [39]. Since both of these processor types use the same ISA, the OS running on the system does not necessarily need to be aware of the difference between processors. However, the Global Task Scheduling (GTS), which is in fact a patch on the scheduling mechanisms in the OS, is aware of the difference between processors and tries to get better performance by assigns tasks to different processors based on the needs of applications. Besides this architecture, there has not been any work on asymmetric caches on FPGAs to the extent of author's knowledge. Moreover, the ARM processor cores available on some FPGAs are hard cores and are not part of the reconfigurable fabric of the FPGA.

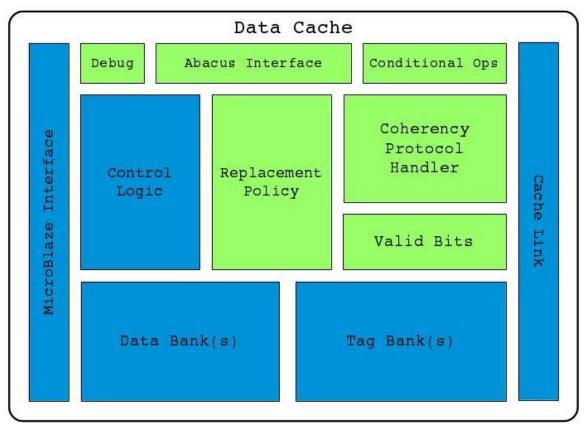

A single-core MicroBlaze system with its instruction and data cache can boot an OS or run any generic application without any problems. A multicore system based on MicroBlaze, however, cannot necessarily do that just by replicating MicroBlaze cores and their caches. Since there is no coherency mechanism implemented for MicroBlaze's caches, without proper measures, the memory consistency will become a problem, the OS will fail to even boot, and generic applications will fail to execute correctly. Therefore, the designed caches for PolyBlaze include a coherency protocol handler. Additionally, these caches follow the original MicroBlaze caches and use as many parameters as possible to have high configurability, which in turn enables asymmetric architectures. Besides, ABACUS interface allows ABACUS hardware profiler to easily connect to PolyBlaze caches and gather data about their behaviour.

The remainder of this chapter will present the proposed coherent cache memory architecture. This includes the necessary modifications on instruction and data caches to support a simple *write invalidation protocol*. In addition, we will talk about possible configurations of different parameters in the system and how they will affect system behaviour. Finally, we will discuss the involvement of caches in synchronization and conditional instructions.

# 3.1 Level-1 Data Cache

MicroBlaze has an optional data cache (we can remove it from the system without loosing functionality). However, the data cache is mandatory in PolyBlaze's current implementation as it is involved in handling conditional instructions as well as data access to memory. So in a PolyBlaze system, it is possible to disable the data cache, but its memory interface has to remain in the system. Figure 3.1 highlights the internal architecture of PolyBlaze's data cache. The blue modules exist in MicroBlaze's data cache and the green modules are added for PolyBlaze's data cache. A detailed explanation of each module's role in the cache follows.

Figure 3.1 PolyBlaze's Data cache overview

# Data Bank(s)

The data bank in MicroBlaze's data cache is just used to keep the data. It has several parameters such as the size of cache line or type of memory used to store the data (BRAM or LUTs). In PolyBlaze's data cache, we have the same parameters. However, depending on the replacement policy, the number of used memory blocks can be different.

## Tag Bank(s)

The tag bank in MicroBlaze's data cache is used to keep the tag values and the valid bits. The available parameters for tag bank are similar to data bank's parameters: size of cache line and type of memory used to store values (BRAM or LUTs). In PolyBlaze's data cache, we have the same parameters for tag bank. However, the number of used memory blocks can be different depending on the replacement policy. Additionally, valid bits in PolyBlaze's data cache are stored in a separate bank.

## Valid Bits

As mentioned before, valid bits in MicroBlaze's data cache are kept along with tag values and are only updated when there is either a cache miss or the processor has issued a WDC instruction to invalidate a cache line in data cache. In the PolyBlaze, we have moved the valid bits into a separate memory bank. The main reason for breaking this logic into two separate parts is to localize the logic that accesses the valid bits since it is part of the critical path in the processor. This logic consists of accesses for cache hits, updates to valid bits upon cache misses, invalidations due to WDC instructions, and invalidation logic from coherency protocol. Additionally, the replacement policy module needs access to valid bits as well, depending on the replacement policy used in the system.

## **Replacement Policy**

MicroBlaze only implements a direct-mapped replacement policy. Therefore, the logic for this module is embedded with the rest of logic in cache. In PolyBlaze, we implement a dedicated module and make replacement decisions in that module in order to be able to define different replacement policies such as direct-mapped, Least Recently Used (LRU), Clock, or pseudo-random replacement policy<sup>1</sup>. This module will also allow for asymmetric caches in a PolyBlaze system since we can choose different replacement policies for different cores.

## **Conditional Operations**

Conditional load operations in MicroBlaze are unrelated to the data cache, except that the processor will request data from the data cache, just like any other load operation. In the PolyBlaze, when a processor tries to execute a LWX instruction, instead of setting an internal reservation bit, it will notify the data cache. The data cache in turn will force<sup>2</sup> a cache miss and send a memory request to the L2 Arbiter (a module that includes the Lock Arbiter), which handles reservations. The rest of what happens for the LWX instruction is the same as regular loads operations of MicroBlaze's data cache behaviour: when the data cache receives the data from memory, it will return the data to the processor just like any other load instruction.

Similar to conditional loads, conditional store operations in MicroBlaze do not effect the data cache except to execute a store operation if the store operation is supposed to go through upon a successful conditional operation. Conversely, in PolyBlaze, on a SWX instruction, a write request will be sent to the L2 Arbiter. Then, the L2 Arbiter

<sup>&</sup>lt;sup>1</sup>In this thesis, we only implement direct-mapped and LRU replacement policies.

$<sup>^{2}</sup>$ We force a cache miss because we have to send a request to the Lock Arbiter to make sure that another core is not trying to access the same lock. So if the cache line happens to be in the cache, we will mark it as invalid and send a request to memory to fetch the data from there.

will decide whether the write is supposed to go through all the way to memory or not. If the operation is successful, meaning the reservation bit in the L2 Arbiter is set and the write address matches the reserved address, the L2 Arbiter will pass on the write request to memory. In the mean time, the L2 Arbiter notifies the processor of the result of conditional store via sending a single bit through PBML. If the operation is successful, the value of this bit will be '1', otherwise it will be '0'. When the data cache receives the result of conditional store, it will pass the result to the processor. In addition to that, upon a successful conditional store, the data cache will update its content as if there has been a hit on the requested address.

## **Coherency Protocol Handler**

The coherency protocol handler in PolyBlaze's data cache receives the invalidation requests from the L2 Arbiter. Since the implemented method is *write invalidation protocol*, this module will look at invalidation address in each packet and invalidate the corresponding cache line if the tag from invalidation address matches the tag value read from tag bank.

The *write invalidation protocol* is one of the simplest coherency protocols. More sophisticated methods that are not part of this work, will keep track of which processor is accessing what parts of memory and notify other processors if necessary. Some even mark memory blocks as their own and respond to requests from other processors instead of main memory. Many of these protocols are designed for write-back caches though and are not necessarily applicable to write-through caches. Moreover, these complicated methods would require a more sophisticated interconnect than what we currently have in the L2 Arbiter.

## **ABACUS** Interface