# Robust Micromachining of Compliant Mechanisms for Out-of-plane Microsensors

# by Kourosh Khosraviani

M.A.Sc., Simon Fraser University, 2007 B.Sc., Shahid Beheshti University, 1995

Thesis Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

in the

School of Engineering Science

Faculty of Applied Sciences

# © Kourosh Khosraviani 2013 SIMON FRASER UNIVERSITY Summer 2013

All rights reserved.

However, in accordance with the *Copyright Act of Canada*, this work may be reproduced, without authorization, under the conditions for "Fair Dealing." Therefore, limited reproduction of this work for the purposes of private study, research, criticism, review and news reporting is likely to be in accordance with the law, particularly if cited appropriately.

# **Approval**

| Name:                                                                                         | Kourosh Khosraviani                                                        |     |

|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|

| Degree:                                                                                       | Doctor of Philosophy                                                       |     |

| Title of Thesis:                                                                              | Robust Micromachining of Compliant Mechanisms to Out-of-plane Microsensors | for |

| Examining Committee:                                                                          | Chair: Jie Liang<br>Associate Professor                                    |     |

| Albert M. Leung<br>Senior Supervisor<br>Professor                                             |                                                                            |     |

| Ash Parameswaran<br>Supervisor<br>Professor                                                   |                                                                            |     |

| Behraad Bahreyni<br>Supervisor<br>Assistant Professor                                         |                                                                            |     |

| Marek Syrzycki<br>Internal Examiner<br>Professor<br>School of Engineering Scier               | nce                                                                        |     |

| Karim Karim External Examiner Professor, Electrical and Co Engineering University of Waterloo | mputer                                                                     |     |

|                                                                                               |                                                                            |     |

| Date Defended/Annroyed:                                                                       | Tuly 10 2012                                                               |     |

# **Partial Copyright Licence**

The author, whose copyright is declared on the title page of this work, has granted to Simon Fraser University the right to lend this thesis, project or extended essay to users of the Simon Fraser University Library, and to make partial or single copies only for such users or in response to a request from the library of any other university, or other educational institution, on its own behalf or for one of its users.

The author has further granted permission to Simon Fraser University to keep or make a digital copy for use in its circulating collection (currently available to the public at the "Institutional Repository" link of the SFU Library website (www.lib.sfu.ca) at http://summit/sfu.ca and, without changing the content, to translate the thesis/project or extended essays, if technically possible, to any medium or format for the purpose of preservation of the digital work.

The author has further agreed that permission for multiple copying of this work for scholarly purposes may be granted by either the author or the Dean of Graduate Studies.

It is understood that copying or publication of this work for financial gain shall not be allowed without the author's written permission.

Permission for public performance, or limited permission for private scholarly use, of any multimedia materials forming part of this work, may have been granted by the author. This information may be found on the separately catalogued multimedia material and in the signed Partial Copyright Licence.

While licensing SFU to permit the above uses, the author retains copyright in the thesis, project or extended essays, including the right to change the work for subsequent purposes, including editing and publishing the work in whole or in part, and licensing other parties, as the author may desire.

The original Partial Copyright Licence attesting to these terms, and signed by this author, may be found in the original bound copy of this work, retained in the Simon Fraser University Archive.

Simon Fraser University Library Burnaby, British Columbia, Canada

revised Fall 2011

#### **Abstract**

Micro-Electro-Mechanical-Systems (MEMS) take advantage of a wide range of very reliable, and well established existing microelectronics fabrication techniques. Due to the planar nature of these techniques, out-of-plane MEMS devices must be fabricated inplane and assembled afterwards in order to create out-of-plane three-dimensional structures. Out-of-plane microstructures extend the design space of the MEMS based devices and overcome many limitations of the in-plane processing. Nevertheless, several issues have to be addressed in order to integrate an out-of-plane structure into an existing process. These include robustness, yield, reliability, assembly technique, packaging and so forth. In this thesis we introduce an inorganic based post-CMOS compatible process upon which the mechanical structure for out-of-plane micro sensors and actuators can be fabricated. The hinge-less out-of-plane microstructures (compliant mechanisms) are mechanically robust structures that provide reliable electrical connection to the devices that are rotated out-of-plane. Fabrication of these structures by inorganic materials introduces several challenges to the process that have to be addressed.

Fabrication of micromechanical structures by silicon micromachining could significantly modify the topography of the substrate, which results in non-planarity and degradation of the mechanical performance of the structures. On the other hand, the residual stress of the structural layer has profound effect on the final shape of the out-of-plane microstructures. In particular, stress non-uniformity can cause severe structural deformation which deteriorates the device performance (e.g. linearity, sensitivity, and dynamic range), or can make the device assembly difficult or sometimes impossible.

To overcome the topography issue related to the freestanding structures and to control the stress profile of their structural layer, we have developed two novel techniques. The first technique is an unconventional planarization process that is achieved by modifying the etch property of the sacrificial layer. The second technique compensates the stress non-uniformity across the thickness of the sputter-deposited films by in-situ control of the film property during the deposition process. The practicality and versatility of these techniques has been illustrated through the fabrication of a functional out-of-plane three-axis thermal accelerometer, which has a significant and growing share in the consumer electronics market.

**Keywords**: Planarization; Stress Anisotropy; 3-axis Thermal Accelerometer; Nickel

Silicide; Out-of-plane; Micromachining

To my loved ones

# **Acknowledgements**

I wish to express my deep gratitude towards my senior supervisor professor Albert M. Leung for his supervision, support and precious advices over the years.

I am very thankful to my supervisors, Dr. Ash M. Parameswaran, and Dr. Behraad Bahreyni for their comments and advices. My gratitude also goes to Dr. Marek Syrzycki, and Dr. Karim Karim for accepting to be my thesis examiner and patiently reading my thesis and providing valuable feedbacks. I would like to thank Dr. Jie Liang, for chairing my thesis defence.

I would like to express my sincere thanks to Ms. Eva Czyzewska, and Mr. Bill Woods for their many helps in the Engineering Science cleanroom facility.

# **Table of Contents**

|                   | roval                                                    |     |

|-------------------|----------------------------------------------------------|-----|

| Part              | tial Copyright Licence                                   | iii |

| Abst              | tract                                                    | iv  |

| Ded               | lication                                                 | V   |

| Ackr              | nowledgements                                            | vi  |

| Tabl              | le of Contents                                           | vii |

| List              | of Figures                                               | ix  |

|                   | of Tables                                                |     |

|                   |                                                          |     |

|                   | heter death a                                            | 4   |

| 1.                | Introduction                                             |     |

| 1.1.              |                                                          |     |

| 1.2.              |                                                          |     |

|                   | Motivation                                               |     |

| 1.4.              | Chapters outline                                         | 4   |

|                   |                                                          |     |

| 2.                | Planarization                                            | 5   |

| 2.1.              | Planarization techniques                                 | 6   |

| 2.2.              | Nickel silicide                                          | 9   |

| 2.3.              | Design considerations                                    | 12  |

|                   | 2.3.1. Nickel deposition (evaporation versus sputtering) | 12  |

|                   | 2.3.2. The etch-stop layer                               |     |

| 2.4.              | Planarization process                                    |     |

|                   | Planarization process results                            |     |

|                   |                                                          |     |

| 3.                | Stress anisotropy                                        | 25  |

| <b>3.</b><br>3.1. |                                                          |     |

| 3.2.              | 1                                                        |     |

| 3.3.              | 3                                                        |     |

| 3.4.              | ·                                                        |     |

| 3.4.              | Compensation process and results                         | 30  |

|                   |                                                          |     |

| 4.                | Application                                              |     |

|                   | Out-of-plane structures and Assembly techniques          |     |

| 4.2.              |                                                          |     |

|                   | 4.2.1. Operation principle                               |     |

|                   | 4.2.2. 3-axis thermal accelerometer                      |     |

|                   | 4.2.3. Split-heater 3-axis thermal accelerometer         |     |

| 4.3.              | Accelerometer design                                     | 59  |

|                   | 4.3.1. Sensor plate                                      | 59  |

|                   | 4.3.2. Main cantilever and locking mechanism             | 61  |

|                   | 4.3.3. Anchor and bonding pads                           |     |

| 4.4.              | <b>~</b> •                                               |     |

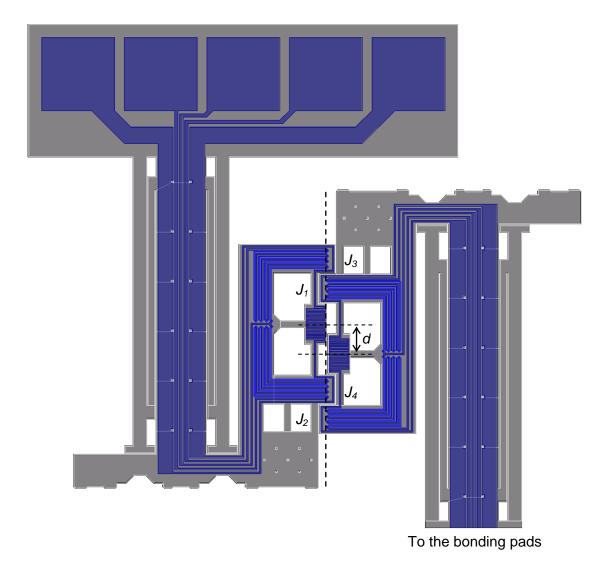

|                   | 4.4.1. Sensor layout                                     | 62  |

|                   | 4.4.2. Sensor fabrication                                |     |

|                   | 4 4 3 Test result                                        | 70  |

| 5. (                  | Contributions and future works |                                                    | 72              |

|-----------------------|--------------------------------|----------------------------------------------------|-----------------|

| 6. (                  | Conclus                        | ion                                                | 75              |

| <b>Apper</b><br>Appen | ndix<br>ndix A                 | 3-axis thermal accelerometer fabrication run-sheet | <b>77</b><br>78 |

| Refere                | ences                          |                                                    | 84              |

# **List of Figures**

| Figure 1:  | A freestanding microstructure fabricated using conventional sacrificial surface micromachining.                                                                                                                                                                                     | 5  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2:  | Planarization by re-sputtering (ion-milling).                                                                                                                                                                                                                                       | 8  |

| Figure 3:  | The thickness ratio between nickel, nickel silicide, and silicon consumption in the nickel mono-silicide (NiSi)                                                                                                                                                                     | 10 |

| Figure 4:  | Stress induced humps on silicide sample after annealing at 350°C.  There is no stress-hump over the areas covered by the oxide diffusion mask                                                                                                                                       | 14 |

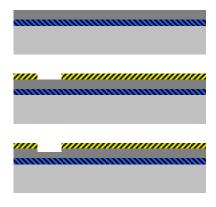

| Figure 5:  | Fabrication steps of the planarization process. <sup>†</sup> For illustration clarity, the composite oxide/NiCr/oxide layer is shown as a single structural layer.                                                                                                                  | 19 |

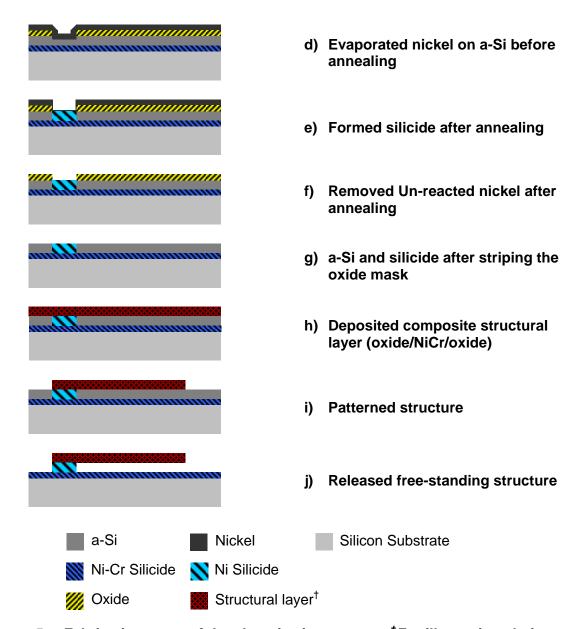

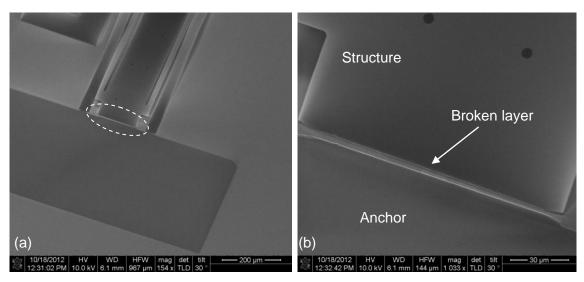

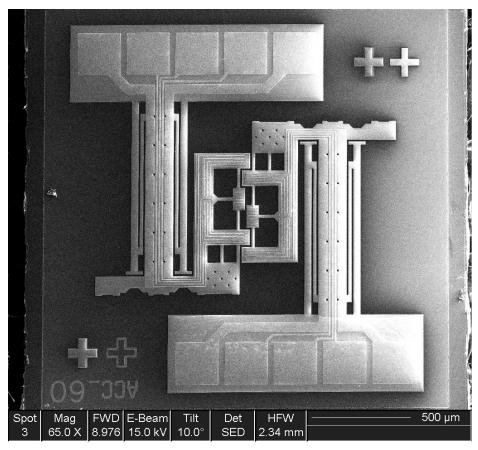

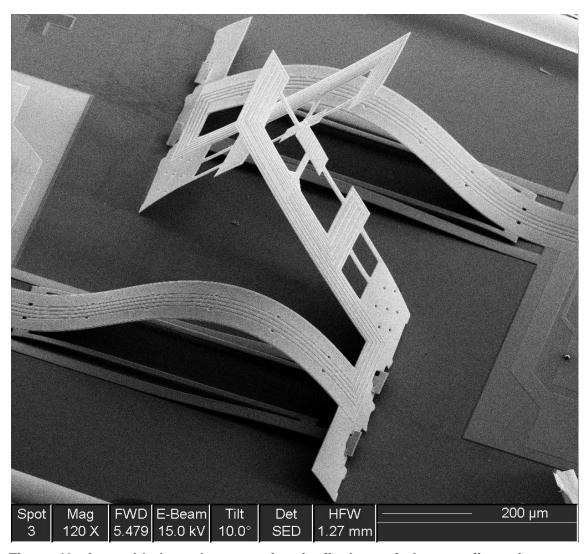

| Figure 6:  | a) SEM image of a compliant mechanism fabricated by our process.  The structure has been pushed out of plane and locked in place. b)  Structure's anchor.                                                                                                                           | 21 |

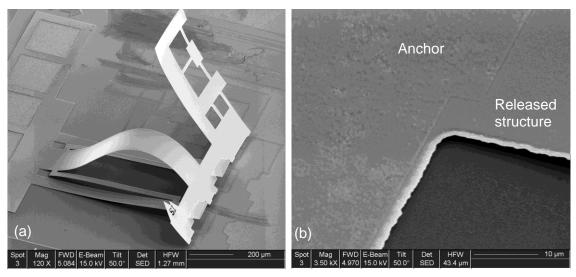

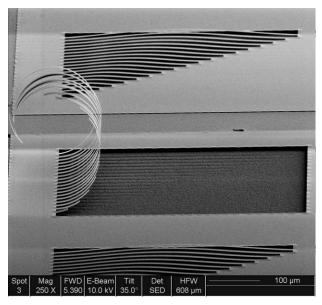

| Figure 7:  | A milled trench into the substrate using FIB reveals the cross section of different layers. Notice that the anchor and sacrificial layer have the same thickness, and the structural layers are virtually planar. Please refer to the figure 5.h for the schematic of the structure | 22 |

| Figure 8:  | a) A failed structure at its anchor during the assembly process (structure anchor is marked with an oval). b) The close-up image of the structure's anchor (marked area in Figure 8.a)                                                                                              | 23 |

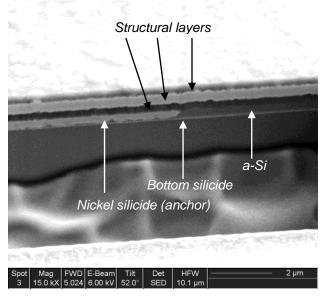

| Figure 9:  | Effect of stress anisotropy across the thickness of a sputter-deposited Nichrome film.                                                                                                                                                                                              | 27 |

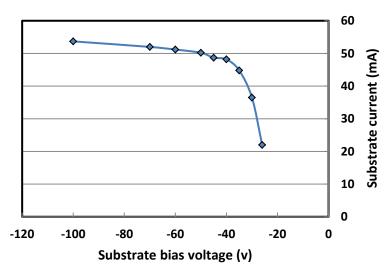

| Figure 10: | Substrate current versus substrate potential                                                                                                                                                                                                                                        | 32 |

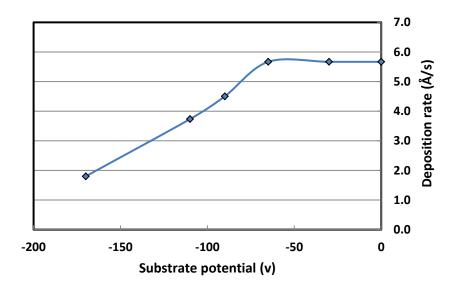

| Figure 11: | Drop in the deposition rate due to the re-sputtering at high bias voltages.                                                                                                                                                                                                         | 33 |

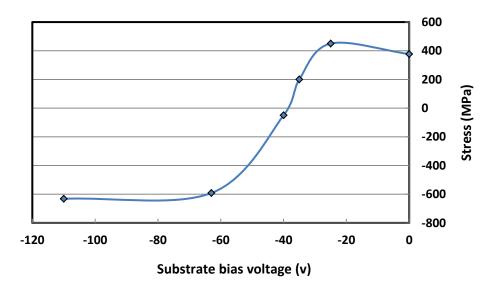

| Figure 12: | Variation in the average stress of a 300 nm thick Nichrome film with respect to the substrate potential.                                                                                                                                                                            | 35 |

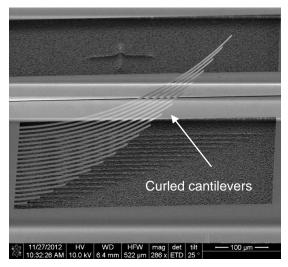

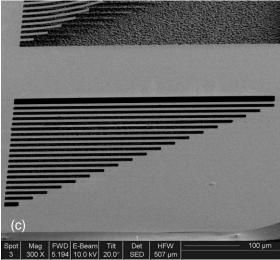

| Figure 13: | Array of 300 nm thick Nichrome cantilevers deposited at room temperature with zero bias voltage.                                                                                                                                                                                    | 38 |

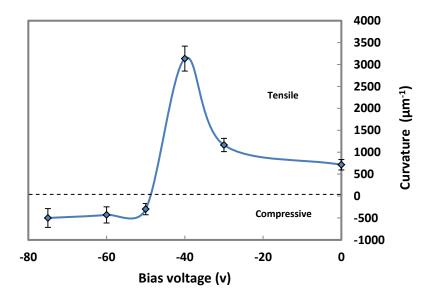

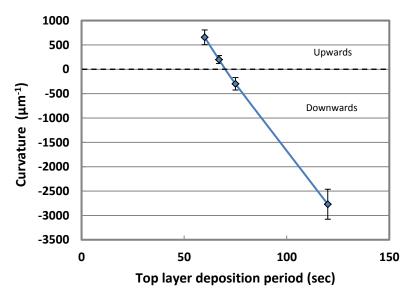

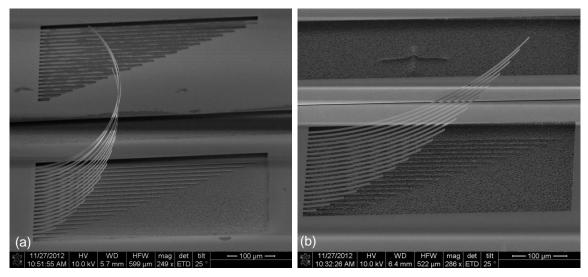

| Figure 14: | Curvature of released cantilevers at different bias voltages with a fixed compensating layer thickness. The transition voltage for the compensating layer lies between -40 to -50 volts.                                                                                            | 30 |

|            |                                                                                                                                                                                                                                                                                     |    |

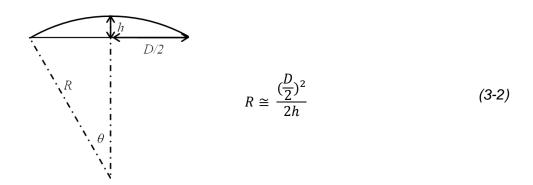

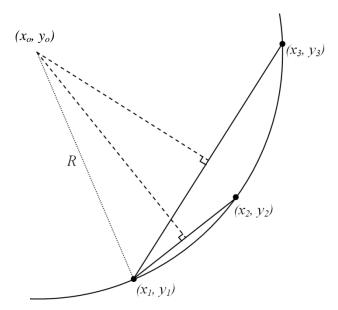

| Figure 15: | The center of curvature is where the centerlines of the two chords intersect                                                                                                                                                  | 40 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 16: | Change in the cantilever curvature with variable compensating layer thickness. The desired deposition time can be extracted from the graph at its zero crossing.                                                              | 41 |

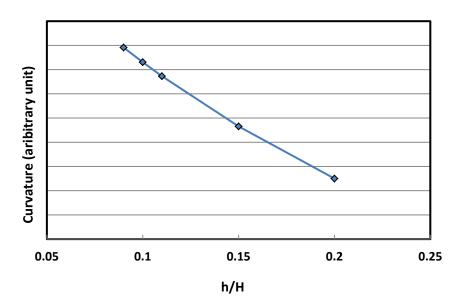

| Figure 17: | Estimated variation in curvature of a bimorph film with respect to the h/H ratio                                                                                                                                              | 42 |

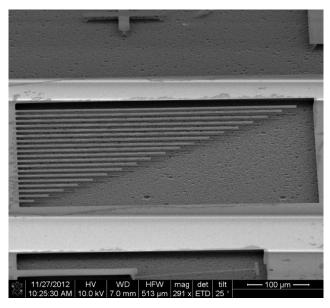

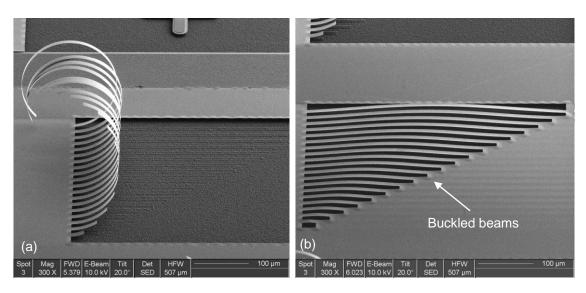

| Figure 18: | Array of cantilevers deposited at room temperature with a variable bias voltage.                                                                                                                                              | 43 |

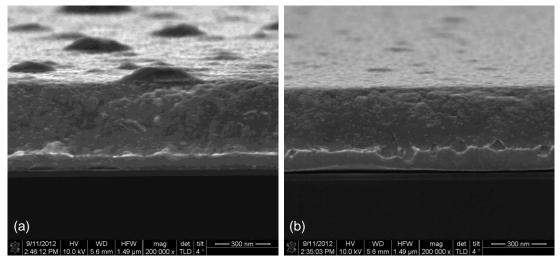

| Figure 19: | Cross section of the deposited films (a) without and (b) with variable bias voltage.                                                                                                                                          | 44 |

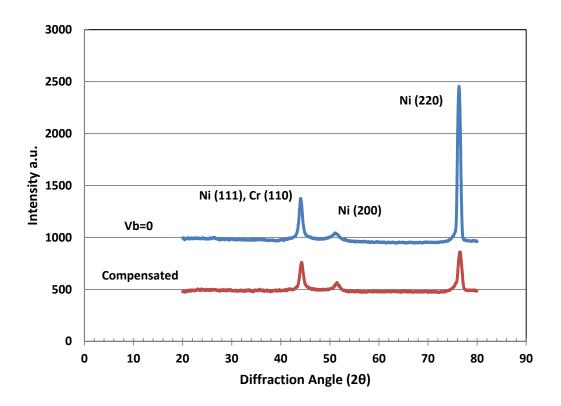

| Figure 20: | X-ray diffraction pattern of Nichrome films deposited with and without bias voltage. Note that curves have a vertical offset for clarity                                                                                      | 45 |

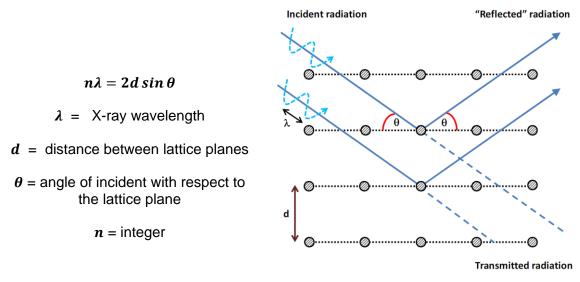

| Figure 21: | Braggs' law for constructive interference of reflected (scattered) x-ray from atoms of a crystal. Source, http://cc.usst.edu.cn/Download /26da9cdf-6134-41fc-bf56-6dcccd9edd20.pdf, retrieved May 12, 2013                    | 46 |

| Figure 22: | The deposited and released structures at room temperature with constant bias voltage at -110 volts. (a) An array of cantilevers. (b) An array of clamped-clamped beams. (c) An array of beams deposited at zero bias voltage. | 47 |

| Figure 23: | The effect of deposition temperature on the vertical stress gradient. (a) An array of cantilevers deposited at 150°C. (b) The same cantilevers deposited at room temperature.                                                 | 48 |

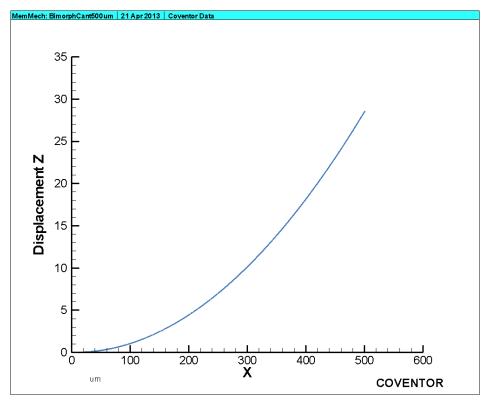

| Figure 24: | Simulation result of a bimorph film at elevated temperature                                                                                                                                                                   | 49 |

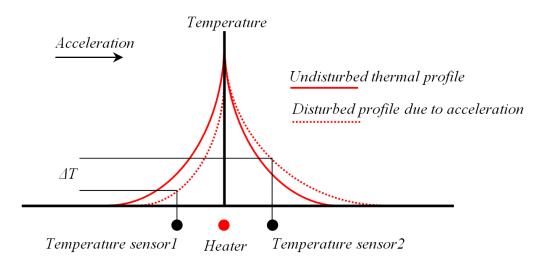

| Figure 25: | Non-disturbed and disturbed temperature profile around a heater                                                                                                                                                               | 53 |

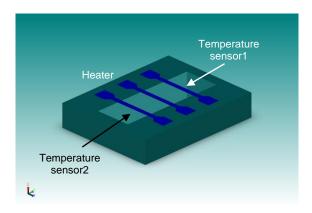

| Figure 26: | A simple depiction of a single-axis thermal accelerometer                                                                                                                                                                     | 54 |

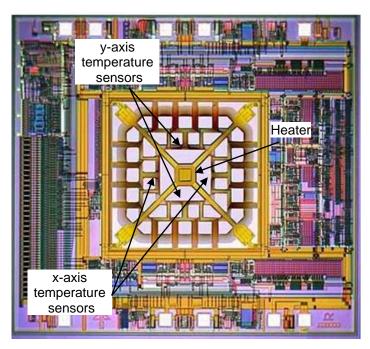

| Figure 27: | A dual-axis thermal accelerometer. Source, http://www.memsic.com/technology/thermal-mems.cfm, retrieved May 12, 2013                                                                                                          | 54 |

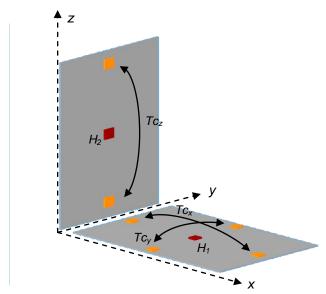

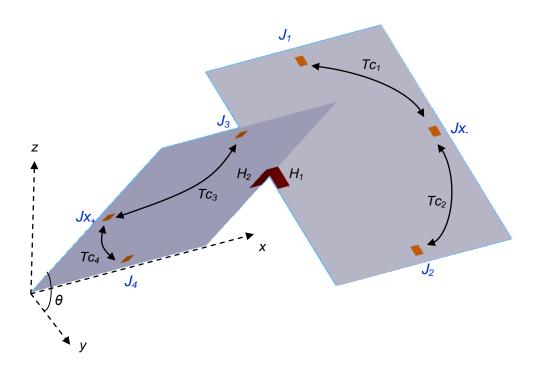

| Figure 28: | 3-axis accelerometer with z-plate implementation                                                                                                                                                                              | 56 |

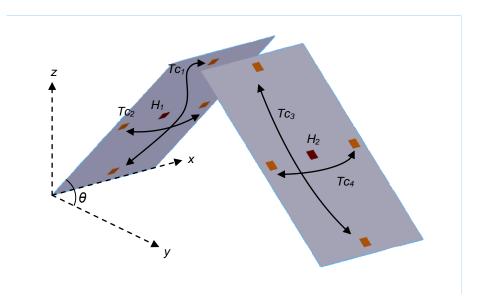

| Figure 29: | 3-axis accelerometer with two tilted out-of-plane sensor plates                                                                                                                                                               | 57 |

| Figure 30: | Schematic of an assembled split-heater 3-axis accelerometer.                                                                                                                                                                  | 58 |

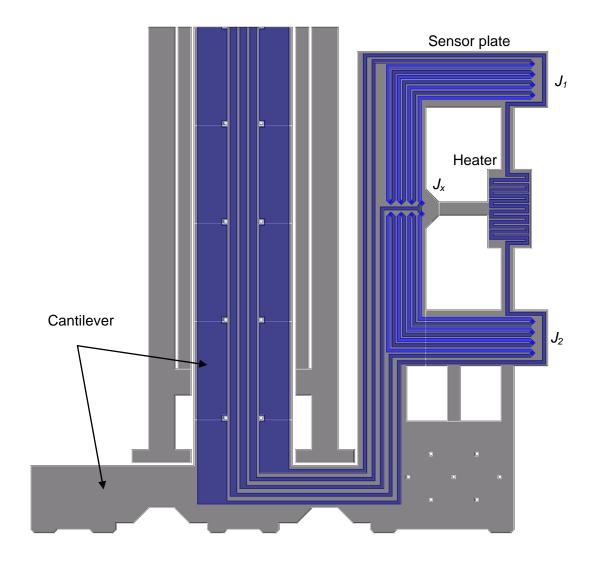

| Figure 31: | Layout of the sensor plate with the heater and the thermopiles                                                                                                                                                                | 60 |

| Figure 32: | The buckled main cantilever with the locking mechanism                                                                                                                                                                        | 62 |

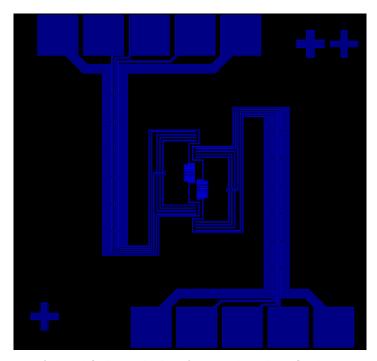

| Figure 33: | Layout of the split-heater accelerometer.                                                                       | 63 |

|------------|-----------------------------------------------------------------------------------------------------------------|----|

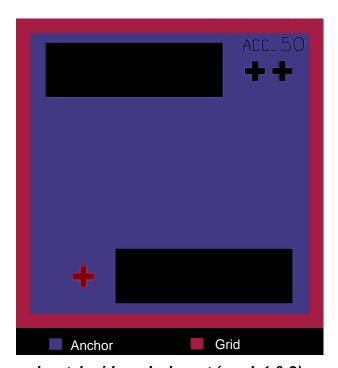

| Figure 34: | Fabricated accelerometer before release and assembly steps                                                      | 64 |

| Figure 35: | Anchor and metal grid masks layout (mask 1 & 2)                                                                 | 65 |

| Figure 36: | Layout of the third mask that forms the electrical connections, the heater, and the bonding pads.               | 66 |

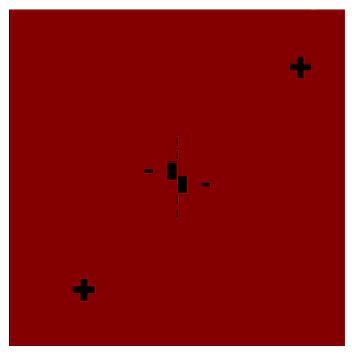

| Figure 37: | The fourth mask (dark-field) layout. It was used to remove the aluminum from undesired areas                    | 67 |

| Figure 38: | The fifth mask layout. It was used to lift-off the NiCu alloy for the thermocouple's second junction.           | 68 |

| Figure 39: | Layout of the sixth mask. It was used to pattern the structural layer                                           | 68 |

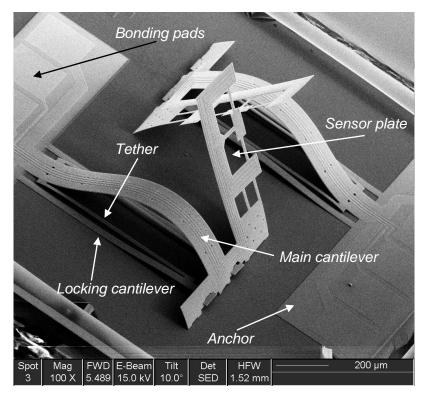

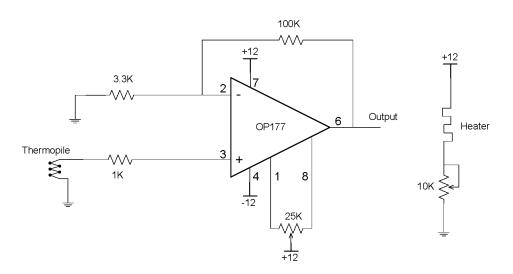

| Figure 40: | Assembled accelerometer into its final out-of-plane configuration                                               | 69 |

| Figure 41: | Amplifier circuit for the thermopiles.                                                                          | 70 |

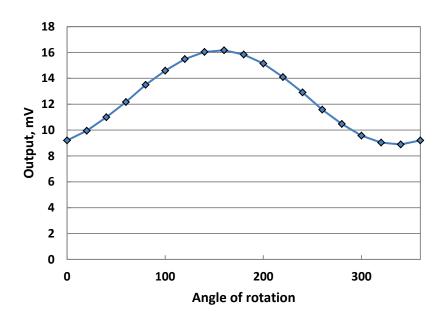

| Figure 42: | Single thermopile output with respect to the angle of rotation                                                  | 71 |

|            |                                                                                                                 |    |

| List of    | Tables                                                                                                          |    |

| Table 1:   | The thickness ratio between nickel, nickel silicide, and silicon consumption in the nickel mono-silicide (NiSi) | 10 |

| Table 2:   | Comparison of oxygen concentration in sputtered and evaporated nickel films                                     | 13 |

#### 1. Introduction

Micro-Electro-Mechanical-Systems (MEMS) take advantage of a wide range of very reliable and well established microelectronics fabrication techniques. Due to the planar nature of these techniques, most out-of-plane MEMS devices are first fabricated in-plane and then assembled in order to create high aspect ratio three-dimensional structures. Out-of-plane micro structures extend the design space of the MEMS based devices and overcome many limitations of the in-plane processing. Nevertheless, several issues have to be addressed in order to integrate an out-of-plane structure into an existing process. These include robustness, yield, reliability, assembly technique, packaging and so forth.

In this thesis we introduce a post-CMOS compatible process, based on inorganic thin films, upon which the mechanical structure for out-of-plane micro sensors and actuators can be fabricated. The hinge-less out-of-plane microstructures are mechanically more robust than the hinged structures and provide reliable electrical connection to the devices that are rotated out-of-plane. These microstructures, also known as compliant mechanisms, gain the necessary mobility for their assembly process through deformation of their elastic component. Fabrication of these structures from inorganic materials introduces several challenges to the process that have to be addressed.

Fabrication of micromechanical structures for sensors and actuators by silicon micromachining could significantly modify the topography of the substrate, which results in non-planar surfaces and therefore, degradation of the mechanical performance of the structures. On the other hand, the residual stress of thin films, which form the structural layer of the out-of-plane microstructures, has profound effect on the final shape of the freestanding and out-of-plane microstructures. In particular, stress non-uniformity can cause severe structural deformation which deteriorates the device performance (e.g.

linearity, sensitivity, and dynamic range), or it makes the device assembly difficult or sometimes impossible.

To overcome the topography issue related to the freestanding structures and to control the stress profile of their structural layer, we have developed two novel techniques. The first technique is an unconventional planarization process that is achieved by modifying the etch property of the sacrificial layer. The second technique compensates the stress non-uniformity across the film thickness by in-situ control of the film property during the deposition process. The practicality and versatility of these techniques will be illustrated through the fabrication of a functional out-of-plane three-axis thermal accelerometer, which has a significant and growing share in the consumer market. These processes are both low temperature and post-CMOS compatible.

# 1.1. Significance of out-of-plane structures

The limits of traditional lithographic microfabrication processes have constrained microelectronics and microelectromechanical systems to the substrate plane. While the commercially available surface micromachining, bulk micromachining and CMOS-based processes are able to create freestanding structures, the majority of these devices operate in the same plane as the substrate plane. Out-of-plane microstructures offer a completely new design space to create devices with advantages and capabilities previously not possible in ordinary planar structures. Out-of-plane microstructures have numerous applications in micro optical, thermal, and RF systems [1], [2], [3]. They can provide thermal isolation from the substrate that is necessary for many transducers, and can also add extra axes of sensitivity to the in-plane devices. The thermal accelerometer and gyroscope are prime examples of the potentials of these structures [3], [4].

# 1.2. Inorganic versus organic

Many researchers [5], [6] have demonstrated the possibility of fabricating out-ofplane structures using organic materials such as SU8, PMGI (Polymethylglutarimide), Polyimide, etc. Polymers in general have much lower Young's modulus to yield strength ratio than most silicon based materials and metals, and hence are mechanically more suitable materials to create compliant mechanisms; structures which are expected to undergo large deformation. However, practical difficulties in integrating a polymer-based fabrication technology into existing silicon-based processes have hindered the industry from adopting such processes. The most important and inherent drawbacks of using an organic material in a silicon based microfabrication foundry are deformation of the structures under long-term stress and contamination. Many polymers still out-gas even when they are cured. The out-gassing makes working with these materials very difficult in vacuum systems. Organic material easily re-sputtered in many common processes such as Reactive Ion Etching (RIE) and sputtering. The re-sputtered material covers the equipment chamber and cause cross-contamination. Sputtered non-organic films easily lose their adhesion to the bottom layers due to this contamination. Furthermore, the resputtered organic material becomes trapped in the coating material and changes the mechanical and chemical property of the film. Using the non-organic material such as metals or silicon-based materials (oxide, nitride, etc) eliminates these problems.

#### 1.3. Motivation

The needs of the MEMS industry are the driving force behind this research. A low-cost, low temperature and reliable process for fabricating out-of-plane structures broadens envisioning for new devices that can thrive in today's highly competitive market. The work presented in this thesis introduces an inorganic based post-CMOS compatible method upon which out-of-plane transducers can be created. While in this thesis we do not insist on fabrication of a particular transducer, but the three-axis thermal accelerometer was chosen to demonstrate a real-world application because of its market potential, ease of design and characterization, and well-studied operating principles [3].

# 1.4. Chapters outline

The planarization technique for eliminating the step between a structure and its anchor is presented in chapter 2. In chapter 3 we introduce a compensation technique to overcome the effect of stress anisotropy across the thickness of the sputter-deposited films. A generic application for these two techniques is illustrated in chapter 3, where the fabrication process for a 3-axis thermal accelerometer is explained, and the test result is presented. A detailed run-sheet of the fabrication steps for the thermal accelerometer is included in Appendix A.

#### 2. Planarization

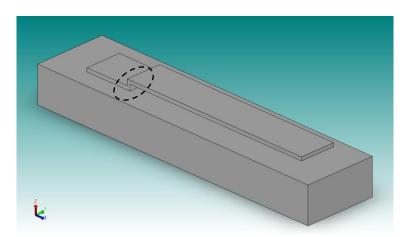

Fabrication of micromechanical freestanding structures for sensors and actuators by silicon micromachining could modify the topography of the substrate significantly [7]. In conventional surface micromachining (e.g. POLYMUMPS), 0.5-2 µm phosphosilicate glass (PSG) is often used as a sacrificial layer. The patterning of the PSG layer creates surface non-planarity. This surface non-planarity will result in a structure with a step, as shown in Figure 1. Local stress concentration may take place at the corners of these steps, which degrades the mechanical performance of the structure. During the actuation or assembly of an out-of-plane structure, stress accumulation at the structure's step can easily exceed the yield strength of the material and lead to the structure failure. Furthermore, the non-planarity results in complications in subsequent processing associated with lithography and step coverage, as in the case of multilayer interconnection of modem integrated circuit fabrication [7]. These difficulties include: variations in resolution and line width near the steps due to the limited depth of focus of exposure systems, and possible discontinuous metal or dielectric coverage of features with vertical sidewalls [7]. Therefore, planarization is important to increase the mechanical robustness of the structures, and the fabrication process yield.

Figure 1: A freestanding microstructure fabricated using conventional sacrificial surface micromachining.

The planarization technique presented in this chapter takes advantage of the nickel silicide technology to enhance the reliability of the freestanding structures and the compliant mechanisms by:

- Increasing the stiffness and mechanical robustness of the structures by eliminating the step between the structure and its anchor, and achieving planarization without using Chemical Mechanical Polishing (CMP).

- Eliminating the step coverage issue related to the deposition processes.

We use a layer of amorphous silicon (a-Si) as a sacrificial layer, which is locally converted to nickel silicide to form the anchors. High etch selectivity between silicon and nickel silicide in the Xenon Difluoride (sacrificial layer etchant) enables us to use the silicide to anchor the structures to the substrate. The formed silicide has the same thickness as the sacrificial layer; therefore, the structure is practically flat.

## 2.1. Planarization techniques

Different planarization techniques of the substrate surface for IC fabrication have been developed. The level of planarization varies significantly from one method to the other. It could be as little as tapering the sharp corners of the formed structures without change in the surface level across the wafer due to the substrate topography, and as far as a completely planar surface across the wafer. Followings are the most common planarization techniques:

- Reflow of doped silicon dioxide

- Reflow of metals (aluminum alloys)

- Re-sputter deposition

- Selective deposition of Chemical Vapour Deposition (CVD) tungsten

- Spin-on glass

- Plasma etch back of sacrificial layer

- Chemical Mechanical Polishing (CMP)

Low Pressure Chemical Vapour Deposition (LPCVD) deposited silicon dioxide requires high annealing temperatures to gain sufficient reflow for reducing substrate topography. A PhosphoSilicate Glass (PSG) requires temperatures in excess of 1000°C

to reflow significantly [8]. However, BoroPhosphoSilicate Glass, BPSG, yields a better performance as it reflows at temperatures below 900 °C; nevertheless, the reflow temperature of the film strongly depends on its phosphorous and Boron content [8]. Due to its extremely high thermal budget, this technique has limited application.

Metal reflow can also be used as planarization technique in processes that involve aluminum or aluminum alloy (aluminum-copper) as a contact or via material. In this process, the wafer is heated to 450-500°C to help fill the vias and planarize the surface. Introducing germanium to the film can reduce the reflow temperature to below 400°C [9]. Aluminum-Copper deposition with conventional techniques results in voids, gaps and poor via filling. By reacting Germane (GeH<sub>4</sub>) with the as deposited Al-Cu film, high aspect ratios vias can be filled without leaving any voids [9]. However, all reflow techniques result in local and partial surface planarization and the wafer's overall topography remains the same.

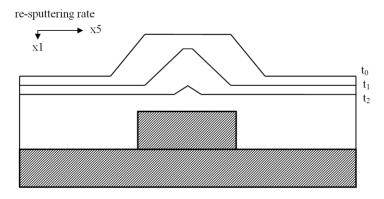

In the biased sputter deposition process, due to the energetic ions that bombard the growing film, deposition and sputter-etching (re-sputtering) can take place at the same time. The relative rate of each process depends on the ion flux, angular distribution and the ion energy. The re-sputtering rate (yield per incoming ion) is relatively low when the incoming ions arrive at shallow angles, and it reaches its maximum when the angle of incident is around 60° [10]. This rate rapidly declines and becomes very low again when the ions hit the surface at right angle. In biased sputtering, different facets can be formed, or removed because re-sputtering yield is different at different angles. During sputter-deposition of a film on a structured substrate, surface features can be eliminated by properly controlling the bombarding ions angle of incident. If re-sputtering rate on the side walls of the surface features is higher than the deposition rate, as the film becomes thicker, the size of these features become smaller and they will eventually disappear [10]. The angle of incident can be controlled by the bias voltage which defines the ion energy. The same technique can be used to planarize thick films using Ion Milling. Figure 2 illustrates the effect of faster milling rate on the sidewalls of a thick non-planar film and its subsequent planarizing outcome. Although surface planarization can be achieved by tuning the deposition and re-sputtering rate, at high re-sputtering rates surface damage and void formation can occur in narrow spaces (e.g. via bottom) [11].

Figure 2: Planarization by re-sputtering (ion-milling).

Tungsten selective deposition on silicon substrate by Chemical Vapour Deposition (CVD) is a practical technique to fill in small via holes in multilevel metal integrated circuits [12]. When silicon dioxide is used as the dielectric and insulation layer on silicon, via holes can be filled by tungsten plugs by a two phase CVD process. Initially, tungsten hexafluoride gas (WF $_6$ ) reacts with the silicon surface and a thin layer of tungsten is deposits on the bottom of the vias. The thickness of this layer is limited because when the exposed silicon is covered by the tungsten layer, the reaction stops. For the second phase of the deposition, hydrogen is introduced. Tungsten hexafluoride reacts with the atomic hydrogen (hydrogen reduction) and tungsten is deposited. The disassociation of the H $_2$  to atomic hydrogen easily takes place at the metal surface but not on the dielectric surface; therefore the overall deposition process is selective. Although this process has demonstrated the ability to fill via holes, there are many problems that have hindered the adoption of technology by the industry (lateral growth, tunnelling).

Spin-on Glass (SOG) is either a mixture of silicon dioxide in a solvent with zero organic content, or a Siloxane (Si-O-Si linkage) polymer chain. The properties and functionality of spin-on glass materials is largely controlled by the various components of the polymer structure. Spin-on glass can be spun like a photoresist layer but it turns to SiO<sub>2</sub> when it is baked and cured. Due to its low viscosity, the spin-on glass can fill in the holes and planarize the substrate surface. The major problems with the spin-on glass are the organic content of the film even after proper curing of the film and the poor quality of the oxide (compare to the CVD or thermal oxide). Spin-on glass can also be used in the plasma etch back planarization process as the sacrificial layer [13]. The

advantage of using spin-on glass instead of other polymers in etch back planarization process is that the spin-on glass can be spun into much thinner layers (less and 100 nm).

In plasma planarization [7], a low viscosity sacrificial layer (usually photoresist, polyimide or spin-on glass) is used to coat the uneven substrate surface to obtain a practically flat surface. Subsequently, plasma etching is used to etch-back the sacrificial coating layer, during which the etch rate of substrate and sacrificial layer should be equal to form a planar surface after the etching. Coating of a structured substrate even with a low viscosity polymer could result in an uneven surface. This issue is more significant when the surface feature density varies (micro-loading) and could result in local planarization.

Once considered a technique too crude and dirty for IC fabrication, CMP emerged as a new method of achieving complete planarization for submicron ULSI applications [14], [15]. With the correct polishing pad, slurry, and planarizing machine tool, thin layers of insulating material and even metals can be removed and brought down to the point where eventually the layer is a plane surface. However, this method suffers from difficulties in planarity control (feature size dependency, hollow formation in wide features, over-polishing of large array areas), and residual contaminations [7].

#### 2.2. Nickel silicide

Silicides have been extensively used in the CMOS technology to reduce the series and the contact resistance to the gate, source and drain regions [16]. Nickel silicide's lower thermal budget, lower resistivity, reduced silicon consumption, and nickel-diffusion-controlled formation have overcome the limitations of the cobalt silicide (CoSi<sub>2</sub>), and made the nickel silicide the first choice for CMOS technologies below 65nm [17], [18]. The fact that formation of nickel silicide is controlled by nickel diffusion is a significant advantage which results in silicide films with much smoother surfaces and interfaces [18].

Nickel silicide has different phases, but numerous reports agree that the predominant phases are Ni<sub>2</sub>Si, NiSi, and NiSi<sub>2</sub> [17]. The Ni<sub>2</sub>Si forms at the temperature

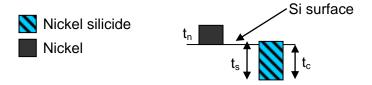

range of 250-300°C, but above 300°C it transitions rapidly to NiSi. At higher temperatures (above 600°C) the mono-silicide transforms to NiSi $_2$  [18]. Figure 3 illustrates the correlation between nickel initial thickness,  $t_n$ , the formed silicide thickness,  $t_s$ , and the consumed silicon thickness,  $t_c$ , for nickel mono-silicide phase (NiSi). The formed silicide is 2.2 times as thick as the initial nickel, and consumed silicon thickness is 1.83 times as much. As it is shown in the figure, the formed silicide grows slightly above the initial silicon interface. The protrusion is only 16.8% of the total silicide thickness,  $t_s$  [18].

Figure 3: The thickness ratio between nickel, nickel silicide, and silicon consumption in the nickel mono-silicide (NiSi).

Table 1 compares the crystalline properties of nickel silicide at its different phases [18]. Silicon rich nickel silicide (NiSi<sub>2</sub>) has the largest silicon consumption ratio to the nickel initial thickness among the predominant phases. This high ratio is an advantage when thick layer of silicon has to be converted to silicide. However, the formation temperature of this phase (above 600°C) is too high to be adopted by our process. Above 350°C, the nickel silicide film mostly consists of NiSi. This temperature is low enough for a post-CMOS compatible process, and amorphous silicon (the sacrificial layer) can also be deposited at these temperatures by taking advantage of PECVD technique.

Table 1: The thickness ratio between nickel, nickel silicide, and silicon consumption in the nickel mono-silicide (NiSi).

| Phase              | t <sub>n</sub> | t <sub>s</sub> | t <sub>c</sub> |

|--------------------|----------------|----------------|----------------|

| Ni <sub>2</sub> Si | 1              | 1.47           | 0.91           |

| NiSi               | 1              | 2.2            | 1.83           |

| NiSi <sub>2</sub>  | 1              | 3.61           | 3.66           |

Nickel silicide etch rate is very low or almost zero in most acids and chemicals [19]. The close-to-zero etch rate of the nickel silicide in XeF<sub>2</sub> gas makes it a good candidate for selectively etching the sacrificial layer in our process. The diffusion rate of nickel into silicon dioxide and nitride is extremely low. Therefore, these films can be used as a masking material to selectively diffuse nickel into silicon.

Mechanical properties and possible applications of the nickel silicide in MEMS have been studied by a few researchers [19], [20], [21]. Qin et al [19], [20], have measured electrical and mechanical properties (resistivity, surface roughness, Young's modulus, and stress) of the nickel silicide formed on polysilicon and crystalline silicon substrate. They even managed to fabricate simple mechanical structures like microbridges and micro-cantilevers using silicon dioxide as diffusion mask. Bhaskaran et al [21], took advantage of high etch resistivity of nickel silicide, and used it as etch mask in silicon bulk micromachining in potassium hydroxide. We were the first group that introduced a planar surface micromachining process using nickel silicide [22]. This process enabled us to improve the performance of a Pirani pressure sensor in atmospheric pressures by reducing the device gap size to 50nm. To extend the application of our process to the other micro sensors and actuators, we had to enhance and modify the original method [23], [24].

Conventionally, the fabrication of a freestanding structure starts with deposition and patterning of a sacrificial layer. The structural layer is deposited afterwards. The structure is anchored to the substrate through the opening of the sacrificial layer. This process results in a non-planar structure with a step between the structure and its anchors, which is equal to the thickness of the sacrificial layer (Figure 1). Besides the mechanical degradation due to this height difference, deposition process of the structural layer has to be conformal, otherwise poor step coverage will further deteriorate the structure robustness. Instead of opening windows in the sacrificial layer to anchor the structure to the substrate, we locally modify the property of the sacrificial layer by converting it to silicide. The modified sacrificial layer is highly etch-resistant to the sacrificial layer etchant (XeF<sub>2</sub>). This process creates patches of highly etch resistant silicide in the sacrificial layer. During the release step (etching the sacrificial layer), the structure remains anchored to the substrate through these patches (Figure 5). The

formed silicide has the same thickness as the original layer which results in a planar structure.

# 2.3. Design considerations

Before describing the planarization process in detail, we have to emphasize on several criteria and principles upon which a particular material or an implementation strategy was chosen. During the development phase of the process, we sometimes had to replace a material for another to overcome an undesirable outcome, or completely substitute a process with a difference technique to meet our requirements. The materials and the processes selection criteria are discussed here.

#### 2.3.1. Nickel deposition (evaporation versus sputtering)

Nickel thin films can be deposited through several techniques such as, electroplating, electroless plating, sputtering and evaporation. The chemical based deposition techniques tend to leave some traces of other elements and compounds in the film which can hinder the silicide formation. On the other hand, pure elemental nickel can be deposited by sputtering or evaporation techniques. Sputtering is easy and convenient way of nickel deposition with good uniformity, and relatively fast deposition rates at moderate powers (up to 8 Å/s at 5.5 W/cm²). Nickel is a magnetic material with high magnetic permeability, and in order to sputter nickel from a magnetron (sputtering source with a magnet), one has to use very thin targets or use specially designed sputtering sources (with stronger or unbalanced magnets).

Alternatively, nickel can be deposited by thermal or e-beam evaporation. Nickel forms alloys with most of the common materials that are used as heater in the thermal evaporation; therefore, it has to be thermally evaporated from an alumina coated heater or basket. The melted nickel does not wet alumina and it forms a sphere with very large contact angle. The small contact area between the melt and the heater reduces the nickel evaporation rate. To compensate for the lower evaporation rate, the heater power rating has to be increased significantly which shortens the heater's life time and causes substrate heating the same time. Using e-beam evaporation alleviates the nickel thermal

evaporation challenges considerably but the evaporation rate is much lower than that of the sputtering. Nickel deposition rate using the e-beam technique is only a few angstroms per second (1-2 Å/s).

Nickel silicide films formed by annealing an evaporated nickel are known to be mono-silicide (NiSi), with the composition being very close to 50% nickel and 50% silicon. Sputtered nickel, unlike the evaporated nickel, requires more thermal effort to form NiSi. Sputtered nickel has to be annealed at temperatures as high as 600°C to form the mono-silicide [25], which is too high and incompatible for a post CMOS process.

We initially used a thin foil of nickel as the target to sputter-deposit nickel on silicon and to form silicide. We tried different deposition conditions but the sputtered film did not react with silicon after we annealed the film at 400°C. The analysis of the as deposited film (before annealing) by Electron Dispersive Spectroscopy (EDS) showed significant concentration of oxygen in the film (up to 14%). The high oxygen content of the film could be one of the main reasons that no silicide was formed at those conditions. The primary source of the oxygen in the sputtered film was from the exposure to the atmosphere and the microcrystalline structure of the film (high oxidation rate). This phenomenon could also be attributed to variations in the diffusivity of metals in silicon, based on the metal thin film deposition technique [25]. Repeating the same experiment with thermal or e-beam evaporated nickel resulted in formation of nickel silicide at temperatures as low as 350°C; therefore, we chose evaporation to deposit nickel in our process. Table 2 shows the difference in the oxygen concentration of a sputter deposited and an evaporated nickel film after exposure to the atmosphere.

Table 2: Comparison of oxygen concentration in sputtered and evaporated nickel films.

| Deposition method | O <sub>2</sub> (atomic %) | Ni (atomic %) |

|-------------------|---------------------------|---------------|

| Sputtering        | 14                        | 86            |

| Evaporation       | 5                         | 95            |

#### 2.3.2. The etch-stop layer

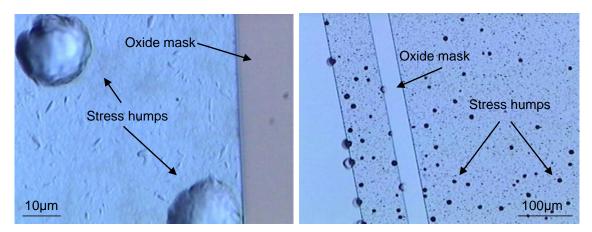

Before the sacrificial layer deposition and formation of the anchors, an etch-stop layer has to be deposited (formed) on the silicon substrate. This layer has to have a very low etch rate in Xenon Difluoride (XeF<sub>2</sub>) in order to protect the silicon substrate during the release step, otherwise the XeF<sub>2</sub> attacks the substrate. In addition to having a low etch rate in XeF<sub>2</sub>, this layer has to have another important characteristic; the sacrificial layer (a-Si) and the nickel silicide have to adhere very well to this layer. Without enough adhesion, the stress induced by the nickel, and the formed silicide during the annealing step could cause the film to delaminate from the substrate and form stress-humps (blisters) [26], [27]. Figure 4 shows the formed stress-humps on a sample with poor adhesion between the sacrificial and the etch stop layer (on silicon dioxide). The stress-hump formation becomes a major issue with relatively thick a-Si layers (a few hundreds of nanometres) [23].

Figure 4: Stress induced humps on silicide sample after annealing at 350°C.

There is no stress-hump over the areas covered by the oxide diffusion mask.

In order to apply our process to large structures (a few hundreds of microns across) and to facilitate the structure release process, we had to increase the sacrificial layer thickness to hundreds of nanometres. Even with etch holes in the structure, releasing a large structure with a very thin sacrificial layer (e.g. 100 nm) could be very

time consuming, and sometimes impossible. Lack of sufficient adhesion between the etch-stop and the top silicide layer limits the maximum thickness of the sacrificial layer.

The nickel-silicide based surface micromachining process that we initially introduced in [22] used thermal oxide as the etch-stop layer on the silicon substrate. The adhesion of the sacrificial layer and the formed nickel silicide to the bottom oxide layer was very poor, which had limited the process to the applications with extremely thin sacrificial layers (up to 100 nm). For thicker a-Si layers, nickel film thickness had to be increased to provide enough supply of nickel to completely consume the silicon and form the silicide (anchor). We noticed that as we increase the nickel thickness the stresshump formation becomes more significant and with nickel layers thicker than 100 nm the annealed film was covered with blisters. Obviously the expansion of the film during silicide formation results in high stress values and the force exerted by the film exceeds the film adhesion to the etch-stop layer which causes the film to delaminate from the bottom layer and form the stress humps.

Increasing the a-Si deposition temperature (up to 350°C) slightly improved the adhesion but we still observed major stress-hump formation with nickel layers thicker than 100 nm. We later attempted to replace the thermal oxide with another etch-stop layer. PECVD silicon nitride showed much better adhesion but unfortunately the etch rate of nitride is relatively high in XeF<sub>2</sub> and it is also a strong function of deposition parameters. PECVD silicon dioxide on the other hand stands to XeF<sub>2</sub> very well, but it did not show enough adhesion to the sacrificial layer and the formed nickel silicide to be considered for our process.

We came up with the idea of replacing the dielectric etch-stop with a thin layer of silicide in order to solve the adhesion problem. We thought that this layer diffuses both into the substrate and the a-Si layer and would become a bonding layer between the sacrificial layer and the substrate. Experiment with silicide revealed that the a-Si and the top silicide layer adhere much better to a thin layer of silicide compare to the other films such as oxide or nitride. In [23], we introduced a modified process which used a thin layer of nickel silicide as the bottom etch-stop layer. To form the silicide etch-stop layer we deposited a very thin layer of nickel (10 nm) by e-beam evaporation on the substrate

and deposited the PECVD a-Si on top of it. A short annealing step was required to from the bottom etch-stop layer.

With the available equipment (separate e-beam evaporator and PECVD machines), it was impossible for us to evaporate the bottom nickel and deposit the PECVD a-Si without breaking the vacuum (exposing the nickel film to atmosphere). Exposure to atmosphere partially oxidizes the nickel which deteriorates its adhesion to the a-Si and the top silicide layer after silicidation. Although replacing the bottom oxide layer with a layer of nickel silicide improved the film adhesion and reduced the stress hump formation significantly, nickel oxidation was still an issue which rendered the process hard to control and reproduce.

To avoid the exposure of nickel to atmosphere, we had to deposit the nickel in our Cluster Tool and then transfer the wafer to the PECVD chamber for the a-Si deposition without breaking the vacuum. In a Cluster Tool machine, different process chambers are connected to each other via an Ultra High Vacuum (UHV) Isolation and Transferring Zone (ITZ), and a robotic manipulator moves the sample between different chambers. However, the only available technique for nickel deposition in our system was sputtering. As we mentioned earlier, the sputtered nickel needs much higher thermal budget to react with silicon and to form silicide; therefore, we could not use the nickel to further improve the adhesion. It had to be replaced with another material.

Our experience with Nichrome (80% Nickel, 20% Chromium) had shown that it forms a very thin layer of silicide even when it is sputtered at room temperature. Biased sputtering followed by high temperature annealing (350°C) further enhances the silicide formation. The formed silicide at this temperature has excellent etch resistivity to XeF<sub>2</sub> and excellent adhesion to a-Si and nickel silicide. However, silicide formation is very sensitive to presence of oxygen during metal deposition and requires base pressures below 10<sup>-7</sup> Torr. Furthermore, film exposure to atmosphere after deposition hinders the silicide formation as well (similar to nickel). To avoid the Nichrome film exposure to the atmosphere before sacrificial layer deposition, the entire process was carried out in our Cluster Tool machine equipped with UHV processes and transfer chambers.

The experimental results with Nichrome were very promising and the formed Ni-Cr silicide showed excellent adhesion to the top layers. By monitoring the base pressure of the chamber before deposition and long enough pump-down period, the process was very well controlled and reproducible. We monitored the partial pressure of the different gas species in the chamber using a quadrupole Residual Gas Analyzer (RGA). This was a crucial step in our process since most pressure gauges are calibrated for nitrogen and partial pressure of other gas species in the chamber could be much higher (up to an order of magnitude) than the measured pressure by the gauge. Difference in the gas species partial pressure can significantly affect critical processes which are sensitive to the presence of certain gas types (water vapour in our case).

Turbomolecular pumps are the most common pumps in high vacuum systems. They provide high pumping speed (l/s) and sufficient compression ratio for different gas species. The compression ratio could be as high as  $10^9$  for nitrogen and as low as 1000 for lighter species like hydrogen. The pumping speed is also much lower for the lighter gases. Water vapour has the highest partial pressure among the other gas species in the chambers equipped with a turbomolecular pump due to its low compression ratio and pumping speed and its relatively high concentration at the pump outlet (atmosphere). Although the average pressure of the chamber can be brought down into the  $10^{-7}$  Torr range relatively fast (as can be verified by the gauge) the water vapour pressure in the chamber usually requires much longer pumping cycles and must be verified by RGA readout. In our sputtering chamber the base pressure drops below  $5x10^{-7}$  Torr in less than 5 minutes (after loading the sample), but the chamber has to be pumped down for more than an hour to reduce the water vapour pressure below  $5x10^{-7}$  Torr which is necessary to prevent the Nichrome oxidation and to promote the silicide formation.

# 2.4. Planarization process

Different steps of the planarization process is illustrated Figure 5. The thin etch-stop silicide layer is formed by sputtering 20 nm NiCr (Nichrome; 80% Nickel, 20% Chromium) on the silicon substrate. We used the MVSystem Cluster Tool for sputtering NiCr and for PECVD amorphous silicon deposition. Our Cluster Tool is equipped with two UHV sputtering chambers, two UHV PECVD chambers, and a UHV Isolation and

Transferring Zone (ITZ). For NiCr sputtering the chamber base pressure was below 10<sup>-7</sup> Torr, and during transferring the sample from the sputtering to the PECVD chamber the ITZ pressure was kept below 10<sup>-6</sup> Torr. After DC sputtering of 20 nm thick NiCr (Argon pressure 1 mTorr, 3" target at 150 Watts power rating, substrate bias -50 V) and transferring the sample into the PECVD chamber, 300 nm thick a-Si was deposited on the NiCr film. Amorphous silicon was deposited using pure Silane chemistry (chamber pressure 350 mTorr, substrate temperature 350°C, RF power 2 watts). The Nichrome:a-Si stack was annealed in a convection furnace at 350°C in forming gas atmosphere (5% hydrogen, balance in nitrogen) for 10 minutes to form the etch stop layer (bottom silicide). The forming gas prevents the a-Si from oxidation during the annealing process. Nichrome reacts with the silicon substrate and the a-Si layer at the same time, and it is totally consumed by the silicon to form the bottom silicide. Diffusion into both the substrate and the a-Si layer significantly improves the a-Si layer adhesion to the substrate and prevents the stress-hump appearance during the top silicide layer formation.

We used the FEI Nova NanoSEM 430 EDAX analyzer to study the formed silicide composition utilizing the Energy Dispersive Spectroscopy (EDS) technique. The analysis result showed that the nickel and chromium concentration of the silicide layer is very close to that of the sputtering target (nickel 80%, chromium 20%). The slight discrepancy in the film composition is perhaps due to the sputtering yield difference between nickel and chromium. The measured composition of the formed silicide film on the substrate was Si-60.92%, Ni-30.80%, Cr-8.28%.

- a) Sacrificial layer with bottom silicide layer

- b) Patterned diffusion mask (oxide)

- c) Partially etched a-Si layer in RIE with diffusion mask

Figure 5: Fabrication steps of the planarization process. †For illustration clarity, the composite oxide/NiCr/oxide layer is shown as a single structural layer.

After the sacrificial layer deposition and the bottom silicide layer formation, a 200 nm thick layer of PECVD oxide was deposited to act as a diffusion mask for the silicidation process. The first mask was used to open the anchor windows into the oxide layer. To compensate the growth of the nickel silicide above the original a-Si surface, part of the a-Si was etched by RIE using a mixture of CF<sub>4</sub> and oxygen (10:1). The a-Si etch depth was equal to the amount that the silicide grows above the surface. This

guarantees that the silicide layer has the same thickness as the a-Si layer. To form the silicide and make the anchors, a 200 nm thick nickel film was evaporated and annealed. We annealed the film in the forming gas atmosphere at 350°C for 45 minutes. We deposit enough nickel on silicon so that after annealing the a-Si is entirely consumed by the nickel to form the anchors (the top and bottom silicides actually merge). We used the Bestec e-beam evaporation system to deposit nickel. During evaporation the chamber pressure was about  $5x10^{-7}$  Torr and the deposition rate was about 1 Å/s. After annealing, the non-reacted nickel was etched by a mixture of  $H_2SO_4$  and  $H_2O_2$  (1:1) at  $70^{\circ}C$  for 5 minutes and the oxide layer was etched by Buffered Oxide Etchant (BOE). PECVD oxide etch rate in BOE was about 250 nm/min.

After the anchors were formed, we deposited and patterned the structural layer on the substrate to fabricate the desired mechanical structures. The mechanical structures were released and assembled manually using a mechanical probe to form an out-of-plane configuration.

The structural layer is a symmetrical tri-layer film consisting of two layers of PECVD oxide (250 nm thick each), on top and bottom of a Nichrome film (300 nm thick). The bottom oxide, Nichrome, and top oxide layers are deposited first and then patterned using a single mask with self-alignment technique. The top and bottom oxide layers were etched in RIE, and the Transene 1020AC Chromium etchant was used to wet etch the Nichrome film. The composite film minimizes the overall stress level of the structural layer, and the symmetry of the structure eliminates its deformation due to the stress mismatch between different layers [28]. We used  $XeF_2$  gas to etch the sacrificial layer and release the structure.  $XeF_2$  is a white crystal that sublimes with a vapor pressure around 4 Torr at room temperature. The  $XeF_2$  gas is an isotropic etchant for silicon. The etch rate of silicon in  $XeF_2$  is a strong function of exposed silicon, but it can reach as high as 4  $\mu$ m/min. The etch selectivity between silicon and silicon dioxide in  $XeF_2$  gas is better than 1:2000. The etch selectivity is much higher for most of the metals and the silicides [29], [30].

### 2.5. Planarization process results

Figure 6.a shows the SEM image of an assembled 3D compliant mechanism fabricated using our process. The close up view of the structure's anchor is shown in Figure 6.b. Although there is no height difference between the structure and its anchor, the anchor (the silicide) has a rougher surface compared to that of the structural layer which creates the illusion of having a discontinuous film. The structure is the sensor-plate of a 3-axis thermal accelerometer [3], which provides thermal insulation from the substrate for the sensor, and adds the third sensing axis (z-aixs) to the device. The structure has been buckled out of plane and locked in place [31], [32], [33]. To assemble the structure to the out-of-plane configuration, tip of the T-shape cantilever (main cantilever) is pushed back using a probe. When tip of the main cantilever passes the locking cantilever, the probe is retracted and the mechanism is locked in placed as it is shown in the image. To assemble the structure, tip of the main cantilever has to be slid back slightly more than 25% of the cantilever's original length and then released. During this process, stress is accumulated at the cantilever's anchor and the structural layer is most likely to fail.

Figure 6: a) SEM image of a compliant mechanism fabricated by our process. The structure has been pushed out of plane and locked in place. b) Structure's anchor.

Figure 7 shows a SEM image of the structure cross section (before the release step). To expose the structure cross section we milled a trench into the substrate using

Focused Ion Beam (FIB). It can be observed that the anchor and the sacrificial layer have the same thickness, and that the structural layers are practically planar. The bottom silicide layer (etch stop) is also clearly visible in the image. We used a surface profiler to examine the structure topography. The measured height difference between the anchor and the original a-Si surface was about 10 nm on a 300 nm thick sacrificial layer (Figure 6.b). This step could be a result of processes variation during a-Si etching, or inconsistency in the nickel silicide composition.

Figure 7: A milled trench into the substrate using FIB reveals the cross section of different layers. Notice that the anchor and sacrificial layer have the same thickness, and the structural layers are virtually planar. Please refer to the figure 5.h for the schematic of the structure.

The a-Si thickness governs the final thickness of the anchors, because nickel completely consumes the amorphous silicon to form the silicide regions. If the etch depth of the a-Si by RIE is not equal to the desired calculated depth, the final surface of the silicide could be lower or higher compare to the original a-Si surface. The other reason for this discrepancy could be the actual composition of the silicide layer. Our process calculations are based on the formation of a perfectly mono-silicide film after annealing. If the annealed film partially contains the other phases of the silicide, the final silicide thickness and the amount that it grows above the initial a-Si surface will be different. However, the actual thickness of the silicide layer and its growth rate can be measured and used to compensate the processes variations.

To study how much our process has improved the mechanical robustness and the assembly yield of the fabricated compliant mechanism, we compared the assembly yield of two sets of identical structures (Figure 6.a), fabricated with and without the proposed planarization technique. The fabricated structures without using our process were made by conventional surface sacrificial micromachining as was explained earlier in this chapter. We released and assembled forty structures from each sets of the fabricated mechanisms. All forty structures that were fabricated by our planarization technique were successfully assembled and locked in place. The assembly success rate for the devices fabricated by the conventional technique was less than 20%, and most of the cantilevers failed and snapped at their anchor when they were pushed backed to be assembled. Figure 8 shows the images of a failed mechanism and the broken structural layer at its anchor. The structure failure happens right at the step that was resulted from the substrate topography.

Figure 8: a) A failed structure at its anchor during the assembly process (structure anchor is marked with an oval). b) The close-up image of the structure's anchor (marked area in Figure 8.a)

We introduced an innovative sacrificial surface micromachining process that enhances the mechanical robustness of freestanding microstructures and compliant mechanisms. This process facilitates the fabrication, and improves the assembly yield of the out-of-plane micro sensors and actuators. Our process overcomes the topography issue related to the free-standing structures by eliminating the step between the structure and its anchor, and achieves planarization without using Chemical Mechanical

Polishing (CMP). The experimental results showed a significant improvement in the assembly yield of the compliant mechanisms that were fabricated by our proposed planarization technique.

# 3. Stress anisotropy

In freestanding structures, structural layer stress variation in different directions, or stress anisotropy, can severely distort the final shape of the released structure. Structural deformation can deteriorate the device performance (e.g. linearity, sensitivity, and dynamic range), or make the device assembly difficult or sometimes impossible. Therefore minimizing the stress anisotropy is a key issue in many applications that incorporate a free-standing or an out-of-plane structure. In many applications the released structure must remain flat and in-plane with the substrate; nevertheless, stress anisotropy or stress mismatch between different layers is a key element in the design of mechanisms such as self-assembly of out-of-plane structures, or 3D RF antennas [34].

Micromachining using polysilicon has a high thermal budget that limits its applications. Polysilicon is usually deposited at temperatures around 600°C [35], and further annealing for controlling the stress, grain size or dopant activation requires even higher temperatures. Such thermal processes cannot be performed on all substrates, especially on ones with active devices. Because of the high thermal budget as well as other practical constraints [36], polysilicon based micromachining is not a post-CMOS compatible process and new materials have to be explored for low temperature micromachining on such substrates. On the other hand, thin metal films can be sputterdeposited at room temperature; they are attractive materials for micromachining and potential substitute for polysilicon. However, thin films prepared by physical vapour deposition are usually polycrystalline, and they often develop large residual stresses that can have a strong effect on film properties and functional performances [37]. These films experience large stress variations within the substrate plane (biaxial), and across their thickness. It is generally believed that columnar crystallite formation in the film's microstructure causes this anisotropy [37]. These films are not completely amorphous, and they are distinguished by their unique morphology and long-range atomic order in their structure. The microcrystalline structure and morphology of these films are a strong function of the sputtering parameters and geometry.

To successfully fabricate an out-of-plane sensor plate, to make a thermal accelerometer for instance, controlling the stress of the structural layer is as important as controlling the structural layer's stress anisotropy. The stress mismatch between the electrical layers that are deposited on top of the structural layer could significantly deform the sensor plate, if the structural layer stress is not controlled. By controlling the net (overall) stress level of the structural layer the mechanical effect of the electrical layers on the sensor plate could be minimized.

The overall stress level of the structural layer could be controlled by using a symmetrical tri-layer structure [38]. Two different materials with opposite intrinsic stress polarity (tensile and compressive) are used to form the structure. The structural layer is formed by sandwiching a layer of the first material between two symmetrical layers of the second material. The symmetry in the structure prevents the structural deformation due to stress mismatch, and the overall stress level of the layers is controlled by the thickness and the stress level of the each layer. The overall stress level of a tri-layer film is given by [38],

$$\sigma = \frac{2d_1\sigma_1 + d_2\sigma_2}{2d_1 + d_2} \tag{3-1}$$

where  $d_1, d_2, \sigma_1$ , and  $\sigma_2$  are the thickness and intrinsic mechanical stress of the two outer and the sandwiched layers respectively.

Elemental metal and alloy thin films usually develop tensile intrinsic stress when they are sputter deposited, and their stress level is a function of the film material and the deposition parameters [37]. To fabricate a composite layer with controlled net stress level, these films can be encapsulated by two layers of a dielectric film, which usually have compressive intrinsic stress level. PECVD deposited dielectric films (silicon dioxide, silicon nitride) are completely amorphous materials with zero stress gradient across their thickness that makes them perfect choices for the fabrication of composite structures. Unfortunately, sputter deposited metal films have substantial stress gradient across their thickness that could cause major deformation in these composite structures. Figure 9 shows drastically deformed array of cantilevers fabricated out of sputter-deposited Nichrome after being released from substrate. The released cantilevers have

curled up severely due the non-uniform stress across the film thickness (perpendicular to substrate plane).

Figure 9: Effect of stress anisotropy across the thickness of a sputter-deposited Nichrome film.

To fabricate a flat out-of-plane sensor plate we use a composite structural layer consisting of two layers of PECVD silicon dioxide on top and bottom of a layer of a Nichrome film. We developed a novel technique to compensate for the stress anisotropy across the thickness of sputter-deposited metal films (Nichrome) which guarantees that the tri-layer structure remains flat when it is released from the substrate. The technique that we introduce in this chapter balances the stress variation across the thickness of the sputtered metal films by controlling the charged particles that bombard the film during the deposition process. By controlling the flux and energy of the bombarding ions during the film growth, stress level and stress polarity of the film can be modified. Ion flux and energy can be easily controlled by changing the substrate bias voltage. In a film with a net tensile stress, the forced exerted by the stress gradient across the film thickness can be compensated by changing the stress level of a very thin layer of the film to compressive. The moment caused by this stress mismatch prevents the freestanding structures from bending upwards due to the stress anisotropy.

# 3.1. Related compensation techniques

Magnetron-sputtered metal films that are deposited with dynamic deposition geometry (i.e., a moving substrate) were shown to develop in-plane crystallographic textures, elongated grain structures, and anisotropic residual stresses [37]. In order to obtain a homogenous thickness distribution, it is very common that the substrate is moved with respect to the sputtering source during deposition. During film deposition, the crystallites have the tendency to grow in the direction of in incoming atoms (atom flux) [39]. The periodic motion of the substrate leads to a periodical change of the deposition angle and growth direction of the crystallites. In this case, the anisotropic growth of the crystallites leads also to anisotropic film properties (e.g. magnetic properties), and in particular anisotropic intrinsic stress. However, films deposited in a static geometry generally develop isotropic in-plane residual stress (bi-axially balanced). Regardless of the deposition geometry, these films experience a large stress gradient across their thickness.

Many techniques have been developed to overcome the stress anisotropy of the sputtered metal films. Some of these methods were able to only reduce the film in-plane stress gradient, without eliminating the gradient across the film thickness. The inhomogeneous nature of the deposited film's microcrystalline structure is believed to be the main cause of this anisotropy. H. Kattelus *et al.* [36] tried to remove the long-range atomic order in the deposited films and to improve the film's microcrystalline uniformity by reactive sputtering. They have tried to deposit a completely amorphous film by introducing nitrogen in the film composition through reactive sputtering. They were highly successful with eliminating the lateral stress variation in the film, but the vertical gradient remained unchanged.

F. Hubenthal *et al.* [39] managed to control the in-plane stress anisotropy of a sputter deposited TiN film by controlling the period of a linearly moving substrate (with respect to the sputtering source). They characterized the film structure by the undulation period,  $\lambda = t/n$ , where t is the total thickness of the film and n is the number of the cycles. They noticed a distinct microstructure with a preferential growth direction, combined with high in-plane stress anisotropy for large undulation periods, whereas an almost isotropic structure with a poor crystalline order and almost isotropic biaxial

stresses for small undulation periods. Nevertheless, they observed strong stress anisotropy across the film thickness regardless of the undulation period.